*************

课 程 设 计 报 告

课程设计名称:计算机组成原理课程设计

课程设计题目:阵列除法器的设计

院(系):*************

专 业:*************

班 级:*************

学 号:*************

姓 名:*************

指导教师:*************

完成日期:*************

*************课程设计报告

目 录

第1章 总体设计方案......................................................................................................1

1.1 设计原理 1

1.2 设计思路 2

1.3 设计环境 3

第2章 详细设计方案......................................................................................................6

2.1 顶层方案图的设计与实现 6

2.1.1创建顶层图形设计文件...................................................................................6

2.1.2器件的选择与引脚锁定...................................................................................7

2.1.3编译、综合、适配...........................................................................................8

2.2 功能模块的设计与实现 8

2.3 仿真调试 10

第3章 编程下载与硬件测试........................................................................................12

3.1 编程下载 12

3.2 硬件测试及结果分析 12

参考文献........................................................................................................................14

附录(电路原理图)....................................................................................................15

-I-

*************课程设计报告

第1章 总体设计方案

1.1 设计原理

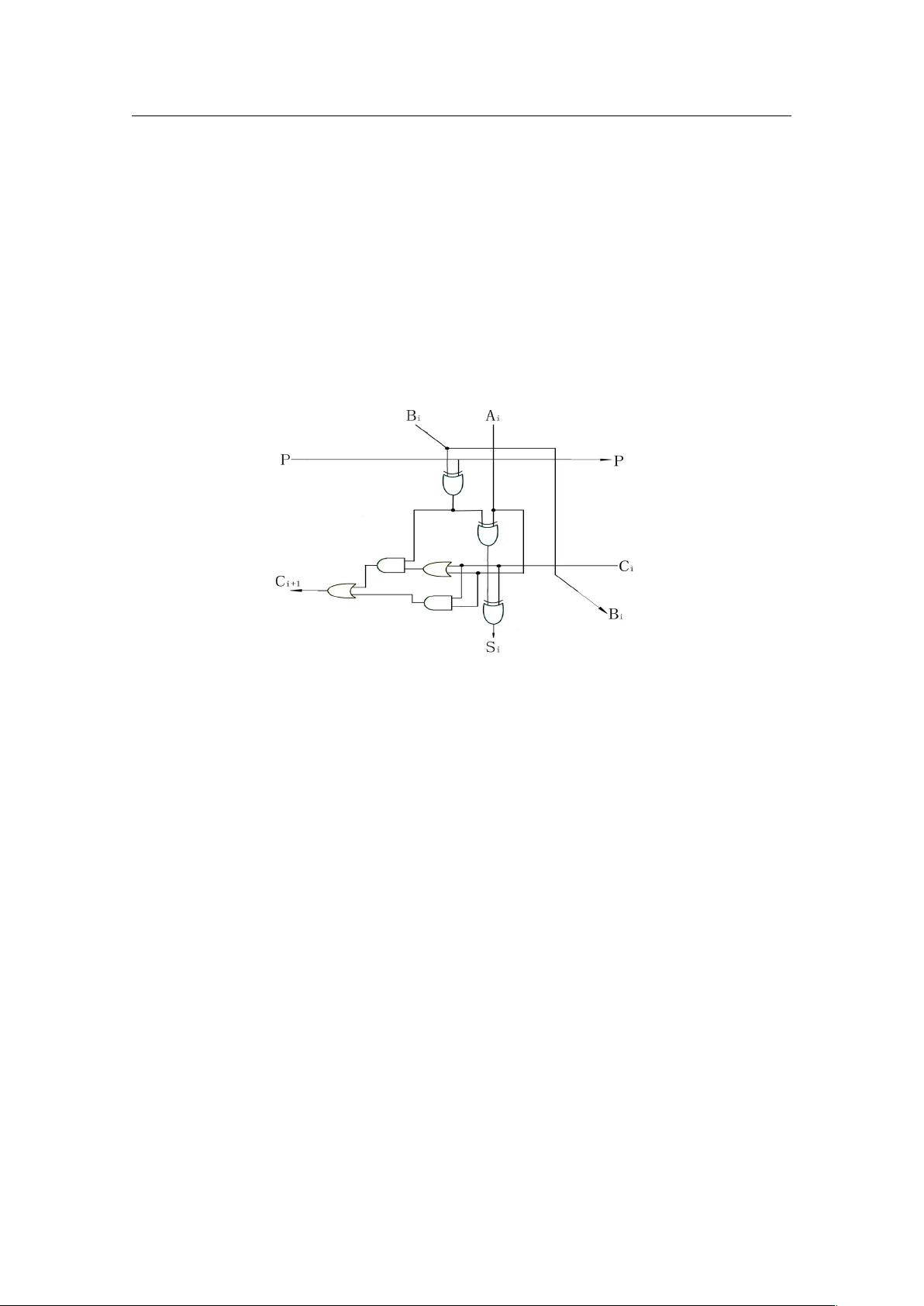

阵列除法器的功能是利用一个可控加法/减法(CAS)单元所组成的流水阵列来

实现的。它有四个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当

P=1时,CAS作减法运算。可控加法/减法(CAS)单元的逻辑电路图如图1.1所示。

图1.1 可控加法/减法(CAS)单元的逻辑图

CAS单元的输入与输出关系可用如下一组逻辑方程来表示:

S

i

=A

i

⊕ (B

i

⊕ P) ⨁ C

C

i

+

1

=(A

i

+C

i

) ∙ (B

i

⊕ P)+A

i

C

i

当P=0时,就得到我们熟悉的一位全加器(FA)的公式:

S

i

=A

i

⊕ B

i

⊕ C

i

C

i

+

1

=A

i

B

i

+B

i

C

i

+A

i

C

i

当P=1时,则得求差公式:

S

i

=A

i

⨁ B

i

'⨁ C

i

C

i

+

1

=A

i

B

i

'+B

i

'C

i

+A

i

C

i

其中B

i

'=B

i

⨁ 1。

在减法情况下,输入C

i

称为借位输入,而C

i

+

1

称为借位输出。

不恢复余数的除法也称加减交替法。在不恢复余数的除法阵列中,每一行所执

-1-

*************课程设计报告

行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否一致

当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位

“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变

它的符号时,即产生商位“1”,下一行的操作应该是减法。

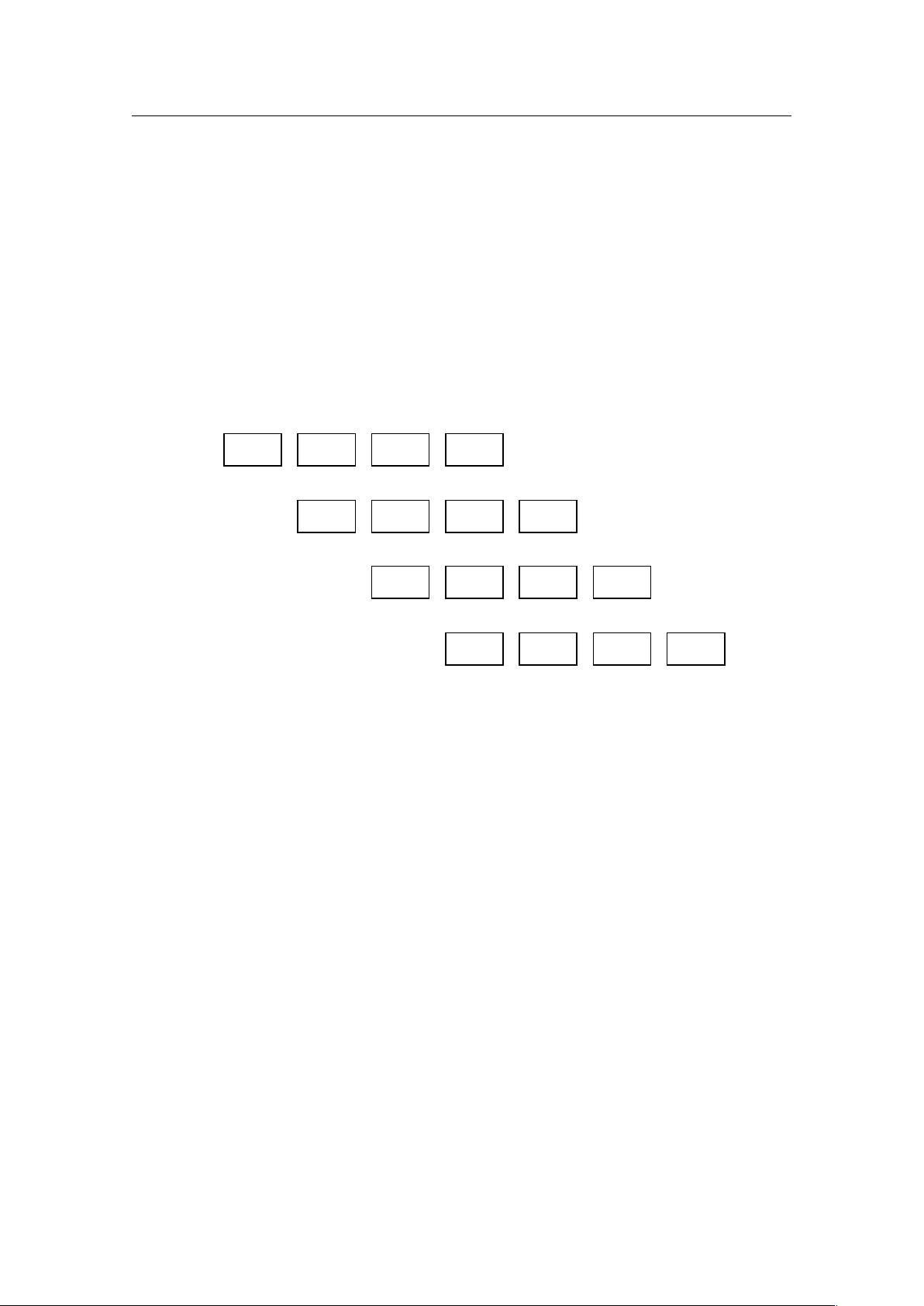

本实验就采用加减交替的方法设计阵列除法器。图1.2所示的就是4位除4位不

恢复余数阵列除法器的逻辑原理图。

图1.2 4位除4位阵列除法器

1.2 设计思路

不恢复余数阵列除法器是用一个可控加法/减法(CAS)单元所组成的流水阵列来

实现的。

由图1.2可知,被除数x=0.x

6

x

5

x

4

x

3

x

2

x

1

,它是由顶部一行和最右边的对角线上的

垂直输入线来提供的。

除数y=0.y

3

y

2

y

1

,它沿对角线方向进入这个阵列。这是因为,在除法中将所需

要的部分余数保持固定,而将除数沿对角线右移。

商q=0.q

3

q

2

q

1

,它在阵列的左边产生。

余数r=0.00r

6

r

5

r

4

r

3

,它在阵列的最下一行产生。

最上面一行所执行的初始操作一定是减法。因此最上面一行的控制性P固定置

成“1”。减法是用2的补码运算来实现的,这时右端各CAS单元上的反馈线用作初始

的进位输入,即最低位加“1”。每一行最左边的单元的进位输出决定着商的数值。

q

4=

0

0 0

y

3

y

2

y

1

x

6

x

5

x

4

CAS CAS CAS CAS

CAS CAS CAS CAS

CAS CAS CAS CAS

CAS CAS CAS CAS

x

3

x

2

x

1

r

3

r

4

r

5

r

6

1

q

3

q

2

q

1

-2-