没有合适的资源?快使用搜索试试~ 我知道了~

计算机组成原理课程设计阵列除法器的设计

温馨提示

试读

23页

阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等本实验设计的是加减交替阵列除法器。

资源推荐

资源详情

资源评论

Xxxxxxxxx

课 程 设 计 报 告

课程设计名称:计算机组成原理课程设计

课程设计题目:阵列除法器的设计

院(系):xxxxxxxxx

专 业:xxxxxxxxx

班 级:xxxxxxxxx

学 号:xxxxxxxxxxx

姓 名:xxxxxxxxxxxxx

指导教师:xxxxxxxxxxxx

完成日期:xxxxxxxxxxxxxxx

沈阳航空工业学院课程设计报告

目 录

第1章 总体设计方案......................................................................................................1

1.1 设计原理................................................................................................................1

1.2 设计思路................................................................................................................3

1.3 设计环境................................................................................................................4

第2章 详细设计方案......................................................................................................7

2.1 顶层方案图的设计与实现....................................................................................7

2.1.1创建顶层图形设计文件...................................................................................7

2.1.2器件的选择与引脚锁定...................................................................................8

2.1.3编译、综合、适配...........................................................................................9

2.2 功能模块的设计与实现........................................................................................9

2.3 仿真调试..............................................................................................................11

第3章 编程下载与硬件测试........................................................................................14

3.1 编程下载..............................................................................................................14

3.2 硬件测试及结果分析..........................................................................................14

参考文献........................................................................................................................16

附录(电路原理图)....................................................................................................17

-I-

沈阳航空工业学院课程设计报告

第1章 总体设计方案

1.1 设计原理

阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除

法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速

度。阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等本实

验设计的是加减交替阵列除法器。

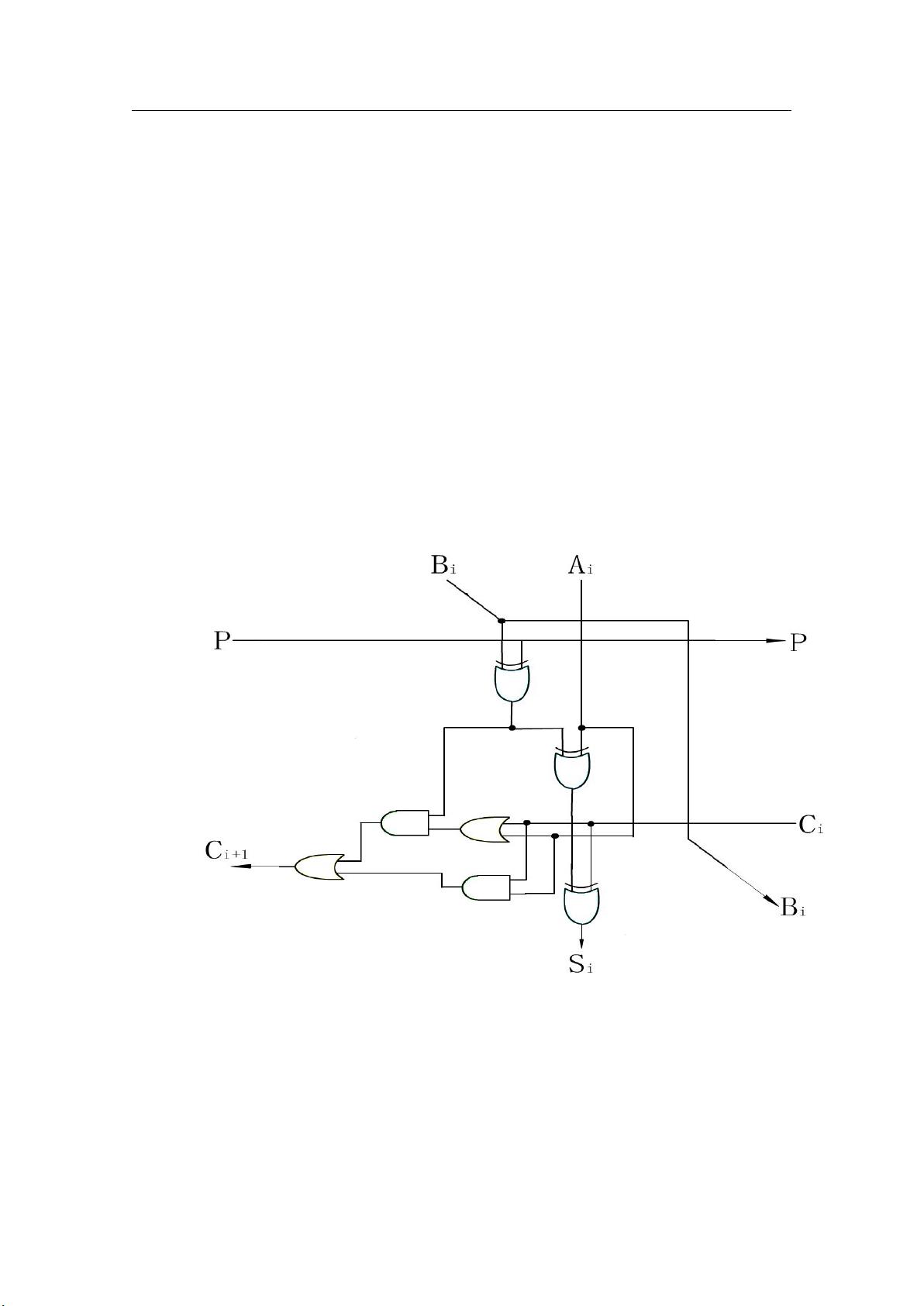

原理是利用一个可控加法/减法CAS单元所组成的流水阵列来实现的它有四

个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当P=1时,CAS作

减法运算。逻辑结构图如图1.1所示。

图1.1不恢复余数阵列除法器的逻辑结构图

CAS单元的输入与输出的关系可用如下一组逻辑方程来表示:

S

i

=A

i

⊕(B

i

⊕P)⊕C

C

i

+

1

=(A

i

+C

i

)·(B

i

⊕P)+A

i

C

i

当P=0时,就是一个全加器,如下式:

-1-

沈阳航空工业学院课程设计报告

S

i

=A

i

⊕B

i

⊕C

i

C

i

+

1

=A

i

B

i

+B

i

C

i

+A

i

C

i

当P=1时,则得求差公式:

S

i

=A

i

⊕B

i

⊕C

i

C

i

+

1

=A

i

B

i

+B

i

C

i

+A

i

C

i

其中B

i

=B

i

⊕1。

在减法情况下,输入C

i

称为借位输入,而C

i

+

1

称为借位输出。

不恢复余数的除法也就是加减交替法。在不恢复余数的除法阵列中,每一行所

执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否一

致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个

商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不

改变它的符号时,即产生商位“1”,下一行的操作应该是减法。

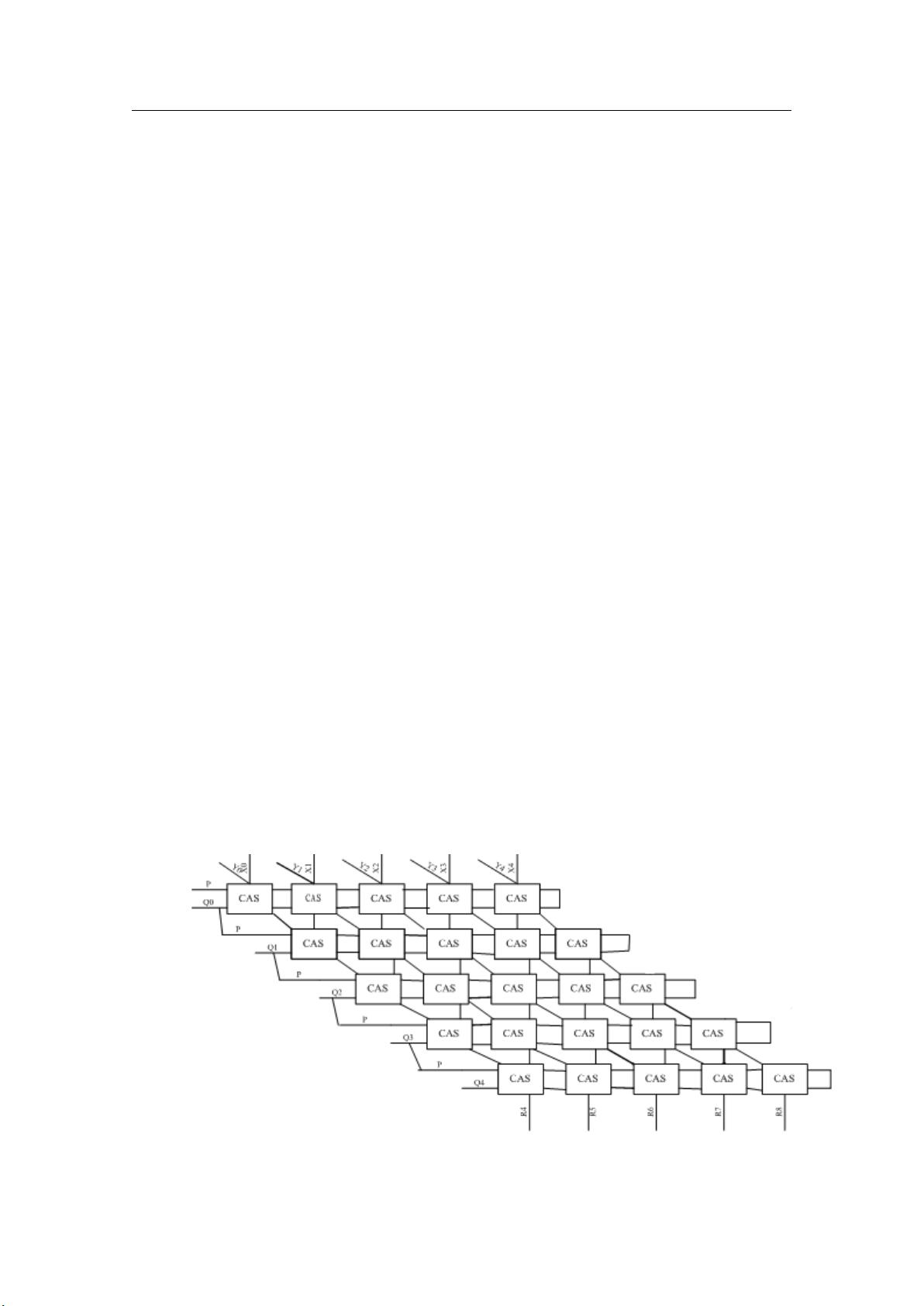

本实验就采用加减交替的方法设计这个阵列除法器。图1.2所示的就是一个阵

列除法器完成X/Y的除法运算,图中每一个方框是一个可控加法/减法(CAS)单元

被除数为X= X

0

X

1

X

2

X

3

X

4

;除数为Y= Y

0

Y

1

Y

2

Y

3

Y

4

。其中X

0

和Y

0

是被除数和除

数的符号位,在本次设计中X

0

和Y

0

为零,商的符号位恒为零,商为0.Q

1

Q

2

Q

3

Q

4

,

余数为0.000R

4

R

5

R

6

R

7

R

8

。被除数X是由顶部一行和最右边的对角线上的垂直输入

线来提供的,除数Y是沿对角线方向进入这个阵列。至于作加法还是减法,由控制

信号P决定,即当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算

其原理框图如图1.2所示。

-2-

剩余22页未读,继续阅读

资源评论

yahoolovers2013-03-26有点难懂。。。

yahoolovers2013-03-26有点难懂。。。 wangpeng1991972011-09-19是硬件实现的东西,对我是没用,~~~~(>_<)~~~~

wangpeng1991972011-09-19是硬件实现的东西,对我是没用,~~~~(>_<)~~~~ conebbb2013-06-03很难,所以上来找代码了,其实也没看懂,不过挺不错的~

conebbb2013-06-03很难,所以上来找代码了,其实也没看懂,不过挺不错的~

damoyiweidujiang

- 粉丝: 2

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功