没有合适的资源?快使用搜索试试~ 我知道了~

IC设计后端流程初学必看.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

温馨提示

试读

36页

IC设计后端流程初学必看.pdf

资源推荐

资源详情

资源评论

基本后端流程(漂流 & 雪拧)

----- 2010/7/3---2010/7/8

本教程将通过一个 8*8 的乘法器来进行一个从 verilog 代码到版图的整个流程(当然只是基

本流程,因为真正一个大型的设计不是那么简单就完成的) ,此教程的目的就是为了让大家

尽快了解数字 IC 设计的大概流程,为以后学习建立一个基础。此教程只是本人探索实验的

结果, 并不代表内容都是正确的, 只是为了说明大概的流程, 里面一定还有很多未完善并且

有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括以下内容:

1. 逻辑综合(逻辑综合是干吗的就不用解释了把?)

2. 设计的形式验证(工具 formality )

形式验证就是功能验证, 主要验证流程中的各个阶段的代码功能是否一致, 包括综合前 RTL

代码和综合后网表的验证,因为如今 IC 设计的规模越来越大,如果对门级网表进行动态仿

真的话,会花费较长的时间(规模大的话甚至要数星期) ,这对于一个对时间要求严格 (设

计周期短) 的 asic 设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验

证。另外, 因为版图后做了时钟树综合, 时钟树的插入意味着进入布图工具的原来的网表已

经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3. 静态时序分析( STA),某种程度上来说, STA 是 ASIC 设计中最重要的步骤,使用

primetime 对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重

新进行综合。 (PR 后也需作 signoff 的时序分析)

4. 使用 cadence 公司的 SOCencounter 对综合后的网表进行自动布局布线( APR)

5. 自动布局以后得到具体的延时信息( sdf 文件,由 寄生 RC 和互联 RC 所组成)反标注到

网表 ,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布

局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违

规,则进入下一步。

6. APR 后的门级功能仿真(如果需要)

7. 进行 DRC 和 LVS,如果通过,则进入下一步。

8. 用 abstract 对此 8*8 乘法器进行抽取,产生一个 lef 文件,相当于一个 hard macro。

9. 将此 macro 作为一个模块在另外一个 top 设计中进行调用。

10. 设计一个新的 ASIC, 第二次设计,我们需要添加 PAD ,因为没有 PAD ,就不是一个 完整

的芯片,具体操作下面会说。

11. 重复第 4 到 7 步

1. 逻辑综合

1) 设计的 8*8verilog 代码如下

module mux (clk,clr,data1,data2,dataout);

input clk,clr;

input [7:0] data1,data2;

output reg [15:0] dataout;

always @(posedge clk)

begin

if(!clr)

begin

dataout<=0;

end

else

begin

dataout<=data1*data2;

end

end

endmodule

2) 综合之前,我们要选取库,写好约束条件,修改 dc 的启动文件 synopsys_dc.setup,目标

库选择 TSMC (此设计都是用 TSMC18 的库)的 typical.db 。 (选择 max 库会比较好 )

Dc 的命令众多,但是最基本的命令差不多,此设计的约束文件命令如下:

create_clock -period 10 [get_ports clk] //用于时钟的创建

set_clock_latency -source -max 0.2 [get_ports clk] // 外部时钟到 core 的 clk 连线延时

set_clock_latency -max 0.1 [get_ports clk] //core 的 clk 到寄存器 clk 端的 net 连线延时

set_clock_uncertainty -setup 2 [get_ports clk] // 时钟延时的不确定性, 求 setup 违规时会被计算

进去

set_clock_uncertainty –hold 1 【all_clocks 】

set_input_delay -max 0.5 -clock clk [get_ports [list [remove_from_coll [all_inputs] clk] ] //

输入延时,外部信号到 input 端的连线延时

set_output_delay -max 0.5 -clock clk [all_outputs] // 输出延时

set_driving_cell -lib_cell INVX4 [all_inputs] // 输入端的驱动强度

set_load -pin_load 0.0659726 [all_outputs] // 输出端的驱动力

set_wire_load_model -name tsmc18_wl10 -library typical // 内部 net 的连线模型

set_wire_load_mode enclosed //定义建模连线负载相关模式

set_max_area 0

compile

report_timing

report_constraint

change_names -rule verilog –hier

set_fix_multiple_ports_net –all

write -format verilog -hier -output mux.sv // 输出网表,自动布局布线需要

write -format ddc -hier -output mux.ddc // 输出 ddc

write_sdf mux.sdf // 输出延时文件,静态时序分析时需要

write_sdc mux.sdc // 输出约束信息,自动布局布线需要

3) 逻辑综合

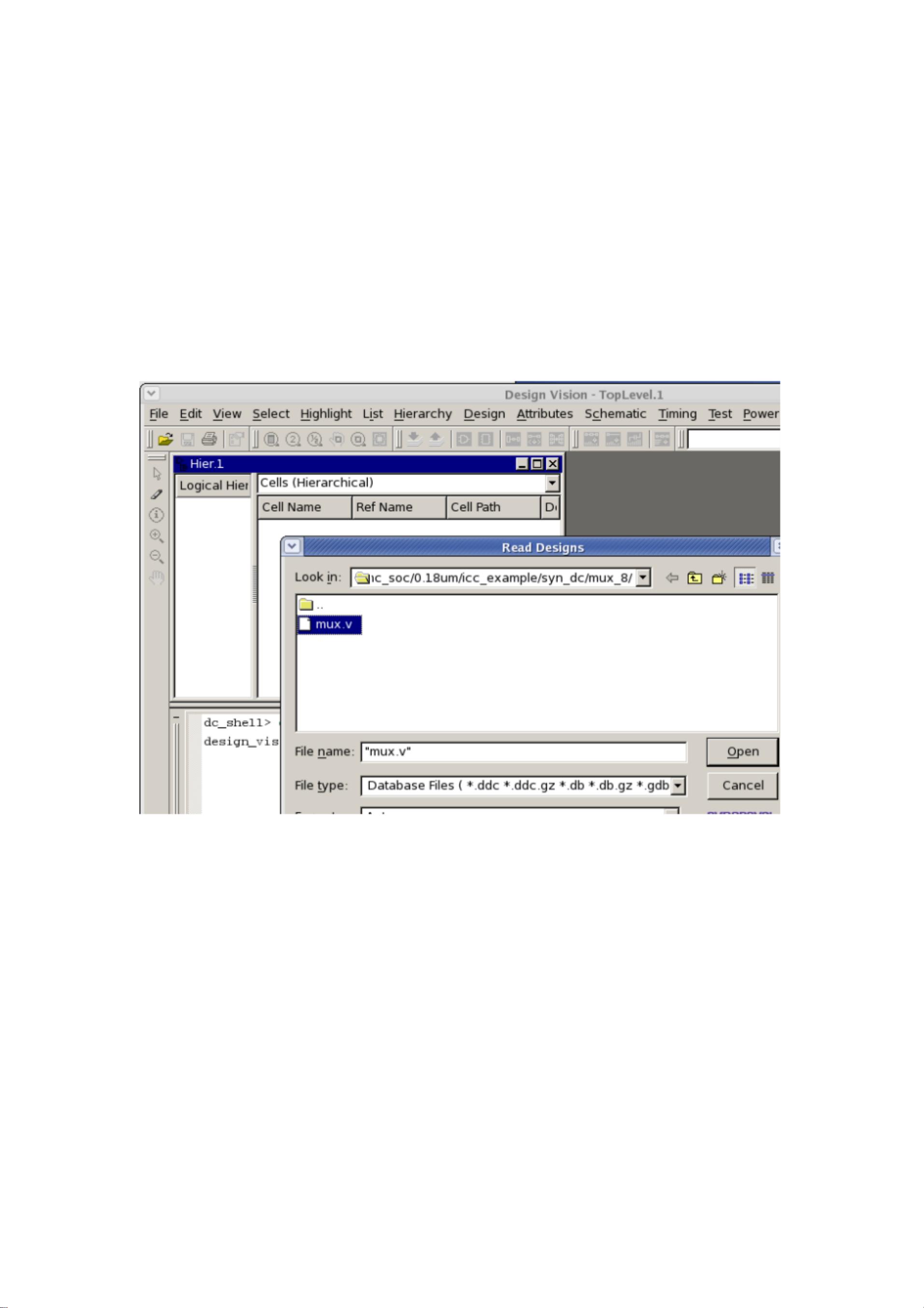

启动 design_vision 。Read->mux.v

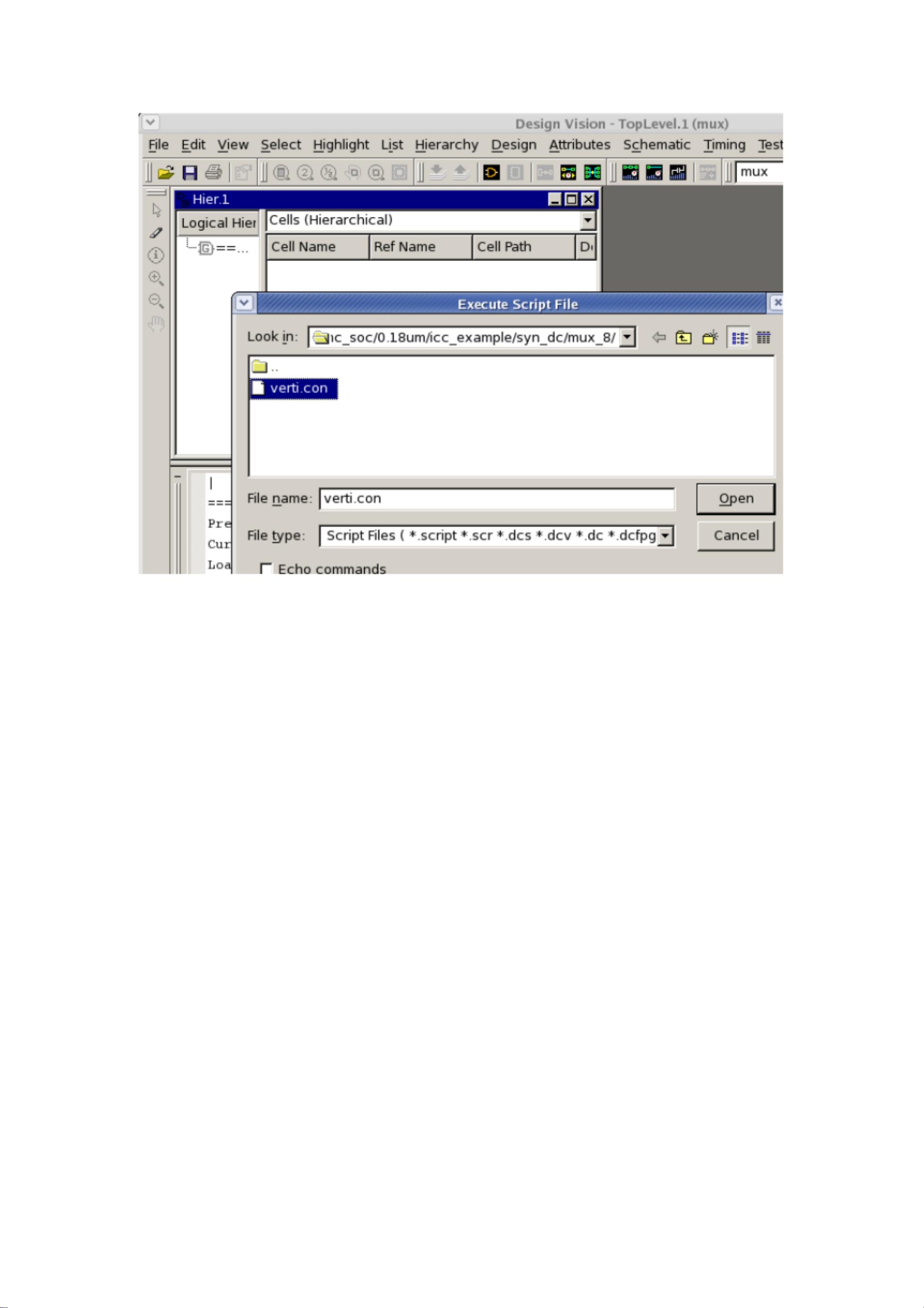

输入约束文件。 File->excute script->verti.con

之后会产生 mux.sv,mux.sdc,mux.sdf,mux.ddc 等文件

4) 时序分析

综合以后我们需要分析一下时序, 看时序是否符合我们的要求, 综合实际上是一个 setup

时间的满足过程,但是我们综合的时候,连线的负载只是库提供的(即上面的 wire_load ),

并不是实际的延时,所以一般做完综合以后,时间余量( slack)应该为时钟的 30%(经验

值),以便为后面实际布局布线留下充足的延时空间。因为如果 slack 太小,甚至接近于 0,

虽然我们看起来是没有时序违规的,但是实际布局以后,时序肯定无法满足。

使用 report_timing 命令,可以查看时序分析报告:

****************************************

Report : timing

-path full

-delay max

-max_paths 1

-sort_by group

Design : mux

Version: D-2010.03-SP1

Date : Fri Jul 2 12:29:44 2010

****************************************

Operating Conditions: typical Library: typical (模型库)

Wire Load Model Mode: enclosed

Startpoint: data2[4] (input port clocked by clk)

Endpoint: dataout_reg_15_

(rising edge-triggered flip-flop clocked by clk)

Path Group: clk

Path Type: max

Des/Clust/Port Wire Load Model Library

------------------------------------------------

mux tsmc18_wl10 typical (线载模型及库)

Point Incr Path

--------------------------------------------------------------------------

clock clk (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

input external delay 0.50 0.50 f

data2[4] (in) 0.01 0.51 f

mult_14/b[4] (mux_DW_mult_uns_0) 0.00 0.51 f

mult_14/U131/Y (INVX1) 0.54 1.05 r

mult_14/U161/Y (NOR2X1) 0.14 1.18 f

mult_14/U39/S (CMPR42X1) 0.68 1.87 f

mult_14/U12/CO (ADDFX2) 0.32 2.19 f

mult_14/U11/CO (ADDFX2) 0.23 2.42 f

mult_14/U10/CO (ADDFX2) 0.23 2.65 f

mult_14/U9/CO (ADDFX2) 0.23 2.88 f

mult_14/U8/CO (ADDFX2) 0.23 3.10 f

mult_14/U7/CO (ADDFX2) 0.23 3.33 f

mult_14/U6/CO (ADDFX2) 0.23 3.56 f

mult_14/U5/CO (ADDFX2) 0.23 3.79 f

mult_14/U4/CO (ADDFX2) 0.23 4.02 f

mult_14/U3/CO (ADDFX2) 0.23 4.25 f

mult_14/U2/CO (ADDFX2) 0.22 4.47 f

mult_14/product[15] (mux_DW_mult_uns_0) 0.00 4.47 f

dataout_reg_15_/RN (DFFTRXL) 0.00 4.47 f

data arrival time 4.47

clock clk (rise edge) 10.00 10.00

clock network delay (ideal) 0.30 10.30

clock uncertainty -0.10 10.20

dataout_reg_15_/CK (DFFTRXL) 0.00 10.20 r

library setup time -0.19 10.01

data required time 10.01

--------------------------------------------------------------------------

data required time 10.01

data arrival time -4.47

剩余35页未读,继续阅读

资源评论

m0_721603992024-02-28资源值得借鉴的内容很多,那就浅学一下吧,值得下载!

m0_721603992024-02-28资源值得借鉴的内容很多,那就浅学一下吧,值得下载!

ll17770603473

- 粉丝: 0

- 资源: 6万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- XILINXFPGA源码Xilinxspratan3xcs100E(VGAPS2)

- XILINXFPGA源码XilinxSPARTAN-3E入门开发板实例

- XILINXFPGA源码XilinxSdramVerilog和VHDL版本文档

- 物联网智能家居方案-基于Nucleo-STM32L073&机智云(大赛作品,文档齐全,可直接运行)(文档加Matlab源码)

- XILINXFPGA源码XilinxISE9.xFPGACPLD设计源码

- 成都市地图含高新区(高新南区,高新西区),天府新区,东部新区虚拟行政区划

- XILINXFPGA源码XilinxEDK设计试验

- XILINXFPGA源码XilinxEDKMicroBlaze内置USB固件程序

- 基于 django 的视频点播后台管理系统源代码+数据库

- 基于Java的网上医院预约挂号系统的设计与实现(部署视频)-kaic.mp4

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功