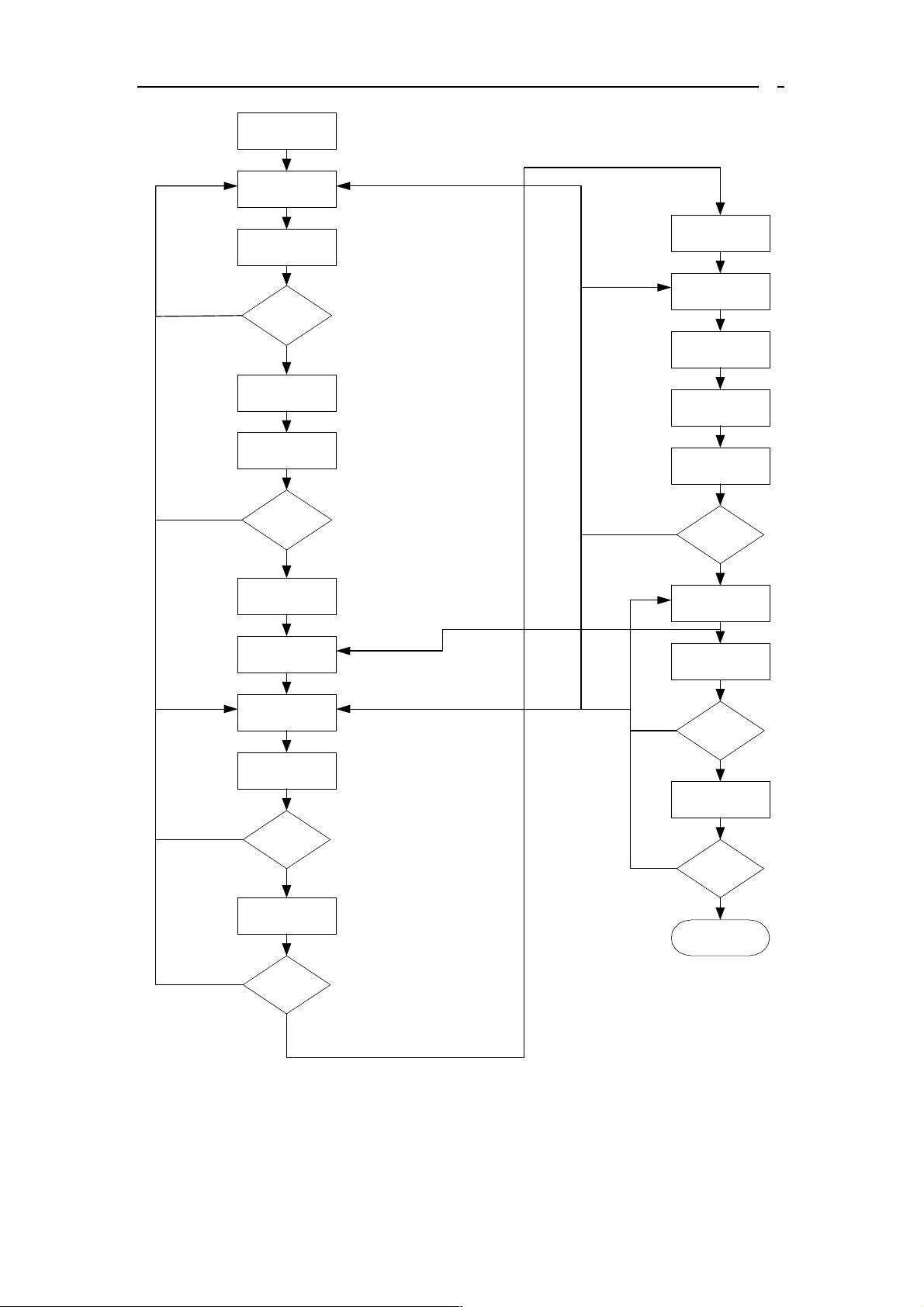

### ASIC设计流程详解 #### 一、引言 随着半导体技术的进步,集成电路设计进入了深亚微米时代。在这个阶段,单个芯片上的晶体管数量急剧增加,使得传统的全定制手工设计方法几乎不再适用。为了应对日益增大的设计复杂度以及缩短产品上市时间(time-to-market)的需求,新的设计方法学和工具应运而生。本文将详细介绍基于标准单元库的深亚微米数字集成电路自动化设计流程,涵盖从行为级描述到最终版图后仿真的各个环节。 #### 二、设计流程概述 ##### 1. 行为级描述 设计流程始于行为级或寄存器传输级(RTL)的描述,通常采用硬件描述语言(HDL)如VHDL或Verilog进行编写。这一阶段的目标是对系统的功能行为进行抽象描述。 ##### 2. 系统行为级仿真 在此阶段,使用仿真工具如Synopsys公司的VSS (VHDL System Simulator)对设计的行为级描述进行功能验证,确保其逻辑正确无误。 ##### 3. 设计综合 通过综合工具(例如Synopsys Design Compiler)将行为级或RTL级的HDL代码转换成门级网表,同时考虑各种约束条件如时序、面积等。 ##### 4. 综合后仿真 综合完成后,需要再次进行仿真验证以确保转换后的门级网表与原始HDL代码的功能一致。这一步骤同样使用VSS等仿真工具。 ##### 5. 自动化布局布线 自动化布局布线(Auto Place and Route, APR)是将门级网表映射到物理芯片布局的过程。通常使用Cadence Silicon Ensemble等工具完成这一过程,旨在优化芯片的面积、功耗和性能。 ##### 6. 版图后仿真 完成布局布线后,需要进行版图后仿真(Post-layout Simulation),以验证最终的物理设计是否符合功能要求。由于某些文件格式的限制,可能会使用其他工具如Active-HDL进行验证。 #### 三、关键技术工具及其应用 1. **仿真工具**: - **VSS (VHDL System Simulator)**:用于行为级和综合后仿真。 - **Active-HDL**:用于版图后仿真。 - 这些工具可以帮助设计者检测和修复设计中的错误,提高设计质量。 2. **综合工具**: - **Synopsys Design Compiler**:将HDL代码转换成门级网表。 - 设计综合过程中会考虑到多种约束条件,如时钟周期、功耗等,以优化设计。 3. **自动化布局布线工具**: - **Cadence Silicon Ensemble**:提供高效的自动化布局布线解决方案。 - 该工具能够优化芯片的布局,减少信号间的干扰,提高整体性能。 4. **Formal Verification**: - 作为一种静态验证技术,Formal Verification可以更全面地验证电路的功能正确性,避免了动态仿真的局限性。 5. **Clock Tree Synthesis**: - 在自动化布局布线阶段,Clock Tree Synthesis技术用于生成均衡的时钟网络,以保证所有时钟信号的到达时间一致,从而提高设计的整体性能。 #### 四、设计流程的关键步骤解析 1. **行为级仿真**: - 目标是验证设计的行为正确性,确保功能逻辑正确。 - 使用VSS等工具进行仿真。 2. **设计综合**: - 将行为级或RTL级的HDL代码转换为门级网表。 - 考虑时序、面积等约束条件。 3. **综合后仿真**: - 验证门级网表与HDL代码的一致性。 - 使用VSS进行功能验证。 4. **自动化布局布线**: - 通过Cadence Silicon Ensemble等工具完成布局布线。 - 优化芯片面积、功耗和性能。 5. **版图后仿真**: - 最终验证物理设计的正确性。 - 可能使用Active-HDL或其他工具进行。 #### 五、结论 基于标准单元库的深亚微米数字集成电路设计流程涉及多个关键步骤,包括行为级描述、系统行为级仿真、设计综合、综合后仿真、自动化布局布线和版图后仿真。通过采用先进的EDA工具和技术,如Synopsys Design Compiler、Cadence Silicon Ensemble等,可以极大地提高设计效率和质量,缩短产品上市时间,满足市场对高性能集成电路的迫切需求。

剩余66页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 电子商务_网上商城管理系统_用户身份验证_便捷购物_1740825436.zip

- 商城管理_System_SCUM_1740825333.zip

- 智能公交系统电子站牌设计_STM32_微信小程序_毕业设_1740825532.zip

- 全国地图 省GeoJson 市GeoJson

- MATLAB实现领航追随法与人工势场法融合的车辆编队避障控制策略,MATLAB领航追随法融合人工势场法的车辆编队避障控制策略实现研究,MATLAB基于领航追随法的车辆编队控制,领航追随者与人工势场法的

- 迪恩在线教育素材培训课程网站源码 discuz内核完整资料带数据

- 基于手性光学效应的连续介质束缚态研究:从三维图谱到Q因子图的所见即所得超表面复现分析,基于Comsol模拟:三次谐波效应下的本征手性BIC超表面研究-远场偏振图、手性透射曲线与光学响应的可见性分析

- 和材料性能分析** COMSOL 培训视频,深入解析多物理场仿真技术与应用 **深入解析COMSOL多物理场仿真技术与应用:从结构力学到化学反应的全面分析**,界面仿真和流控模拟 COMSO

- 找高手:应该如何训练工程造价的大模型?

- NOIP2009年提高组NOI Linux和Cena测评环境与数据

- 手把手项目实践:用Labview制作一个电子秤的485上位程序

- golang画图库演示程序源码

- IntelCacheAccelerationSoftware,傲腾加速软件

- 昆仑通态MCGS与欧姆龙E5CC温控器通讯:PID控制及输出启停功能实现,欧姆龙E5CC温控器与昆仑通态MCGS的PID通讯方式及输出启停(KUNL-1),昆仑通态MCGS与欧姆龙E5CC温控器通讯+

- 补码计算与进制转码学习

- 《从0到1:手把手教你OpenCV下载安装秘籍》

信息提交成功

信息提交成功