DSP systems– interfacing

with the outside world

4

CHAPTER

In this chapter many issues related to DSP peripheral components will be consid-

ered. This will include a consideration of both on- and off-chip components and

their operation. Many ideas presented in Chapter 3 such as the use of efficient

pipelines, fast data manipulation and arithmetic operations all rely on the ability of a

DSP device to move large amounts of data quickly and seamlessly into and out of

the DSPs processing core. To facilitate this effective movement and storage of data,

most DSPs incorporate a wide range of peripheral management facilities and these

will be considered here. As with Chapter 3, a hypothetical DSP device will be intro-

duced which incorporates a generic set of typical features. The hypothetical device

will be used as the basis for discussions and then related to real life examples, again

taken mainly from the Texas Instruments range of DSP devices.

4.1 DSP devices – beyond

the core 00

4.2 Hardware interfacing and

I/O control 00

4.3 System management and

control 00

4.4 All the analog bits and pieces

(i.e. ADC, DAC, anti-aliasing,

over-sampling, etc) 00

4.5 Getting signals in 00

4.6 Getting signals out 00

4.7 Getting signals in and out 00

4.8 Digital up- and

down-conversion 00

4.9 Interfacing with the real

world 00

4.10 Questions 00

4.11 References 00

In Chapter 3 many issues related to the operation and use of the central code of the DSP

processor were introduced. In particular the operation of the ALU, hardware multiplier,

various registers, control registers and the accumulator were all considered. In this section

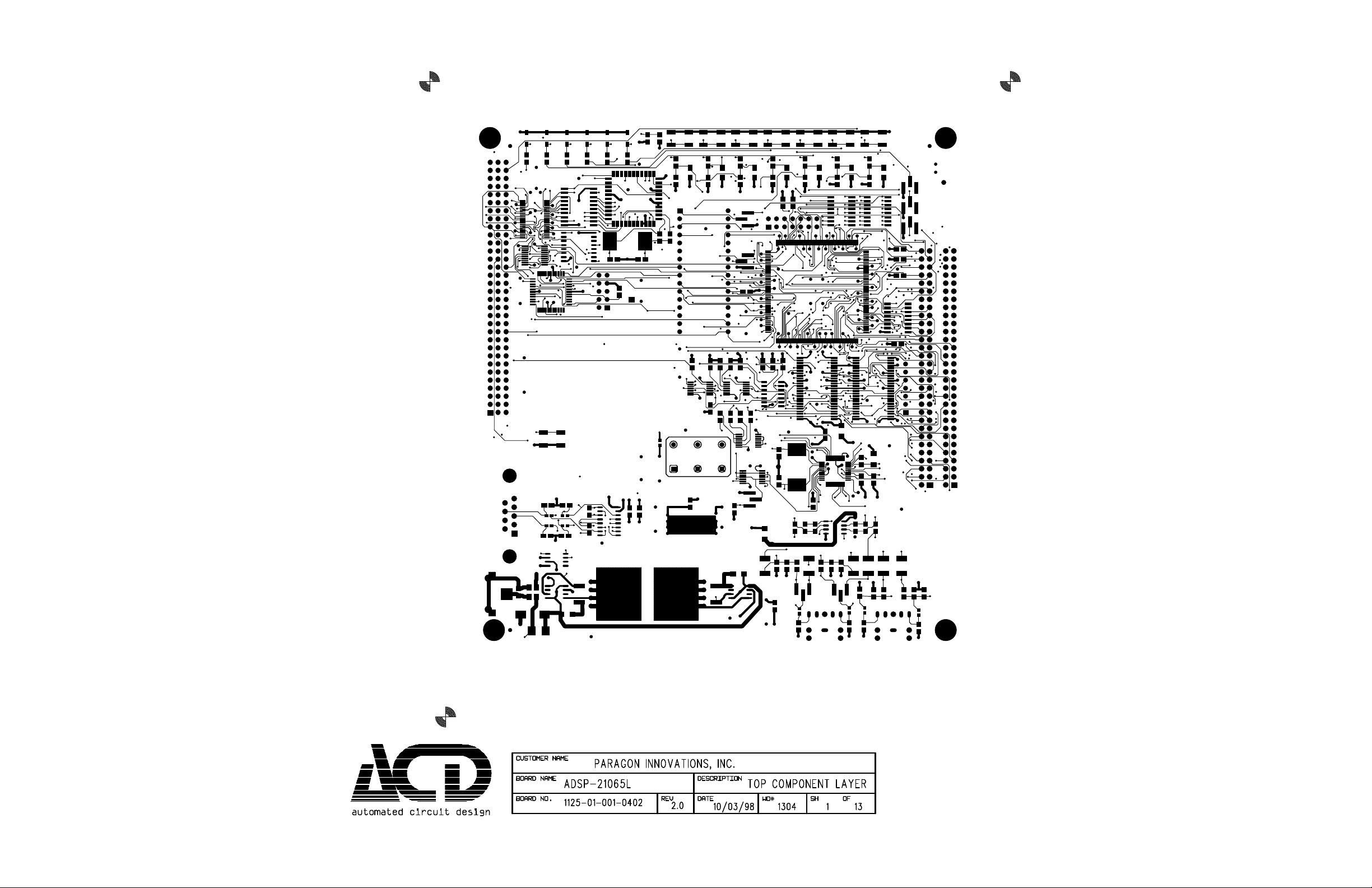

we move on to consider the other facilities typically found on a DSP device. Figure 4.1

shows the hypothetical DSP device introduced in the previous chapter. As already men-

tioned we will use this device again as the basis for our discussion and as with Chapter 3

we will relate the generic DSP features presented in the hypothetical device with examples

taken from real devices.

In Figure 4.1, the central core is shown at the center of the DSP device. In this section

we will consider the components arranged outside the core but still inside the DSP device

itself. Most of these components are able to run in parallel with the DSP core, taking little

of the core’s available instruction cycle time. A good example of this is the on-chip timer

which can be initialized to interrupt the DSP device at a regular rate, e.g. every 1 ms. If the

timer was not available this task would be carried out using a software routine which

would directly impact on the core itself. By delegating tasks to on-chip components, the

processing core can be freed up to handle the more demanding arithmetic requirements

of the algorithm. Of course at start-up, when the DSP is reset, all of the peripheral com-

ponents must be initialized and set to a known state. This has already been considered a

little in Section 2.2.1, although initialization issues will also be considered further here.

We start by looking at each of the components shown in Figure 4.1, as follows.

4.1 DSP devices – beyond the core

208 Chapter 4 ❚ DSP systems – interfacing with the outside world

External

memory

interface

Data

memory

Program

memory

General

purpose

I/O

interface

DMA

processor

Interrupt

control

unit

Data bus

Program bus

Instruction

cache

Timer

(0)

Timer

(1)

Address

generation

unit (0)

Address

generation

unit (0)

DSP

central

core

Multi-channel

serial port (0)

Clock

(PLL)

Multi-channel

serial port (1)

Wait state

generator

Host port

interface

Power

management

Test and emulation

logic (JTAG)

Register file

Figure 4.1

Hypothetical DSP

device

The idea of the Harvard architecture used within most DSP devices has already been

introduced in Chapter 3. Harvard architectures, as already mentioned, make use of sepa-

rate program and data storage areas that can be simultaneously accessed. This makes

many processing operations far more efficient than would be possible on a traditional Von

Neumann architecture. The program and data storage areas may be constructed using a

range of different memory types as appropriate for any given application. Most DSPs are

provided with a limited amount of on-chip memory which can be accessed at full speed;

also this is usually divided into program and data areas which can truly be accessed simul-

taneously. If extra memory space is required for a particular application, then this can be

added via an external memory interface which provides data, address and control buses to

the outside world. One of the problems with interfaces to external memory is that the on-

chip dual bus architecture is rarely replicated to the outside world and so simultaneous

access to external memory are not possible. For this reason, high-speed processing opera-

tions, using simultaneous accesses to memory, usually requires that data and program

instructions reside on-chip (Ref. 4.1).

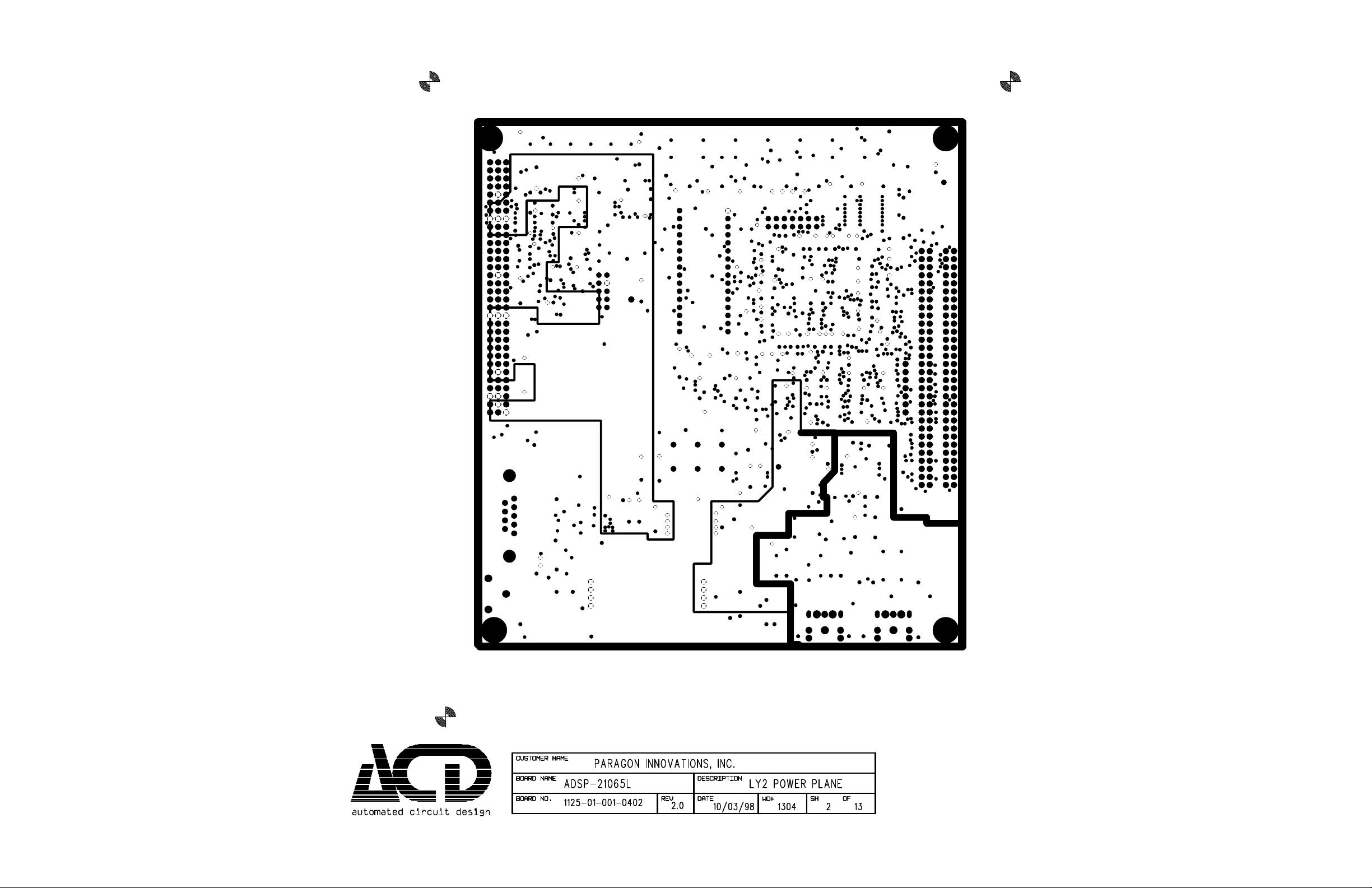

It is common practice to represent the addressable memory or I/O space of a DSP

device using a memory map. The memory map of a TMS320C54x DSP device is shown in

Figure 4.2. In fact, this is the memory map of a C548 DSP device which is one of a

number of different devices within the C54x family. The memory map of Figure 4.2,

which is quite typical of many DSP devices, shows the two identifiable areas of program

and data memory. This is further subdivided into areas of internal and external memory

space. The memory space defined for this device is actually organized into three individu-

ally selectable spaces labelled as program, data, and I/O space.

The memory map of the C548 DSP shown in Figure 4.2 can be set to one of a number

of different configurations according to settings given in the Processor Mode Status

Register, PMST, associated with this device. The operation of the PMST register is dis-

cussed in Section 3.7.5. In summary, two register flags are important for memory

configuration on the C54x devices, the OVLY flag and the MP/MC flag. The OVLY flag is

used to enable or disable the mapping of data memory into program memory space and

the MP/MC flag is used to enable or disable the on-chip ROM and hence determines the

boot mode of the device.

Most DSP devices are provided with a limited amount of on-chip read-only memory,

ROM, and random access memory, RAM, and the C54x is no exception to this. All C54x

devices contain both RAM and ROM. Among the different C54x devices, two types of RAM

are represented: dual-access RAM, DARAM, and single-access RAM, SARAM. Table 4.1

shows the allocation of internal memory for each of the different devices in the C54x family.

On-chip ROM. The on-chip ROM is part of the program memory space and, for some

devices, forms part of the data memory space. The amount of on-chip ROM available on

each device varies, as indicated in Table 4.1. On devices with a small amount of ROM (2K

words), the ROM contains a boot loader, which is useful for booting to faster on-chip or

external RAM during the start-up sequence. The boot loader algorithm initializes the DSP

to a known state and provides a simple mechanism by which the user’s application code

can be loaded onto the DSP and program execution initiated. The boot loader is very flex-

Memory structures 4.1.1

DSP devices – beyond the core 209

210 Chapter 4 ❚ DSP systems – interfacing with the outside world

'548 Program memory

0000h

2000h

4000h

6000h

8000h

A000h

C000h

E000h

FFFFh

OVLY = 0

OVLY = 1

2000h–7FFFh External (paged)

2000–7FFFh On-chip SARAM

OVLY = 0

OVLY = 1

0000h–1FFFh External (paged)

0000h–007Fh Reserved

0080h–1FFFh On-chip DARAM

8000h–EFFFh External (paged)

MP/MC = 0

MP/

MC = 1

F000h–F7FFh Reserved

F800h–FF7Fh On-chip ROM

FF80h–FFFFh Interrupt vectors

F000h–FF7Fh External (paged)

FF80h–FFFFh Interrupt vectors

'548 Data memory

0000h

2000h

4000h

6000h

8000h

A000h

C000h

E000h

FFFFh

2000–7FFFh On-chip SARAM

0000h–005Fh Memory-mapped registers

0060h–007Fh Scratch-pad DARAM

0080h–1FFFh On-chip DARAM

8000h–FFFFh External

Figure 4.2 Memory

map showing the

program and data

space defined for a

TMS320C548 DSP

device

Table 4.1 Texas

Instruments C54x

DSP – on-chip

program and data

memory

Memory type C541 C542 C543 C545 C546 C548

ROM 28K 2K 2K 48K 48K 2K

Program 20K 2K 2K 32K 32K 2K

Program/data 8K 0 0 16K 16K 0

DARAM* 5K 10K 10K 6K 6K 8K

SARAM* 0000024K

* The dual-access RAM (DARAM) and single-access RAM (SARAM) can be configured as data memory or program/

data memory.

ible and allows the application code to be loaded from slow external ROMs or via a serial

interface, host port or through the use of JTAG. On devices with larger amounts of ROM,

a portion of the ROM may be mapped into both data and program space. The larger

ROMs are also custom ROMs: where the user provides the code or data to be pro-

grammed into the ROM in object file format and Texas Instruments generates the

appropriate process mask to program the ROM.

On-chip dual-access RAM (DARAM). The DARAM is composed of several blocks.

Because each DARAM block can be accessed twice per machine cycle, the central process-

ing unit, CPU, can read from and write to a single block of DARAM in the same cycle. The

DARAM is always mapped in data space and is primarily intended to store data values. It

can also be mapped into program space and used to store program code.

On-chip single-access RAM (SARAM). The SARAM is also composed of several blocks.

Each block is accessible once per machine cycle for either reading or writing. The SARAM

is always mapped in data space and is primarily intended for storage of data values. It can

also be mapped into program space and used to store program code.

Memory-mapped registers. The data memory space contains memory-mapped registers

for the CPU and the on-chip peripherals. These registers are located on data page 0, sim-

plifying access to them. The memory-mapped access provides a convenient way to save

and restore the registers for context switches and to transfer information between the

accumulators and the other registers.

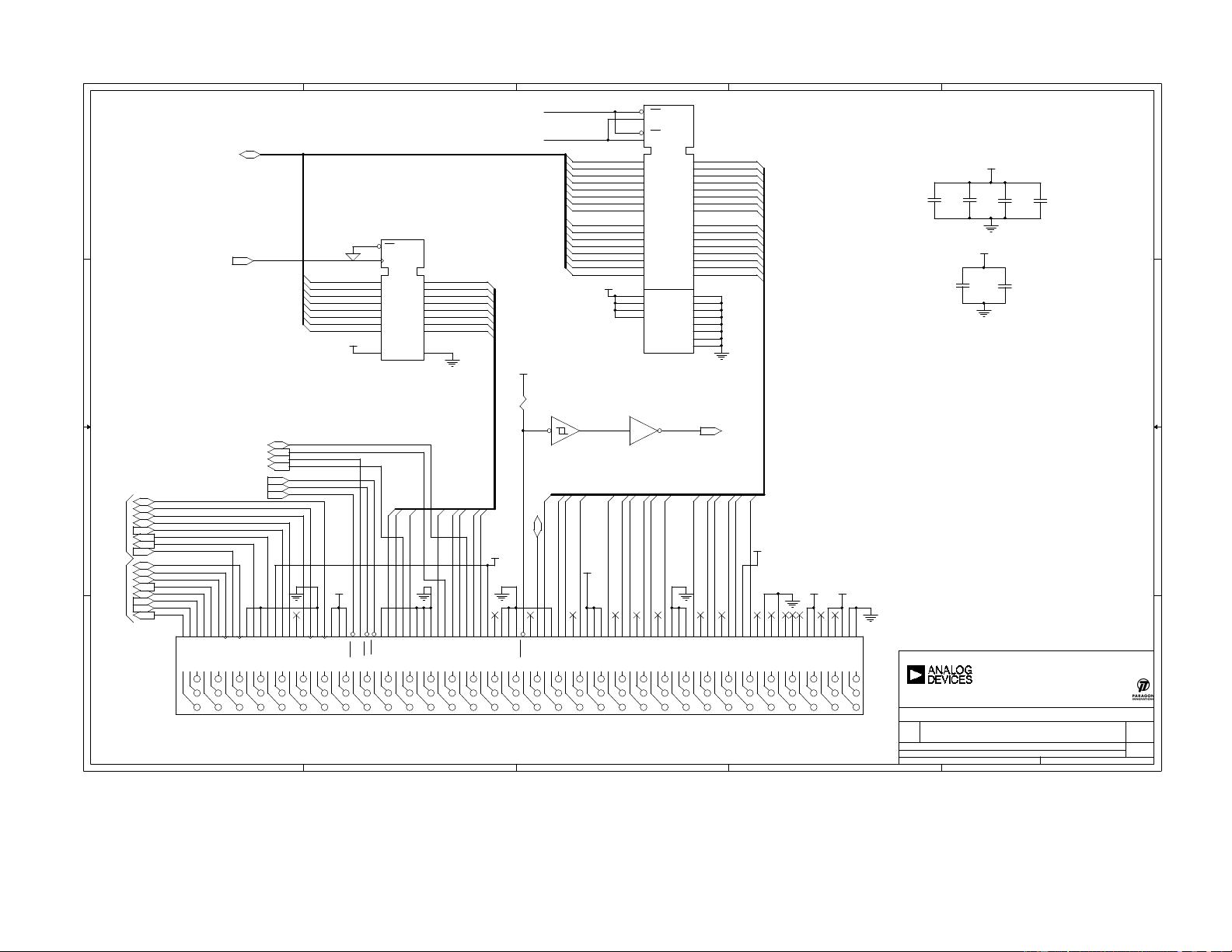

It has been mentioned that the C54x DSP presented in this example is able to make use of

dual-access RAM, DARAM. This type of fast random access memory can be written to or

read from twice in each instruction cycle and hence the potential data throughput rate of

the DSP device is increased. Dual accesses are achieved through the use of a multiple bus

architecture, as shown in Figure 4.3. The diagram of Figure 4.3 shows the eight internal

buses used on the C54x DSP. Of these, four are allocated to addressing and another four

allocated to carry program or data information. Specifically, the C54x DSP uses three

internal data ‘highways’ labelled CB, DB and EB with associated address buses CAB, CDB

and CEB respectively. Also one of the busses is allocated to carrying program instructions

and is labelled PB with an associated program address bus, PAB.

Although internally many DSP devices, including the C54x, are structured with a

multibus architecture, this is rarely replicated to the outside world. Most DSPs are pro-

vided with some sort of memory interface that will multiplex the internal multibus

structure down to a single set of external I/O lines including one full-width address and

data bus. In the case of the C54x DSP this interface is represented by the block shown on

the right hand side of Figure 4.3. This fact is confirmed by observing external pin connec-

tions provided on the DSP chip itself, as identified in Figure 4.4.

Because DSP devices make use of a Harvard architecture incorporating at least one program

and data memory area, they will usually have separate hardware to generate the required

addressing information. In the case of the program address generation unit, this will incor-

porate the program instruction counter, PC, which is used to step through the program

DSP devices – beyond the core 211

Address generation units 4.1.2