没有合适的资源?快使用搜索试试~ 我知道了~

USXGMII-Singleport-Copper-Interface

需积分: 26 4 下载量 152 浏览量

2022-11-12

10:36:37

上传

评论

收藏 1.24MB PDF 举报

温馨提示

试读

33页

USXGMII_Singleport_Copper_Interface cisco

资源推荐

资源详情

资源评论

Date printed: 7/30/2019 USXGMII- Copper PHY: EDCS- 1150953

Copyright 2014 Cisco Systems 1 Cisco Confidential – Controlled Access

A printed copy of this document is considered uncontrolled. Refer to the online version for the controlled revision.

Document Number

EDCS- 1150953

Based on

Template

EDCS-189229 Rev 20

Created By

Amrik Bains

Contributors

Arvind Kansal

Universal SXGMII Interface for a Single

MultiGigabit Copper Network Port

The Universal Serial Media Independent Interface for carrying single network port over a single

SERDES (USXGMII) is specified in this document to meet the following requirements:

• Convey Single network ports over an USXGMII MAC-PHY interface

• Utilize a 64/66 PCS to minimize power and serial bandwidth

• Use modified 802.3by section 108.5.2.4, to add Alignment Markers to support

multiple ports over single SERDES

• System Interface operates in full duplex mode only

• Ability to send PTP time stamp from PHY to MAC to improve accuracy/jitter on

encrypted/non-encrypted PTP packet with MACSec is in the ASIC

• Hardware assisted auto-negotiation for all supported speeds

• Flexibility to add new features using Extension Field in pre-amble

USXGMII isn’t a single protocol, but rather an architecture that allows for the definition of

specific interfaces in a way that maximizes reuse and reduces risk. There are other

implementation targeted at different applications and contact Cisco for details. A PHY can

implement one or more options specified above based on a particular application, cost and power

optimization.

Date printed: 7/30/2019 USXGMII- Copper PHY: EDCS- 1150953

Copyright 2014 Cisco Systems 2 Cisco Confidential – Controlled Access

A printed copy of this document is considered uncontrolled. Refer to the online version for the controlled revision.

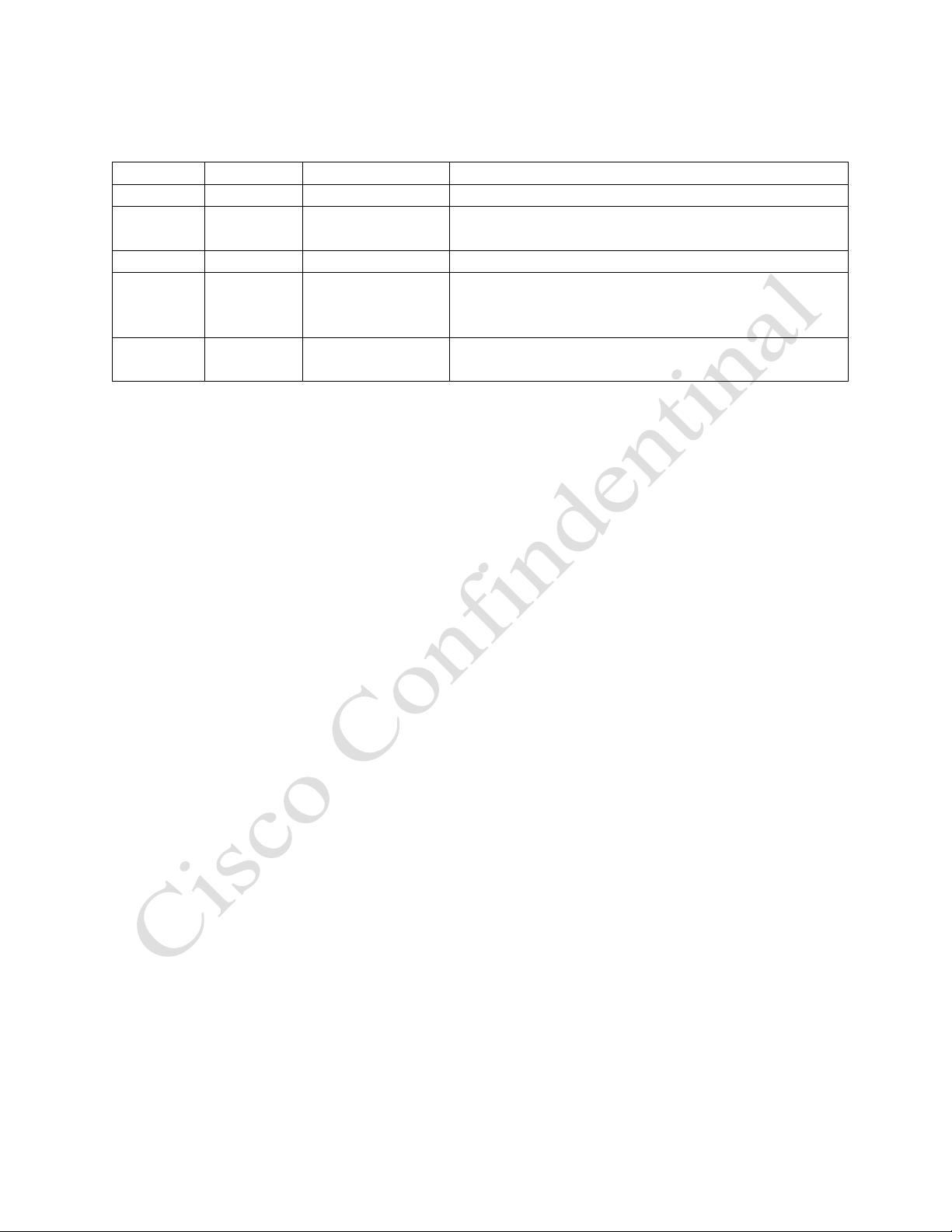

Modification History

Revision

Date

Originator

Comments

2.0

11/12/2015

Amrik Bains

First official Cisco release derived from rev2.0

2.1

04/11/2016

Amrik Bains

Typo fix on page 23 for data bit on the wire. Hex value is

the same as before.

2.2

05/11/2016

Amrik Bains

Remove USXGMII flow control typo’s

2.3

11/01/2016

Amrik Bains

Extension Field Type typo correction to

Extension Field contains Tag/Signature associated with

for time-stamp to be taken by the PHY

2.4

07/30/2019

Amrik Bains

Clarification on IPG and Pre-amble processing in the

PHY

Date printed: 7/30/2019 USXGMII- Copper PHY: EDCS- 1150953

Copyright 2014 Cisco Systems 3 Cisco Confidential – Controlled Access

A printed copy of this document is considered uncontrolled. Refer to the online version for the controlled revision.

Table of Contents

1 Overview .................................................................................................................................. 6

1.1 In-band Control and Status Signaling ................................................................................ 9

1.1.1 Auto-neg Mechanism .................................................................................................. 9

1.1.2 Auto-negotiation Message ........................................................................................ 10

1.1.3 Packet Control Header .............................................................................................. 13

2 Implementation Specification ................................................................................................ 15

2.1 XGMII Mapping .............................................................................................................. 15

2.2 GMII Mapping ................................................................................................................. 15

2.3 MII Mapping.................................................................................................................... 15

2.4 Pause Frame Support ....................................................................................................... 15

2.5 Auto-neg Mechanism ...................................................................................................... 15

2.5.1 Transmitting Configuration Words ........................................................................... 16

2.6 Rate Adaptation - Replicating Transmit Bytes ................................................................ 16

2.6.1 Tx 10G Mode ............................................................................................................ 17

2.6.2 10G Mode Sampling Received Bytes ....................................................................... 18

2.6.3 Tx 5G Mode .............................................................................................................. 18

2.6.4 Rx 5G Sampling Received Bytes .............................................................................. 19

2.6.5 Receiving Configuration Words ............................................................................... 19

2.6.6 Clocking .................................................................................................................... 19

2.6.7 Hardware Auto-negotiation Programming Sequence ............................................... 19

2.6.8 Port ASIC Software Controlled Negotiation Programming Sequence ..................... 20

2.7 USXGMII Packet Control Header Implementation ........................................................ 21

2.8 PHY Implementation ....................................................................................................... 26

2.8.1 Rx PHY Block .......................................................................................................... 26

2.8.2 Tx PHY Block........................................................................................................... 27

2.8.3 MDI: Tx IPG and Pre-amble Processing on MDI .................................................... 27

2.9 Electrical Specification .................................................................................................... 29

3 Appendix ................................................................................................................................ 31

Date printed: 7/30/2019 USXGMII- Copper PHY: EDCS- 1150953

Copyright 2014 Cisco Systems 4 Cisco Confidential – Controlled Access

A printed copy of this document is considered uncontrolled. Refer to the online version for the controlled revision.

Table of Figures

Figure 1: USXGMII Port ASIC Functional Block Diagram .......................................................... 7

Figure 2 USXGMII PHY Functional Block Diagram .................................................................... 8

Figure 3: Packet Control Header (PCH) Format........................................................................... 13

Figure 4: Packet Information Message Mapping in Pre-amble .................................................... 21

Figure 5: Bit order for Serial CRC Computation .......................................................................... 23

Figure 6: CRC Calculation............................................................................................................ 24

Table of Tables

Table 1: USXGMII Single Port Options ......................................................................................... 6

Table 2: Definition of channel control information passes between links .................................... 10

Table 3: Auto-neg Message aligned to Ordered Set followed Data and then by 7-bit Control

Characters ............................................................................................................................... 11

Table 4 Auto-neg Message aligned to Control Code followed by Ordered Set ........................... 12

Table 5: Auto-neg Message aligned to Ordered Set and NO Control Codes ............................... 12

Table 6: Definition of channel control information passed between links via UsxgmiiPCH[47:0]

................................................................................................................................................ 14

Table 7: UsxgmiiPCH Placement when SOP in LANE 0 ............................................................ 25

Table 8: UsxgmiiPCH Placement when SOP in LANE 4 – Part1 ................................................ 25

Table 9: UsxgmiiPCH Placement when SOP in LANE 4 – Part 2 ............................................... 25

Date printed: 7/30/2019 USXGMII- Copper PHY: EDCS- 1150953

Copyright 2014 Cisco Systems 5 Cisco Confidential – Controlled Access

A printed copy of this document is considered uncontrolled. Refer to the online version for the controlled revision.

Definitions

MII - Media Independent Interface: A digital interface that provides a 4-bit wide datapath between a 10/100 Mbit/s

PHY and a MAC sublayer. Since MII is a subset of GMII, in this document, we will use the term “GMII” to cover

all of the specification regarding the MII interface.

GMII- Gigabit Media Independent Interface: A digital interface that provides an 8-bit wide datapath between a

1000 Mbit/s PHY and a MAC sublayer. It also supports the 4-bit wide MII interface as defined in the IEEE 802.3z

specification. In this document, the term “GMII” covers all 10/100/1000 Mbit/s interface operations.

LPI- Low Power Idle: An alternative form of idle signaling that is used by the MAC to indicate that the PHY may

enter a low power state and signal this change of state to the link partner; and is used by the PHY to signal to the

MAC that the link partner has entered a low power state. The functions are defined by IEEE 802.3az in IEEE 802.3

clauses 22, 24, 25 (for 100Mb/s); 35, 36, 40, 70 (for 1Gb/s); 46, 48, 49, 55, 71, 72 (for 10GE); and 78 (for overall

descriptions).

SGMII- Serial Gigabit Media Independent Interface: A digital interface that provides a 1.25 Gbps serial dual-data-

rate datapath between a 1000 Mbit/s PHY and a MAC sublayer. Refer to ENG-46158

QSGMII- Quad Serial Gigabit Media Independent Interface: A digital interface that provides a 5.0 Gbps serial

datapath between four 1000 Mbit/s PHY ports and a MAC sublayer. Refer to EDCS-540103

USGMII - Universal Serial Gigabit Media Independent Interface: A digital interface that provides capability to

carry multi-port/multi-rate serial datapath between PHY ports and a MAC sublayer using 8B/10B coding. Refer to

EDCS 1155168

USXGMII - Universal Serial 10 Gigabit Media Independent Interface: A digital interface that provides capability to

carry multiport/multi-rate serial datapath between PHY ports and a MAC sublayer using 64B/66B coding.

剩余32页未读,继续阅读

资源评论

liuyongchong

- 粉丝: 3

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功