没有合适的资源?快使用搜索试试~ 我知道了~

C1547695_FIFO存储器规格书_RENESAS(瑞萨)_IDTFIFO存储器规格书.PDF

需积分: 1 0 下载量 102 浏览量

2023-09-20

11:14:11

上传

评论

收藏 525KB PDF 举报

温馨提示

试读

55页

C1547695_FIFO存储器规格书_RENESAS(瑞萨)_IDTFIFO存储器规格书.PDF

资源推荐

资源详情

资源评论

1

JUNE 2017

DSC-5994/16

©

2017 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The TeraSync FIFO is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

2.5 VOLT HIGH-SPEED TeraSync

TM

FIFO 72-BIT CONFIGURATIONS

16,384 x 72, 32,768 x 72,

65,536 x 72, 131,072 x 72

IDT72T7285, IDT72T7295,

IDT72T72105, IDT72T72115

FUNCTIONAL BLOCK DIAGRAM

INPUT REGISTER

OUTPUT REGISTER

RAM ARRAY

16,384 x 72

32,768 x 72

65,536 x 72

131,072 x 72

FLAG

LOGIC

FF/IR

PAF

EF/OR

PAE

HF

READ POINTER

READ

CONTROL

LOGIC

WRITE CONTROL

LOGIC

WRITE POINTER

RESET

LOGIC

WEN

WCLK/WR

D0 -Dn (x72, x36 or x18)

LD

MRS

REN

RCLK/RD

OE

Q0 -Qn (x72, x36 or x18)

OFFSET REGISTER

PRS

FWFT/SI

SEN

RT

5994 drw01

BUS

CONFIGURATION

BM

CONTROL

LOGIC

BE

OW

IP

PFM

FSEL0

FSEL1

IW

MARK

SCLK

RCS

JTAG CONTROL

(BOUNDARY SCAN)

TCK

TMS

TDO

TDI

TRST

ASYR

WCS

ERCLK

EREN

HSTL I/0

CONTROL

Vref

WHSTL

RHSTL

ASYW

SHSTL

FEATURES:

••

••

• Choose among the following memory organizations:

IDT72T7285

⎯⎯

⎯⎯

⎯ 16,384 x 72

IDT72T7295

⎯⎯

⎯⎯

⎯ 32,768 x 72

IDT72T72105

⎯⎯

⎯⎯

⎯ 65,536 x 72

IDT72T72115

⎯⎯

⎯⎯

⎯ 131,072 x 72

••

••

• Up to 225 MHz Operation of Clocks

••

••

• User selectable HSTL/LVTTL Input and/or Output

••

••

• Read Enable & Read Clock Echo outputs aid high speed operation

••

••

• User selectable Asynchronous read and/or write port timing

••

••

• 2.5V LVTTL or 1.8V, 1.5V HSTL Port Selectable Input/Ouput voltage

••

••

• 3.3V Input tolerant

••

••

• Mark & Retransmit, resets read pointer to user marked position

••

••

• Write Chip Select (WCS) input disables Write Port HSTL inputs

••

••

• Read Chip Select (RCS) synchronous to RCLK

••

••

• Programmable Almost-Empty and Almost-Full flags, each flag can

default to one of eight preselected offsets

••

••

• Program programmable flags by either serial or parallel means

••

••

• Selectable synchronous/asynchronous timing modes for Almost-

Empty and Almost-Full flags

••

••

• Separate SCLK input for Serial programming of flag offsets

••

••

• User selectable input and output port bus-sizing

- x72 in to x72 out

- x72 in to x36 out

- x72 in to x18 out

- x36 in to x72 out

- x18 in to x72 out

••

••

• Big-Endian/Little-Endian user selectable byte representation

••

••

• Auto power down minimizes standby power consumption

••

••

• Master Reset clears entire FIFO

••

••

• Partial Reset clears data, but retains programmable settings

••

••

• Empty, Full and Half-Full flags signal FIFO status

••

••

• Select IDT Standard timing (using EF and FF flags) or First Word

Fall Through timing (using OR and IR flags)

••

••

• Output enable puts data outputs into high impedance state

••

••

• JTAG port, provided for Boundary Scan function

••

••

• Available in 324-pin (19mm x 19mm)Plastic Ball Grid Array (PBGA)

••

••

• Easily expandable in depth and width

••

••

• Independent Read and Write Clocks (permit reading and writing

simultaneously)

••

••

• High-performance submicron CMOS technology

••

••

• Industrial temperature range (–40

°°

°°

°C to +85

°°

°°

°C) is available

••

••

• Green parts are available, see ordering information

2

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T7285/72T7295/72T72105/72T72115 2.5V TeraSync

™™

™™

™ 72-BIT FIFO

16,384 x 72, 32,768 x 72, 65,536 x 72, 131,072 x 72

PIN CONFIGURATION

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

D21

D19 D20 D13

GND

TDO

V

CC

D4 TMS

V

CC

D5D10

D23

D22

D1

Q24

Q14GND Q0 Q2 Q11Q8Q3

V

DDQ

V

CC

V

CC

V

CC

GND V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

CC

D60

D57

D59

D51

D48

D45

D24

D64

GND

GND

GND

GND

GND

GND

GND

GND GND

GND

GND

GND

GND

GND

GND

GND

D69

REN

GND

PAF

EREN

Q64

OE

RCLKD63

D66

D39

Q69 Q66

Q65

Q52

Q49

Q46

12 345678910111213141516

A1 BALL PAD CORNER

MRS

D67

D38

D35

D32

D29

D26

FF

EF

D44

D41

D36

D33

D30

D27

D56

D53

D50

D47

SEN

D43

D37

D40

D34

D31

D28

D25 Q27

Q43

Q40

Q39

Q36

Q33

Q30

RCS

Q67Q70

D52

D49

D46

SCLK

D42

D58 D62 D70

WCS

D65 D71D68

PAELD HF

GND Q68MARK Q71

RT

SHSTLFWFT/SI FS0OW IPFS1

BE

GND PFMBM

ASYR

RHSTL

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

CC

V

CC

WHSTL

ASYW

VREF

IW

V

CC

V

CC

V

CC

V

CC

D61

Q58

Q55D54

WEN

GND

WCLK

PRS

D55

5994 drw02

U

V

D18

V

CC

D16 D15

TDI

TCK

TRST

D6

D0

D2

D9D12

D14D17

D3

Q15

Q16GND ERCLK Q4 Q13Q10Q7

Q5D11 D8D7 GND Q6Q1 Q9 Q12

17 18

Q22

Q20Q21

Q23

V

DDQ

Q63

Q62

Q54

Q51

Q48

Q25

Q45

Q42

Q37

Q34

Q31

Q28

Q61

Q59

Q56

Q41

Q38

Q35

Q32

Q29

Q26

Q53

Q50

Q47

Q44

Q60

Q57

Q19

V

DDQ

Q17

Q18

V

CC

V

CC

V

CC

V

DDQ

V

CC

GNDGND V

DDQ

V

DDQ

V

DDQ

V

CC

V

CC

V

CC

V

DDQ

V

CC

GNDGND V

DDQ

V

DDQ

V

DDQ

GNDV

CC

V

CC

GNDGND GNDGND GND V

DDQ

V

DDQ

GND

GND

GND

V

CC

V

CC

GND

V

CC

V

CC

GND V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

CC

V

CC

GND GNDGND V

DDQ

GNDV

CC

V

CC

V

DDQ

V

CC

V

CC

GND V

DDQ

V

DDQ

V

DDQ

GNDV

CC

V

CC

GNDV

CC

V

CC

GNDV

CC

V

CC

GNDV

CC

V

CC

GND V

DDQ

V

DDQ

GND

V

DDQ

V

DDQ

GND

V

DDQ

V

DDQ

GND

V

DDQ

V

DDQ

PBGA: 1mm pitch, 19mm x 19mm (BB324, BBG324) Order code: BB, BBG

TOP VIEW

3

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T7285/72T7295/72T72105/72T72115 2.5V TeraSync

™™

™™

™ 72-BIT FIFO

16,384 x 72, 32,768 x 72, 65,536 x 72, 131,072 x 72

DESCRIPTION:

The IDT72T7285/72T7295/72T72105/72T72115 are exceptionally deep,

extremely high speed, CMOS First-In-First-Out (FIFO) memories with clocked

read and write controls and a flexible Bus-Matching x72/x36/x18 data flow.

These FIFOs offer several key user benefits:

• Flexible x72/x36/x18 Bus-Matching on both read and write ports

• A user selectable MARK location for retransmit

• User selectable I/O structure for HSTL or LVTTL

• Asynchronous/Synchronous translation on the read or write ports

• The first word data latency period, from the time the first word is written to an

empty FIFO to the time it can be read, is fixed and short.

• High density offerings up to 9 Mbit

Bus-Matching TeraSync FIFOs are particularly appropriate for network,

video, telecommunications, data communications and other applications that

need to buffer large amounts of data and match busses of unequal sizes.

Each FIFO has a data input port (Dn) and a data output port (Qn), both of

which can assume either a 72-bit, 36-bit or a 18-bit width as determined by the

state of external control pins Input Width (IW), Output Width (OW), and Bus-

Matching (BM) pin during the Master Reset cycle.

The input port can be selected as either a Synchronous (clocked) interface,

or Asynchronous interface. During Synchronous operation the input port is

controlled by a Write Clock (WCLK) input and a Write Enable (WEN) input. Data

present on the Dn data inputs is written into the FIFO on every rising edge of

WCLK when WEN is asserted. During Asynchronous operation only the WR

input is used to write data into the FIFO. Data is written on a rising edge of WR,

the WEN input should be tied to its active state, (LOW).

The output port can be selected as either a Synchronous (clocked) interface,

or Asynchronous interface. During Synchronous operation the output port is

controlled by a Read Clock (RCLK) input and Read Enable (REN) input. Data

is read from the FIFO on every rising edge of RCLK when REN is asserted.

During Asynchronous operation only the RD input is used to read data from the

FIFO. Data is read on a rising edge of RD, the REN input should be tied to its

active state, LOW. When Asynchronous operation is selected on the output port

the FIFO must be configured for Standard IDT mode, also the RCS should be

tied LOW and the OE input used to provide three-state control of the outputs, Qn.

The output port can be selected for either 2.5V LVTTL or HSTL operation,

this operation is selected by the state of the RHSTL input during a master reset.

An Output Enable (OE) input is provided for three-state control of the outputs.

A Read Chip Select (RCS) input is also provided, the RCS input is synchronized

to the read clock, and also provides three-state control of the Qn data outputs.

When RCS is disabled, the data outputs will be high impedance. During

Asynchronous operation of the output port, RCS should be enabled, held LOW.

Echo Read Enable, EREN and Echo Read Clock, ERCLK outputs are

provided. These are outputs from the read port of the FIFO that are required

for high speed data communication, to provide tighter synchronization between

the data being transmitted from the Qn outputs and the data being received by

the input device. Data read from the read port is available on the output bus with

respect to EREN and ERCLK, this is very useful when data is being read at

high speed. The ERCLK and EREN outputs are non-functional when the Read

port is setup for Asynchronous mode.

The frequencies of both the RCLK and the WCLK signals may vary from 0

to fMAX with complete independence. There are no restrictions on the frequency

of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices: IDT

Standard mode and First Word Fall Through (FWFT) mode.

In IDT Standard mode, the first word written to an empty FIFO will not appear

on the data output lines unless a specific read operation is performed. A read

operation, which consists of activating REN and enabling a rising RCLK edge,

will shift the word from internal memory to the data output lines.

In FWFT mode, the first word written to an empty FIFO is clocked directly

to the data output lines after three transitions of the RCLK signal. A REN does

not have to be asserted for accessing the first word. However, subsequent

words written to the FIFO do require a LOW on REN for access. The state of

the FWFT/SI input during Master Reset determines the timing mode in use.

For applications requiring more data storage capacity than a single FIFO

can provide, the FWFT timing mode permits depth expansion by chaining FIFOs

in series (i.e. the data outputs of one FIFO are connected to the corresponding

data inputs of the next). No external logic is required.

These FIFOs have five flag pins, EF/OR (Empty Flag or Output Ready),

FF/IR (Full Flag or Input Ready), HF (Half-full Flag), PAE (Programmable

Almost-Empty flag) and PAF (Programmable Almost-Full flag). The EF and FF

functions are selected in IDT Standard mode. The IR and OR functions are

selected in FWFT mode. HF, PAE and PAF are always available for use,

irrespective of timing mode.

PAE and PAF can be programmed independently to switch at any point in

memory. Programmable offsets determine the flag switching threshold and can

be loaded by two methods: parallel or serial. Eight default offset settings are also

provided, so that PAE can be set to switch at a predefined number of locations

from the empty boundary and the PAF threshold can also be set at similar

predefined values from the full boundary. The default offset values are set during

Master Reset by the state of the FSEL0, FSEL1, and LD pins.

For serial programming, SEN together with LD on each rising edge of

SCLK, are used to load the offset registers via the Serial Input (SI). For parallel

programming, WEN together with LD on each rising edge of WCLK, are used

to load the offset registers via Dn. REN together with LD on each rising edge

of RCLK can be used to read the offsets in parallel from Qn regardless of whether

serial or parallel offset loading has been selected.

During Master Reset (MRS) the following events occur: the read and write

pointers are set to the first location of the FIFO. The FWFT pin selects IDT

Standard mode or FWFT mode.

The Partial Reset (PRS) also sets the read and write pointers to the first

location of the memory. However, the timing mode, programmable flag

programming method, and default or programmed offset settings existing before

Partial Reset remain unchanged. The flags are updated according to the timing

mode and offsets in effect. PRS is useful for resetting a device in mid-operation,

when reprogramming programmable flags would be undesirable.

It is also possible to select the timing mode of the PAE (Programmable Almost-

Empty flag) and PAF (Programmable Almost-Full flag) outputs. The timing

modes can be set to be either asynchronous or synchronous for the PAE and

PAF flags.

If asynchronous PAE/PAF configuration is selected, the PAE is asserted

LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOW-

to-HIGH transition of WCLK. Similarly, the PAF is asserted LOW on the LOW-

to-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH

transition of RCLK.

If synchronous PAE/PAF configuration is selected , the PAE is asserted and

updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is

asserted and updated on the rising edge of WCLK only and not RCLK. The mode

desired is configured during Master Reset by the state of the Programmable Flag

Mode (PFM) pin.

This device includes a Retransmit from Mark feature that utilizes two control

inputs, MARK and , RT (Retransmit). If the MARK input is enabled with respect

to the RCLK, the memory location being read at that point will be marked. Any

subsequent retransmit operation, RT goes LOW, will reset the read pointer to

this ‘marked’ location.

4

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T7285/72T7295/72T72105/72T72115 2.5V TeraSync

™™

™™

™ 72-BIT FIFO

16,384 x 72, 32,768 x 72, 65,536 x 72, 131,072 x 72

DESCRIPTION (CONTINUED)

The device can be configured with different input and output bus widths as

shown in Table 1.

A Big-Endian/Little-Endian data word format is provided. This function is

useful when data is written into the FIFO in long word format (x36/x18) and read

out of the FIFO in small word (x18/x9) format. If Big-Endian mode is selected,

then the most significant byte (word) of the long word written into the FIFO will

be read out of the FIFO first, followed by the least significant byte. If Little-Endian

format is selected, then the least significant byte of the long word written into the

FIFO will be read out first, followed by the most significant byte. The mode desired

is configured during master reset by the state of the Big-Endian (BE) pin. See

Figure 5 for Bus-Matching Byte Arrangement.

The Interspersed/Non-Interspersed Parity (IP) bit function allows the user

to select the parity bit in the word loaded into the parallel port (D0-Dn) when

programming the flag offsets. If Interspersed Parity mode is selected, then the

FIFO will assume that the parity bit is located in bit positions D8, D17, D26 and

D35 during the parallel programming of the flag offsets. If Non-Interspersed

Parity mode is selected, then D8 and D17 are assumed to be valid bits. IP mode

is selected during Master Reset by the state of the IP input pin.

If, at any time, the FIFO is not actively performing an operation, the chip will

automatically power down. Once in the power down state, the standby supply

current consumption is minimized. Initiating any operation (by activating control

inputs) will immediately take the device out of the power down state.

Both an Asynchronous Output Enable pin (OE) and Synchronous Read

Chip Select pin (RCS) are provided on the FIFO. The Synchronous Read Chip

Select is synchronized to the RCLK. Both the output enable and read chip select

control the output buffer of the FIFO, causing the buffer to be either HIGH

impedance or LOW impedance.

A JTAG test port is provided, here the FIFO has fully functional Boundary

Scan feature, compliant with IEEE 1449.1 Standard Test Access Port and

Boundary Scan Architecture.

The TeraSync FIFO has the capability of operating its ports (write and/or

read) in either LVTTL or HSTL mode, each ports selection independent of the

other. The write port selection is made via WHSTL and the read port selection

via RHSTL. An additional input SHSTL is also provided, this allows the user

to select HSTL operation for other pins on the device (not associated with the

write or read ports).

The IDT72T7285/72T7295/72T72105/72T72115 are fabricated using

high speed submicron CMOS technology.

5

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72T7285/72T7295/72T72105/72T72115 2.5V TeraSync

™™

™™

™ 72-BIT FIFO

16,384 x 72, 32,768 x 72, 65,536 x 72, 131,072 x 72

TABLE 1 — BUS-MATCHING CONFIGURATION MODES

NOTE:

1. Pin status during Master Reset.

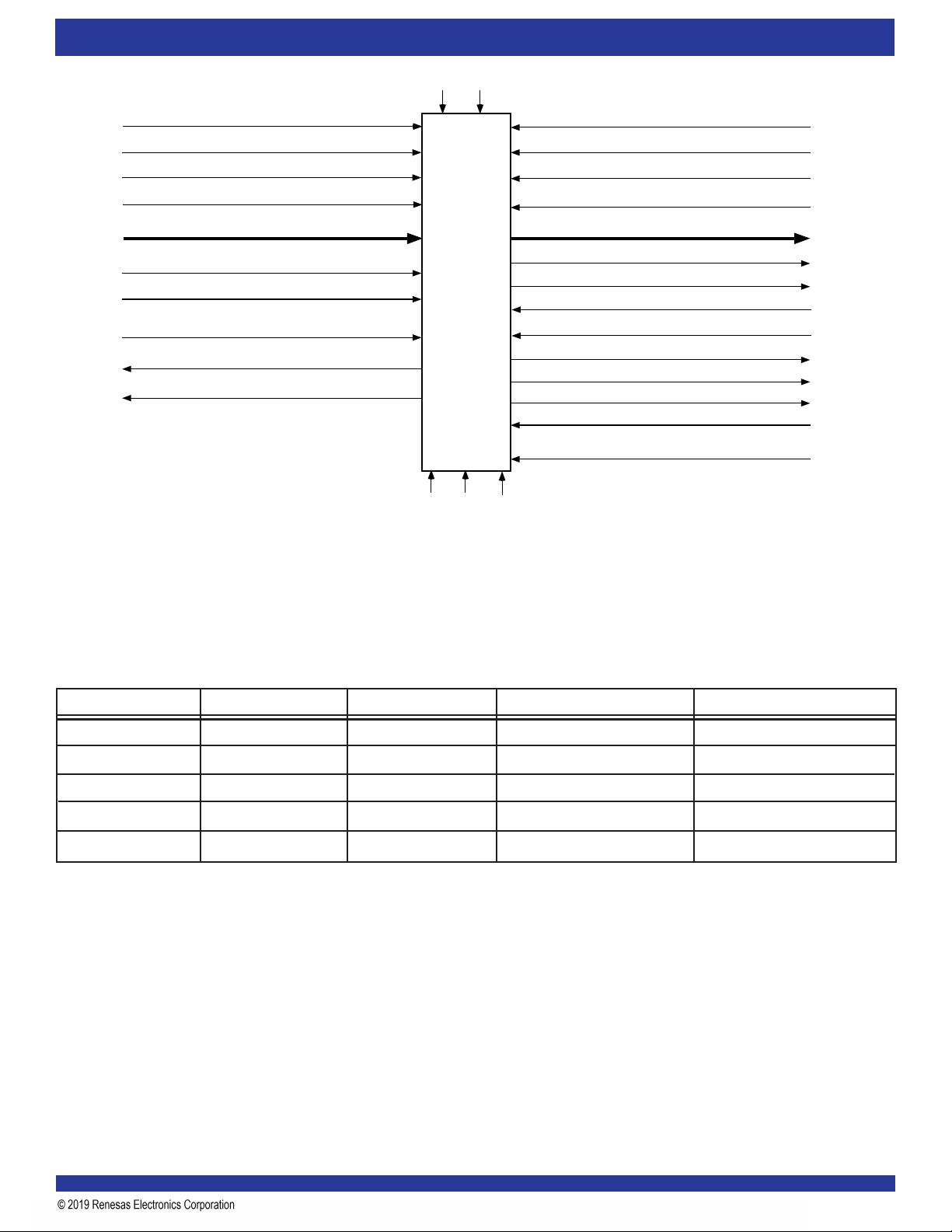

Figure 1. Single Device Configuration Signal Flow Diagram

(x72, x36, x18) DATA OUT (Q

0

- Q

n

)(x72, x36, x18) DATA IN (D

0

- D

n

)

MASTER RESET (MRS)

READ CLOCK (RCLK/RD)

READ ENABLE (REN)

OUTPUT ENABLE (OE)

EMPTY FLAG/OUTPUT READY (EF/OR)

PROGRAMMABLE ALMOST-EMPTY (PAE)

WRITE CLOCK (WCLK/WR)

WRITE ENABLE (WEN)

LOAD (LD)

FULL FLAG/INPUT READY (FF/IR)

PROGRAMMABLE ALMOST-FULL (PAF)

IDT

72T7285

72T7295

72T72105

72T72115

PARTIAL RESET (PRS)

FIRST WORD FALL THROUGH/

SERIAL INPUT (FWFT/SI)

RETRANSMIT (RT)

5994 drw03

HALF-FULL FLAG (HF)

SERIAL ENABLE(SEN)

INPUT WIDTH (IW)

OUTPUT WIDTH (OW)

BIG-ENDIAN/LITTLE-ENDIAN (BE)

INTERSPERSED/

NON-INTERSPERSED PARITY (IP)

BUS-

MATCHING

(BM)

SERIAL CLOCK (SCLK)

MARK

READ CHIP SELECT (RCS)

RCLK ECHO, ERCLK

REN ECHO, EREN

WRITE CHIP SELECT (WCS)

BM IW OW Write Port Width Read Port Width

L L L x72 x72

H L L x72 x36

H L H x72 x18

H H L x36 x72

H H H x18 x72

剩余54页未读,继续阅读

资源评论

z同学的编程之路

- 粉丝: 1880

- 资源: 2130

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功