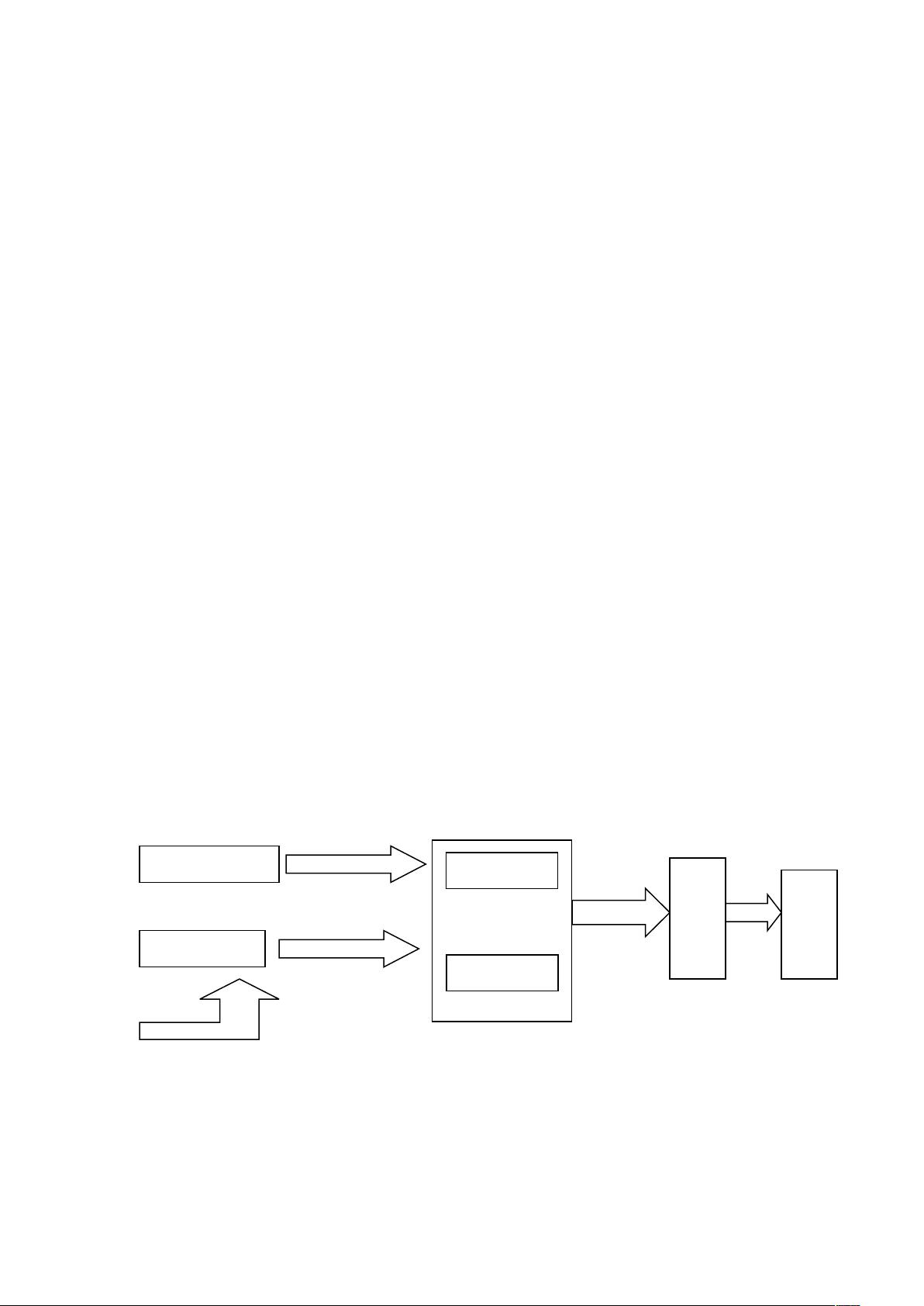

数字电路课程设计及仿真(秒表) 数字电路课程设计及仿真(秒表)是数字电路设计的重要组成部分。该设计的目标是设计一个具有暂停、继续、复位功能的数字秒表,具有高计时精度和可靠性。 设计要求: * 量程:0~99.99s * 计时精度:10ms * 显示方式:十进制格式 * 功能:暂停、继续、复位 设计思路: 数字秒表由四个部分组成:精确的时钟源、十进制计数器、译码器、七段码或液晶显示电路。时钟源产生符合精度要求的基准时钟,本设计中取 10 毫秒即可。十进制计数器需要 4 个,分别对应 4 个十进制位,输出为 BCD 码。若采用七段码显示器则译码器完成 BCD 到七段码的译码,由 4 位显示电路动态显示结果。 电路设计: * 时钟源电路:采用电路板上的 1000HZ 脉冲,74ls90 芯片具有 2-5-10 进制功能,由 5 片 74ls90 芯片构成分频、计数电路。 * 分频电路:第一片 74ls90 芯片将直接输入的 1000HZ 脉冲源分成 100HZ,后四片 74ls90 芯片再逐次进行 10H、1HZ、0.1HZ 的分频工作。 * 计数电路:需要 4 个十进制计数器,4 个计数器由低位到高位连接起来,每一级的输入脉冲是前一级的十分之一,输出则需要正确连接七段码显示电路。 * 清零功能:将 CKB 与 Q0 相连,时钟脉冲从 CKA 输入,构成 8421BCD 码十进制计数器。74ls90 有两个清零端 R0(1)、R0(2)和两个置九端 R9(1)、R9(2)。在此电路中仅使用其清零功能。 * 开关驱动电路:当 S1 打开时,脉冲不可以通过与门,计数电路就会停止,实现暂停功能,当 S1 闭合时,恢复计数;当 S1 闭合,S2 断开时,R0(1) R0(2)都接低电平,实现计数功能。当 S1 闭合,S2 闭合时,R0(1) R0(2)都接高电平,实现清零功能。 仿真结果: * 仿真图显示了数字秒表的设计结果,证实了该设计的正确性和可靠性。 * 仿真结果表明,该设计能够满足要求的计时精度和功能要求。 结论: 数字电路课程设计及仿真(秒表)设计了一个具有暂停、继续、复位功能的数字秒表,具有高计时精度和可靠性。该设计使用了 74ls90 芯片和七段码显示电路,实现了高效、可靠的计时功能。该设计可以应用于体育比赛、时间准确测量等场合。

剩余7页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于Java Swing的飞机订票管理系统.zip

- (源码)基于Spring Boot和Redis的秒杀系统.zip

- (源码)基于OVMS v3的无线控制台系统(WifiConsole).zip

- (源码)基于Arduino和ESP32的IoT计算机开关系统.zip

- (源码)基于Qt框架的PX4飞行控制器固件升级系统.zip

- (源码)基于Spring Boot和Vue的需求管理系统.zip

- 基于深度学习YOLOv5的车牌检测与识别项目源码

- (源码)基于Python的CSGO饰品价格分析与比较系统.zip

- ccs3.3安装补丁SR12-CCS-v3.3-SR-3.3.82.13 2

- (源码)基于Spring Boot框架的攀枝花物流系统.zip

信息提交成功

信息提交成功