没有合适的资源?快使用搜索试试~ 我知道了~

PowerPC(e200z6核)的汇编指令速查

温馨提示

采用e200z6核的PowerPC芯片汇编指令,比较简略,可用于指令的速查。 此指令集仅适用于e200z6核,其它核的PowerPC指令略有差异。

资源推荐

资源详情

资源评论

Freescale Semiconductor

Addendum

© Freescale Semiconductor, Inc., 2006. All rights reserved.

This errata describes corrections to the e200z6 PowerPC™ Core Reference Manual, Revision 0. For

convenience, the section number and page number of the errata item in the reference manual are provided.

Items in bold are new since the last revision of this document.

To locate any published updates for this document, visit our website listed on the back cover of this

document.

Section, Page No. Changes

2.3.1, 2-8 Add the following to the description of MSR[EE]:

“If MSR[EE] = 0 and a transfer error occurs, a DSI or ISI is taken rather than a

machine check or checkstop, as defined by the PowerPC architecture. For more

information see the note in Section 5.6.2, “Machine Check Interrupt (IVOR1),”.

1

This does not affect the e200z6 with VLE.”

1. Which is provided in an erratum below.

Document Number: e200z6RMAD

Rev. 0.2, 10/2006

Errata to the

e200z6 PowerPC™ Core

Reference Manual, Rev. 0

Errata to the e200z6 PowerPC™ Core Reference Manual, Rev. 0

2 Freescale Semiconductor

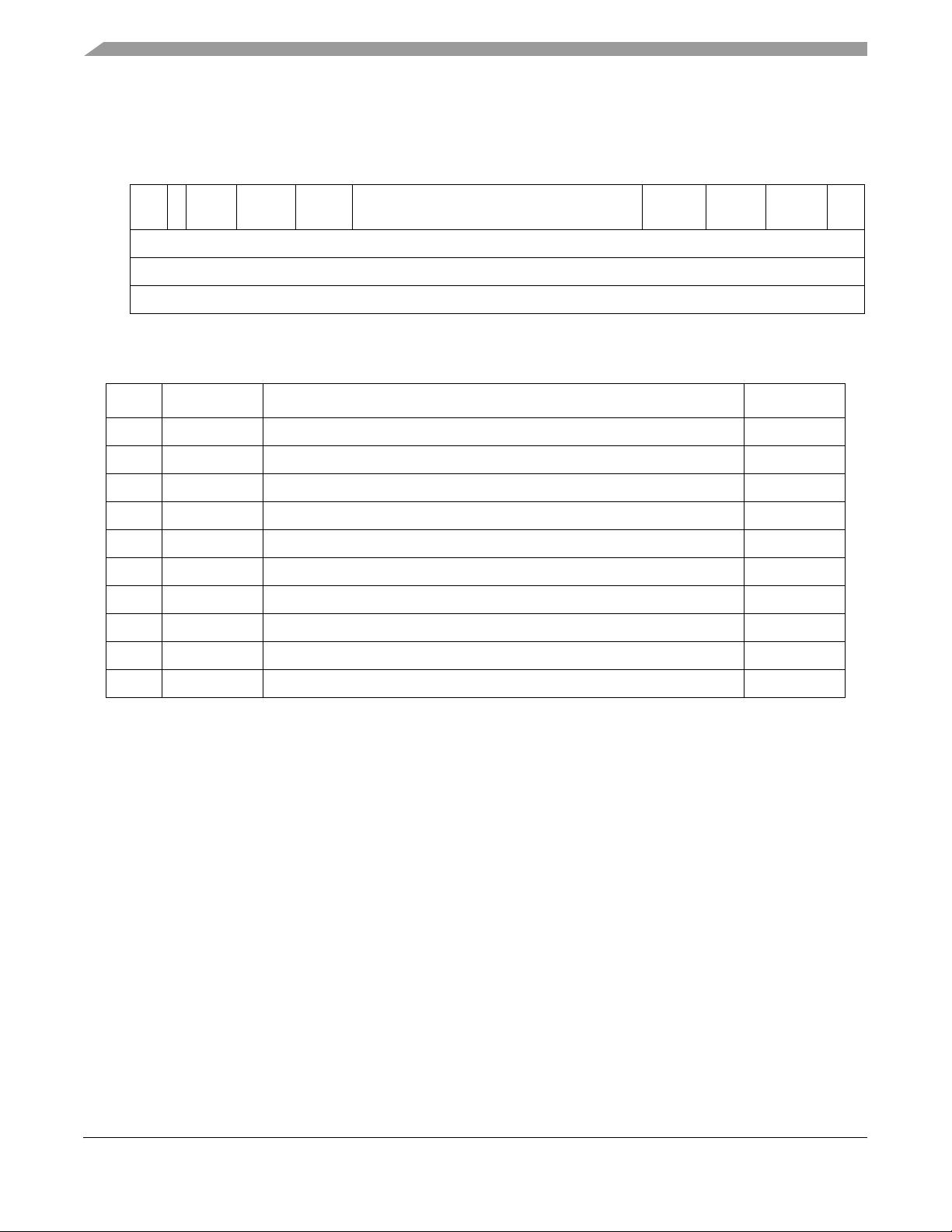

2.7.2.3, 2-26 Machine Check Syndrome Register (MCSR) bits 59 and 60 are incorrectly shown

to be reserved. Replace Figure 2-21 and Table 2-14 with the following:

32 33 34 35 36 37 58 59 60 61 62 63

Field

MCP —

CP_

PERR

CPERR

EXCP_

ERR

—

BUS_

IRERR

BUS_

DRERR

BUS_

WRERR

—

Reset All zeros

R/W R/W

SPR SPR 572

Figure 2-21. Machine Check Syndrome Register (MCSR)

Table 2-14. MCSR Field Descriptions

Bits Name Description Recoverable

32 MCP Machine check input signal Maybe

33 — Reserved, should be cleared. —

34 CP_PERR Cache push parity error Unlikely

35 CPERR Cache parity error Precise

36 EXCP_ERR ISI, ITLB, or bus error on first instruction fetch for an exception handler Precise

37–58 — Reserved, should be cleared. —

59 BUS_IRERR Read bus error on Instruction fetch Unlikely

60 BUS_DRERR Read bus error on data load Unlikely

61 BUS_WRERR Write bus error on buffered store or cache line push Unlikely

62–63 — Reserved, should be cleared. —

Errata to the e200z6 PowerPC™ Core Reference Manual, Rev. 0

Freescale Semiconductor 3

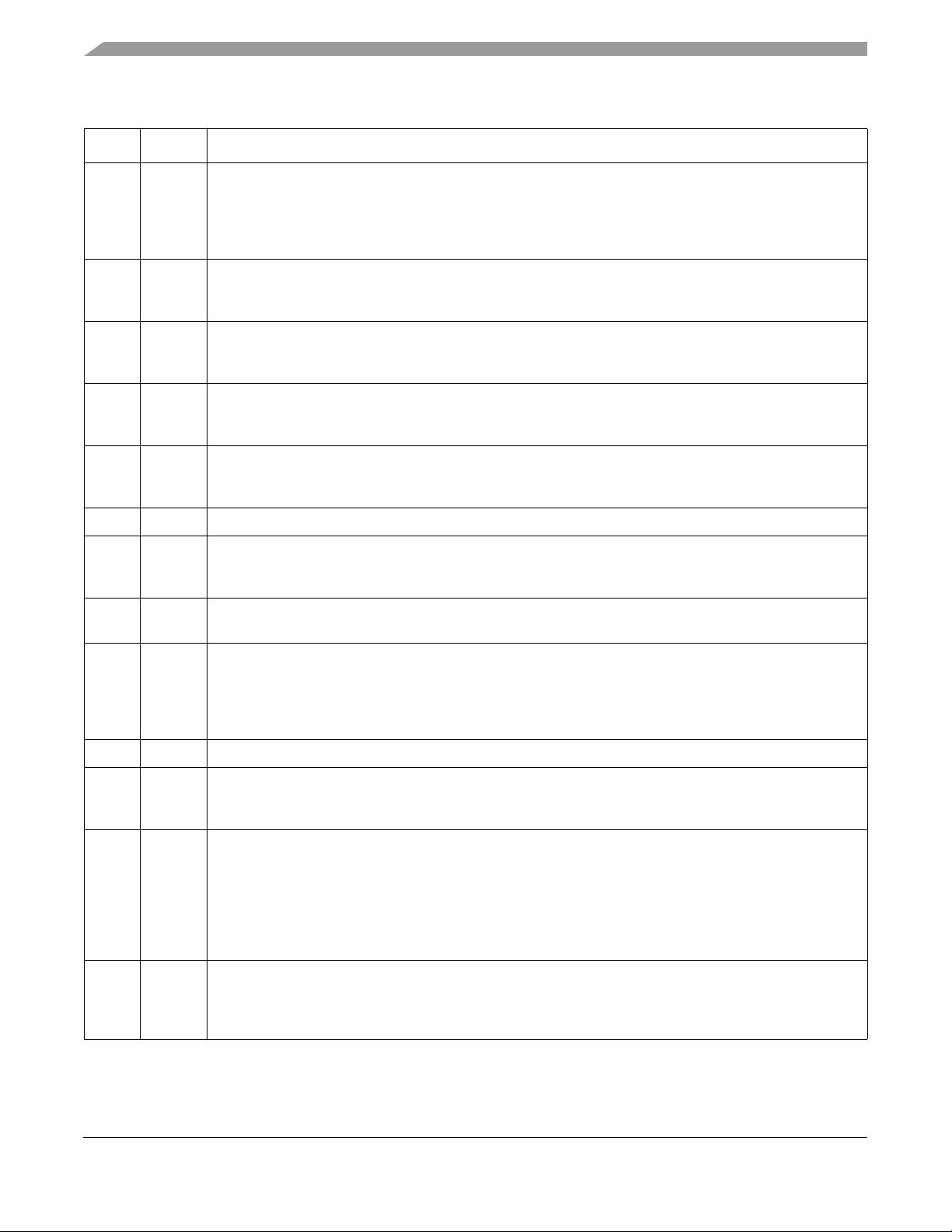

2.13.1, 2-55 Add WAM bit 42 to the L1 Cache Control and Status Register 0 (L1CSR0).

Replace Figure 2-40 and Table 2-26 with the following:

Way Partitioning APU Bits

32 35 36 39 40 41 42 43 44 45 46 47

Field WID WDD AWID AWDD WAM CWM DPB DSB DSTRM CPE

Reset All zeros

R/W R/W

Line Locking APU Bits

48 52 53 54 55 56 60 61 62 63

Field — CUL CLO CLFR — CABT CFI CE

Reset All zeros

R/W R/W

SPR SPR 1010

Figure 2-40. L1 Cache Control and Status Register 0 (L1CSR0)

Table 2-26. L1CSR0 Field Descriptions

Bits Name Description

32–35 WID Way instruction disable. WID and WDD are used for locking ways of the cache and determining the cache

replacement policy.

0 The corresponding way is available for replacement by instruction miss line fills.

1 The corresponding way is not available for replacement by instruction miss line fills.

Bit 0 corresponds to way 0, bit 1 corresponds to way 1, bit 2 corresponds to way 2, and

bit 3 corresponds to way 3.

36–39 WDD Way data disable. WID and WDD are used for locking ways of the cache and determining the cache

replacement policy.

0 The corresponding way is available for replacement by data miss line fills.

1 The corresponding way is not available for replacement by data miss line fills.

Bit 4 corresponds to way 0, bit 5 corresponds to way 1, bit 6 corresponds to way 2, bit 7 corresponds to

way 3.

40 AWID Additional ways instruction disable

0 Additional ways beyond 0–3 are available for replacement by instruction miss line fills.

1 Additional ways beyond 0–3 are not available for replacement by instruction miss line fills.

For the 32-Kbyte 8-way cache, ways 4–7 are considered additional ways.

41 AWDD Additional ways data disable

0 Additional ways beyond 0–3 are available for replacement by data miss line fills.

1 Additional ways beyond 0–3 are not available for replacement by data miss line fills.

For the 32-Kbyte 8-way cache, ways 4–7 are considered additional ways.

42 WAM Cache way partitioning APU. Way access mode.

0 All ways are available for access.

1 Only ways partitioned for the specific type of access are used for a fetch or read operation.

Errata to the e200z6 PowerPC™ Core Reference Manual, Rev. 0

4 Freescale Semiconductor

43 CWM Cache write mode. When set to write-through mode, the W page attribute from an optional MMU is ignored

and all writes are treated as write through required. When set, write accesses are performed in copy-back

mode unless the W page attribute from an optional MMU is set.

0 Cache operates in write-through mode.

1 Cache operates in copy-back mode.

44 DPB Disable push buffer

0 Push buffer enabled

1 Push buffer disabled

45 DSB Disable store buffer

0 Store buffer enabled

1 Store buffer disabled

46 DSTRM Disable streaming

0 Streaming is enabled.

1 Streaming is disabled.

47 CPE Cache parity enable

0 Parity checking is disabled.

1 Parity checking is enabled.

48–52 — Reserved, should be cleared.

53 CUL Cache unable to lock. Indicates a lock set instruction was not effective in locking a cache line. This bit is set

by hardware on an “unable to lock” condition (other than lock overflows), and remain set until cleared by

software writing 0 to this bit location.

54 CLO Cache lock overflow. Indicates a lock overflow (overlocking) condition occurred. Set by hardware on an

overlocking condition, and remains set until cleared by software writing 0 to this bit location.

55 CLFC Cache lock bits flash clear. When written to a 1, a cache lock bits flash clear operation is initiated by

hardware. Once complete, this bit is reset to 0. Writing a 1 while a flash clear operation is in progress results

in an undefined operation. Writing a 0 to this bit while a flash clear operation is in progress has no effect.

Cache lock bits flash clear operations require approximately 134 cycles to complete. Clearing occurs

regardless of the enable (CE) value.

56–60 — Reserved, should be cleared.

61 CABT Cache operation aborted. Indicates a cache invalidate or a cache lock bits flash clear operation was aborted

prior to completion. Set by hardware on an aborted condition, and remains set until cleared by software

writing 0 to this bit location.

62 CINV Cache invalidate

0 No cache invalidate

1 Cache invalidation operation

When written to a 1, a cache invalidation operation is initiated by hardware. Then invalidation is complete,

CINV is reset to 0. Writing a 1 while invalidation is in progress causes an undefined operation. Writing a 0

to this bit while an invalidation operation is in progress is ignored. Cache invalidation operations require

approximately 134 cycles to complete. Invalidation occurs regardless of the enable (CE) value.

63 CE Cache enable. When disabled, cache lookups are not performed for normal load or store accesses.

Other L1CSR0 cache control operations are still available. Also, store buffer operation is not affected by CE.

0 Cache is disabled

1 Cache is enabled

Table 2-26. L1CSR0 Field Descriptions (continued)

Bits Name Description

剩余23页未读,继续阅读

资源评论

- #完美解决问题

- #运行顺畅

- #内容详尽

- #全网独家

- #注释完整

_KINGKANG_2019-01-04评价了有没有积分呢,。。

_KINGKANG_2019-01-04评价了有没有积分呢,。。 小懒_2012-07-10对于开发很有帮助,可以快速的找到指令详解。。。

小懒_2012-07-10对于开发很有帮助,可以快速的找到指令详解。。。 paigukai2011-09-08蛮不错的 看不懂汇编的时候可以快速查看

paigukai2011-09-08蛮不错的 看不懂汇编的时候可以快速查看 jobbyjobby2011-09-14好像没有中断相关指令。

jobbyjobby2011-09-14好像没有中断相关指令。 hirofeng892015-06-10资源不错,清晰

hirofeng892015-06-10资源不错,清晰

lc841004

- 粉丝: 2

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【SEC-2025行业研究报告】Form 10-K Blue Owl Credit Income Corp. .pdf

- 【SEC-2025行业研究报告】Form 10-K CEDAR REALTY TRUST, INC. .pdf

- 【SEC-2025行业研究报告】Form 10-K ChromaDex Corp. .pdf

- 【SEC-2025行业研究报告】Form 10-K BRIGHTHOUSE LIFE INSURANCE Co .pdf

- 【SEC-2025行业研究报告】Form 10-K CPI Card Group Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Custom Truck One Source, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Crexendo, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Cyclerion Therapeutics, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Dave Inc. DE .pdf

- 【SEC-2025行业研究报告】Form 10-K Emergent BioSolutions Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Eos Energy Enterprises, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K Evolus, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-K FLAGSTAR FINANCIAL, INC. .pdf

- 【SEC-2025行业研究报告】Form 10-Q NKGen Biotech, Inc. .pdf

- 【SEC-2025行业研究报告】Form 10-Q DONALDSON Co INC .pdf

- 【SEC-2025行业研究报告】Form 10-K Flutter Entertainment plc .pdf

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功