TMS320C54x DSP

CPU 与外设

TMS32 0 C 5 4 x DSP CPU 和 外设

第一章 综 述

1 总线结构

C54x 包括 8 条 16 比特宽度的总线,其中:

一条程序总线(PB)

三条数据总线(CB、DB、EB)

四条地址总线(PAB、CAB、DAB、EAB)

2 CPU

C54x 的 CPU 结构包括:

40 比特的 ALU,其输 入 来 自 16 比 特 立 即数、16 比特来自数据

存储器的数据、暂时存储器、 T 中的 16 比特数、数据存储器中两

个 16 比特字、数据存储器中 32 比特字、累加器中 40 比特字。

2 个 40 比 特的累加器 ,分为三个 部分,保护 位( 39-32 比特)、

高位字(31-16 比特)、低位字(15-0 比特)。

桶型移位器,可产生 0 到 31 比特的左移或 0 到 16 比特的右移。

17×17 比特的乘法器

40 比特的加法器

比较选择和存储单元 CSSU

数据地址产生器 DAGEN

程序地址产生器 PAGEN

3 外设

C54x 包括:

通用 I/O 引脚,XF 和

定时器

PLL 时钟产生器

HPI 口,8 比特或 16 比特

同步串口

带缓存串口,BSP

多路带缓存串口,McBSP

时分复用串口,TDM

可编程等待状态产生器

可编程 bank-switching 模块

外部总线接口

IEEE1149.1 标准 JTAG 口

第二章 存储器

第2页

TMS32 0 C 5 4 x DSP CPU 和 外设

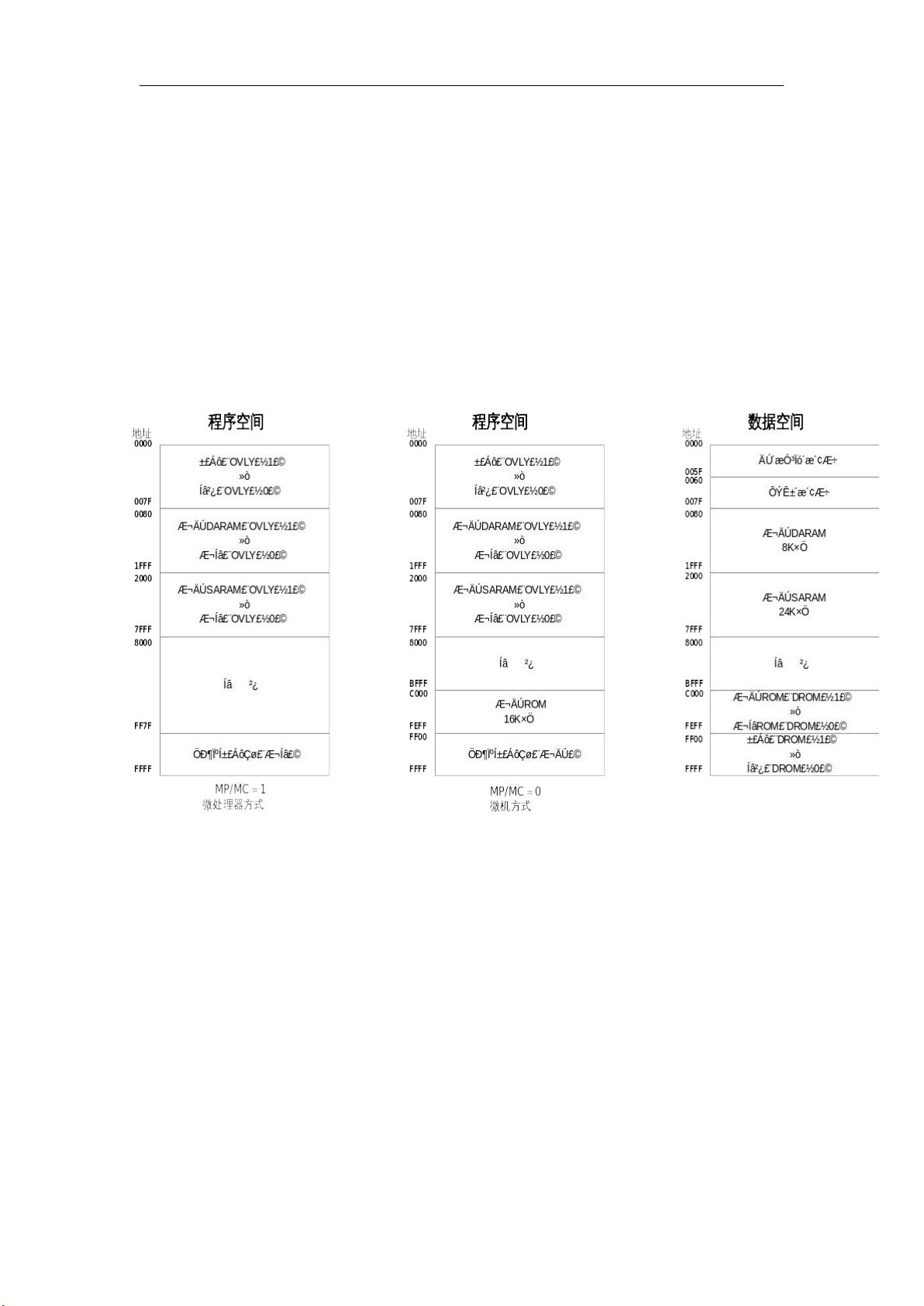

一般而言, C54x 的存储空间可达 192K16 比 特 字 , 64K 程 序 空 间,

64K 数据空间,64KI/O 空间。

依赖其并行的 工艺特性和片 上 RAM 双向访问的性能,在一 个机器周

期内,C54x 可以执行 4 条并行并行存储器操作:取指令,两操作数读,

一操作数写。

使用片内存储器有三个优点:高速执行(不需要等待),低开销,低

功耗。

1 存储空间分配图(以 C549 为例)

复位后,中断 矢量表位于程 序区 FF80H 位 置,可重新定 位于程序空

间任何 一个 128 字的页面 (其地址高 9 比 特即页号由 PMST 中 IPTR 确

定)。

2 程序存储区

C54x 有片内 ROM、DARAM 、SARAM ,这些区域可以 通过软件配

置到程序空间。当地址落在这些区域内,自动对这些区域进行访问;当地

址落在这些区域以外,自动产生对外部存储器的访问。

2.1 片内 ROM

片内 ROM(4K,16K,24K,28K 或 48K 字)可能包括的内容有:

引导程序,可以从串口、外部存储器、I/O 口或 HPI 口引导

256 字的 μ 率扩展表

256 字的 A 率扩展表

256 字的正弦表

第3页

TMS32 0 C 5 4 x DSP CPU 和 外设

中断矢量表

2.2 扩展程序存储器

‘548、’549、’ 5410、’5420 采用分页扩展的方式使可寻址程序空间

达到 8192K 字。这一功能的实现有赖于:

23 条地址线

扩展程序计数器 XPC

6 条访问外部程序空间的指令

当程序 空间可以使用 片内 RAM 时,程序 空间的每一页 分为以下两部

分:最大 32K 字的通用块和 32K 字的专有块。通用块为所有页共享。

XPC 寄存器指 示选定页, 复位后,初 始化为 0 。影响 XPC 的 6 条指

令是:

FB[D]-长跳转指令

FBACC[D]-长跳转指令,跳转地址由 A 或 B 中内容确定

FCAL A[D]-长调用指令,子程序地址由 A 或 B 中内容确定

FCALL[D]-长调用指令

FRET[D]-长返回指令

FRETE[D]-长中断返回指令

其它的指令不修改 XPC 寄存器,而在当前页中做内部访问。

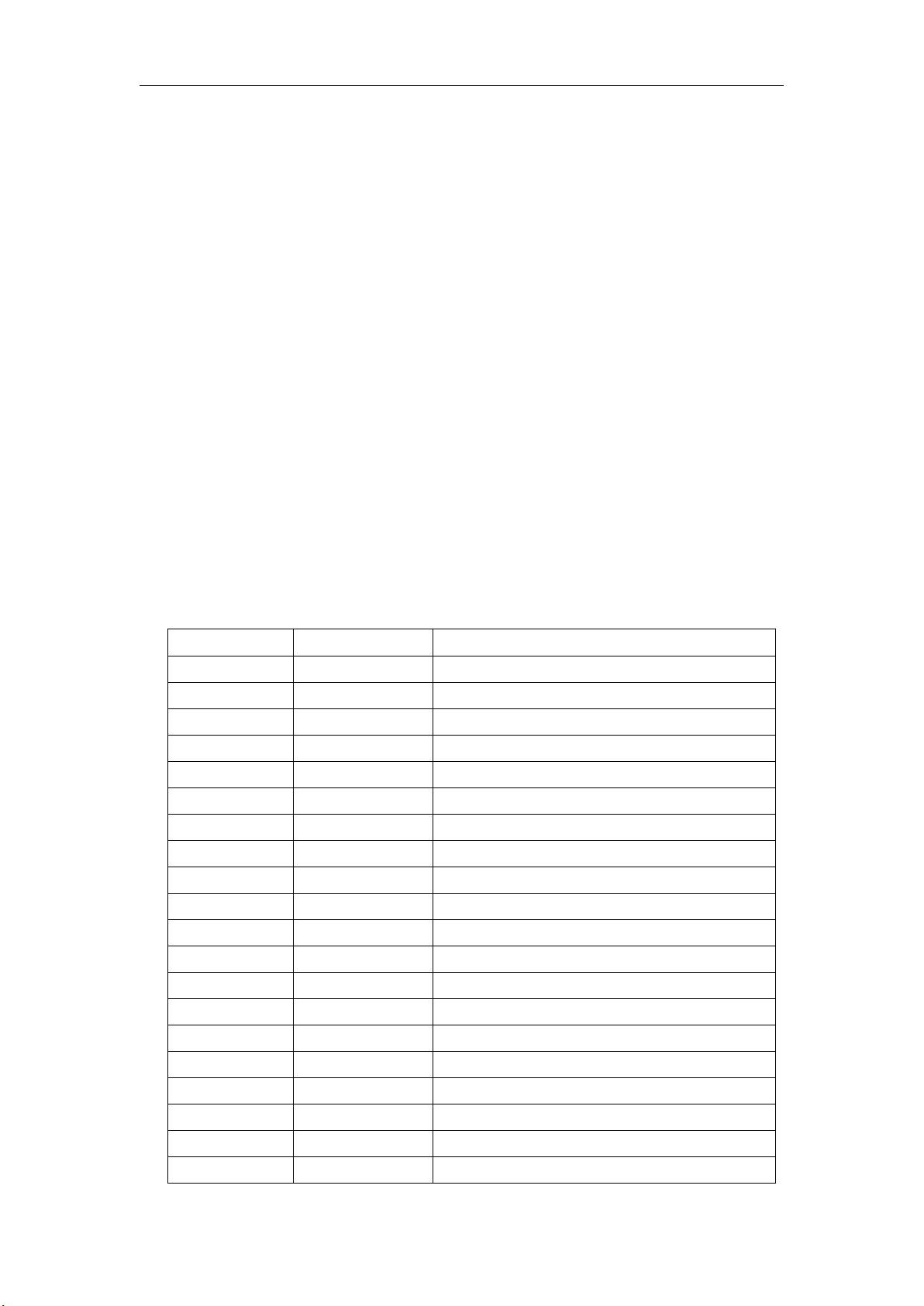

3 内存映象寄存器(以‘549 为例)

0 IMR

中断屏蔽寄存器

1 IFR

中断标志寄存器

2-5 -

测试保留

6 ST0

状态寄存器 0

7 ST1

状态寄存器 1

8 AL

累加器 A 低字(15-0 比特)

9 AH

累加器 A 高字(31-16 比特)

A AG

累加器 A 保护位(39-32 比特)

B BL

累加器 B 低字(15-0 比特)

C BH

累加器 B 高字(31-16 比特)

D BG

累加器 B 保护位(39-32 比特)

E T

乘法寄存器

F TRN

传送寄存器

10-17 AR0-AR7

辅助寄存器 ARn n=0~7

18 SP

堆栈指针

19 BK

循环缓存区大小寄存器

1A BRC

块重复计数器

1B RSA

块重复开始地址

1C REA

块重复结束地址

1D PMST

状态寄存器

1E XPC

PC 扩展寄存器

第4页