x9241资料 能够更亲清楚的了解芯片的功能。

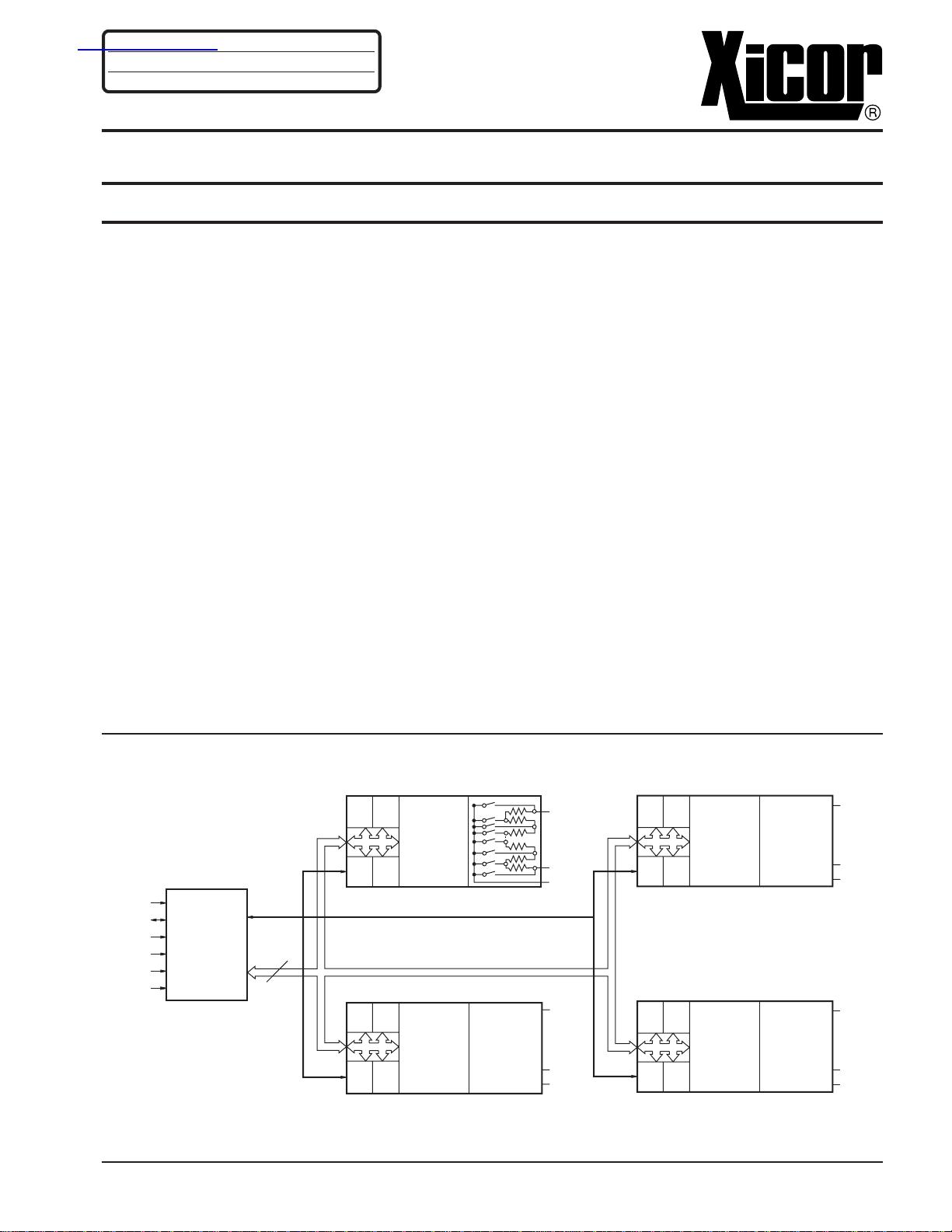

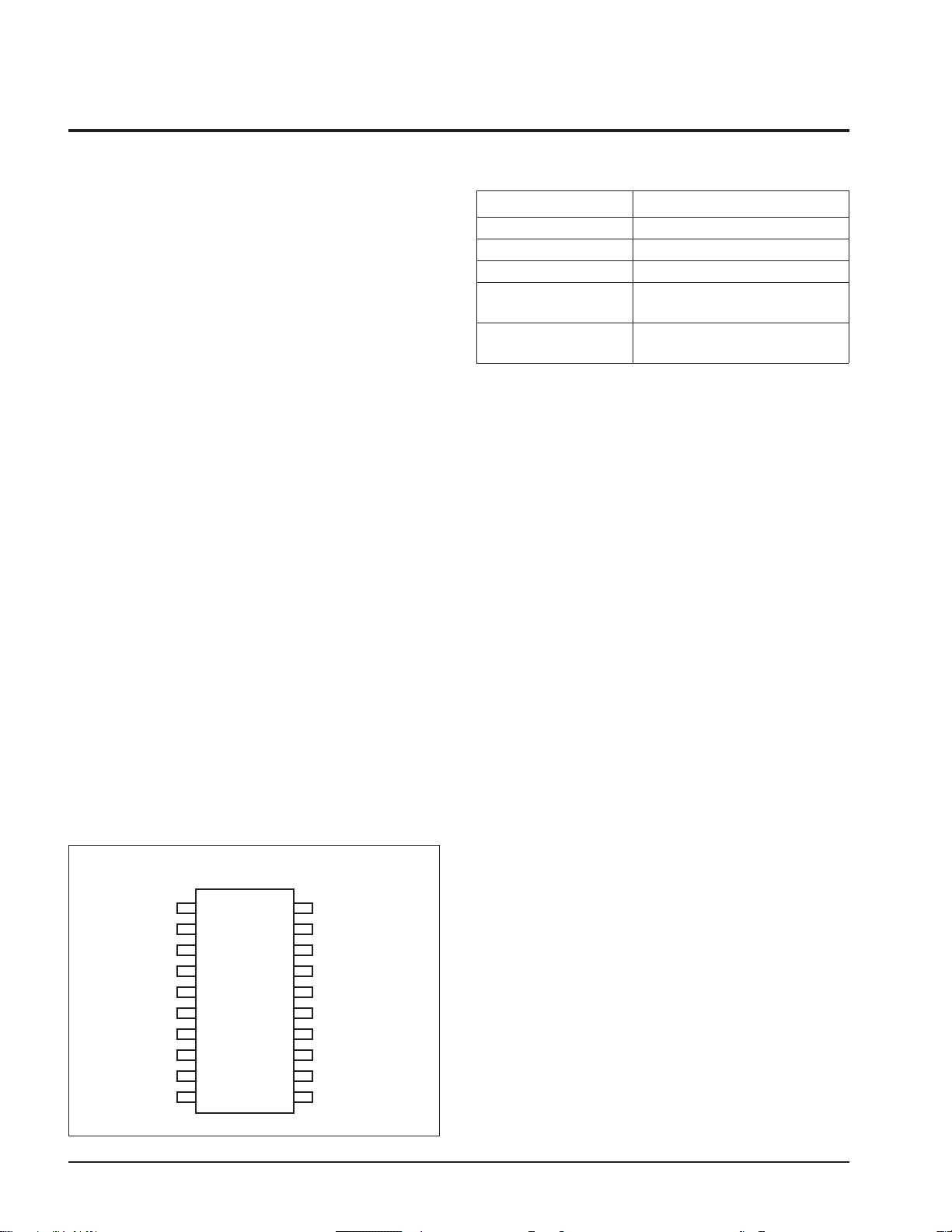

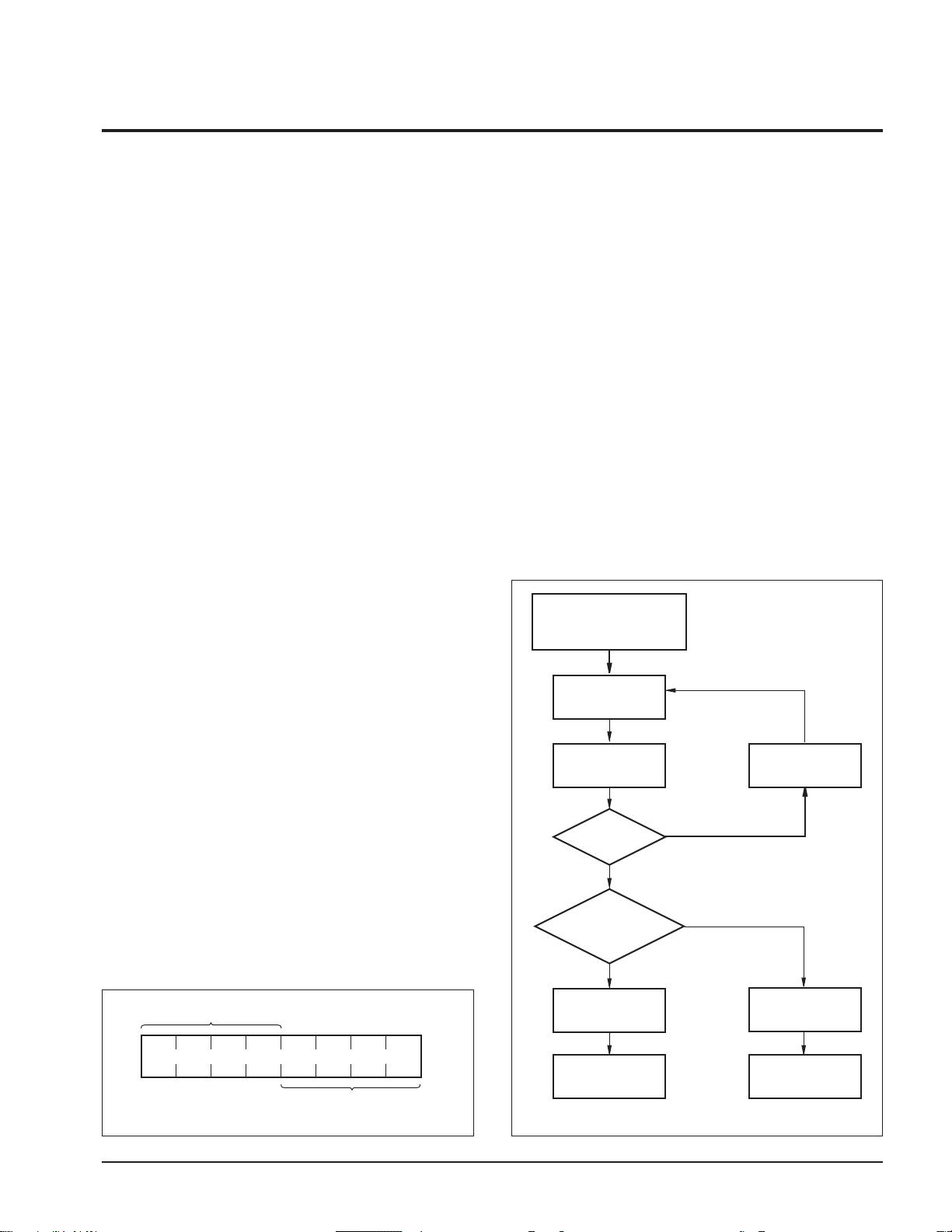

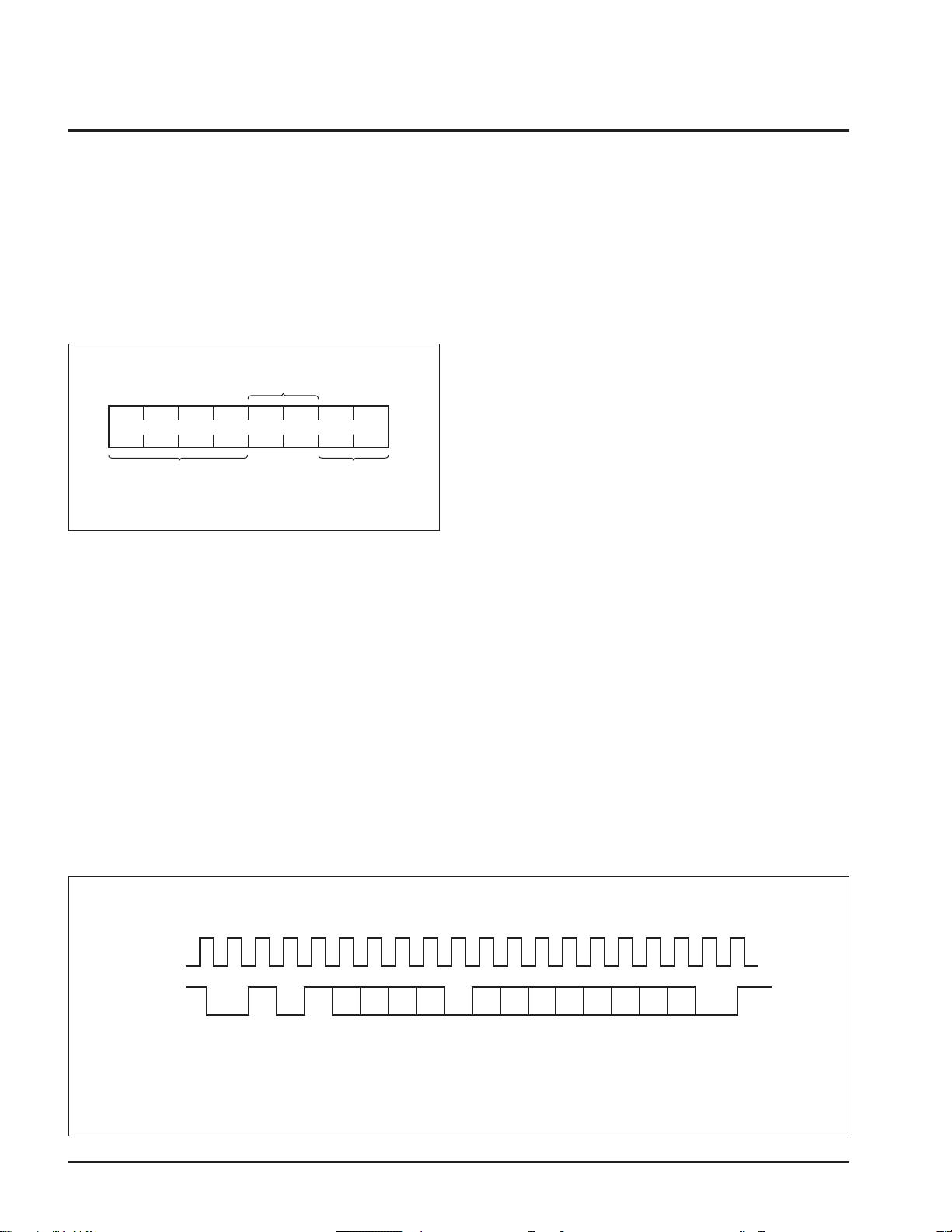

### X9241 芯片功能及应用解析 #### 概述 X9241 是一款集成四个非易失性数字电位器(E2POT™)的单片 CMOS 微电路。该芯片具备低功耗、高可靠性的特点,并通过两线串行接口进行数据交互。其独特的设计使其能够在多种电子设备中实现灵活的电阻控制。 #### 主要特性 - **四合一集成**:X9241 在一个封装内集成了四个 E2POT 数字电位器。 - **两线串行接口**:支持通过两线接口进行数据传输。 - **寄存器导向格式**:用户可以直接写入或读取电位器位置,并且每个电位器最多可以存储四个位置。 - **快速指令格式**:能够快速将寄存器内容转移到电阻阵列中,支持阵列级联。 - **低功耗 CMOS 技术**:采用低功耗 CMOS 工艺制造,适用于便携式或电池供电设备。 - **持久存储能力**:每个寄存器可承受 10 万次数据变化,数据保留时间长达 100 年。 - **内置 E2PROM 存储**:拥有 16 字节的 E2PROM 内存用于存储配置数据。 - **多值电阻阵列**:提供三种电阻值(2KΩ 至 50KΩ 可编程),通过级联可扩展至 500Ω 至 200KΩ 的范围。 - **高分辨率**:每个电位器具有 64 档位调节能力。 - **多种封装形式**:提供 20 引脚塑料 DIP、20 引脚 TSSOP 和 20 引脚 SOIC 封装。 #### 功能描述 X9241 集成有四个电阻阵列,每个阵列由 63 个电阻元件组成,两端各有一个可访问触点。电位器的位置可通过两线串行接口进行控制。 每个电阻阵列与一个擦除计数器寄存器(Wiper Counter Register, WCR)和四个 8 位数据寄存器关联。用户可以直接读写这些寄存器。擦除计数器寄存器的内容控制电位器在电阻阵列上的位置。数据寄存器的内容可以转移至擦除计数器寄存器来改变电位器的位置,当前的电位器位置也可以保存到任意一个数据寄存器中。 此外,这些电阻阵列可以通过级联形成更多档位的电阻元件,如 127、190 或 253 档位。 #### 应用示例 X9241 芯片广泛应用于需要精确控制电阻值的场景,例如: - **音频设备**:用于音量控制、均衡器设置等。 - **工业控制**:如传感器校准、电源管理等。 - **汽车电子**:如仪表盘亮度调节、座椅位置记忆等功能。 - **消费电子产品**:如智能手机中的音量控制、智能家居设备中的亮度调节等。 #### 接口与控制电路 X9241 提供了一个简洁的两线串行接口,包括 SCL(时钟线)和 SDA(数据线)。通过这个接口,用户可以轻松地对寄存器进行读写操作,并调整电位器的位置。 #### 结论 X9241 作为一款先进的数字电位器芯片,凭借其高集成度、灵活性和可靠性,在众多领域中发挥着重要作用。无论是对于硬件工程师还是电子爱好者来说,掌握这款芯片的工作原理和应用技巧都将是非常有价值的。

剩余15页未读,继续阅读

acp15436570012012-08-23资料比较详细,可以参考。。。

acp15436570012012-08-23资料比较详细,可以参考。。。

- 粉丝: 1

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功