没有合适的资源?快使用搜索试试~ 我知道了~

详细介绍了该模块各项功能及原理,原版的英文资料。

资源推荐

资源详情

资源评论

1997 Microchip Technology Inc. DS21222A-page 1

M

24LC01B/02B MODULES

FEATURES

• ISO 7816 Compliant pad locations

• Low power CMOS technology

- 1 mA active current typical

- 10

µ

A standby current typical at 5.5V

• Organized as a single block of 128 bytes (128 x 8)

or 256 bytes (256 x 8)

• 2-wire serial interface bus, I

2

C™ compatible

• 100 kHz (2.5V) and 400 kHz (5V) compatibility

• Self-timed write cycle (including auto-erase)

• Page-write buffer for up to 8 bytes

• 2 ms typical write cycle time for page-write

• ESD protection > 4 kV

• 1,000,000 E/W cycles guaranteed

• Data retention > 200 years

• Temperature ranges available:

DESCRIPTION

The Microchip Technology Inc. 24LC01B and 24LC02B

are 1K-bit and 2K-bit Electrically Erasable PROMs in

ISO modules for smart card applications. The devices

are organized as a single block of 128 x 8-bit or 256 x

8-bit memory with a two-wire serial interface. The

24LC01B and 24LC02B also have page-write capabil-

ity for up to 8 bytes of data.

ISO MODULE LAYOUT

BLOCK DIAGRAM

- Commercial (C): 0

°

C to +70

°

C

VSS

SDA

SCL

V

DD

HV GENERATOR

EEPROM

ARRAY

PAGE LATCHES

YDEC

XDEC

SENSE AMP

R/W CONTROL

MEMORY

CONTROL

LOGIC

I/O

CONTROL

LOGIC

SDA SCL

VCC

VSS

1K/2K I

2

C

™

Serial EEPROMs in ISO Micromodules

24LC01B/02B Modules

DS21222A-page 2

1997 Microchip Technology Inc.

1.0 ELECTRICAL CHARACTERISTICS

1.1 Maxim

um Ratings*

V

CC

...................................................................................7.0V

All inputs and outputs w.r.t. V

SS

................-0.6V to V

CC

+1.0V

Storage temperature ..................................... -65˚C to +150˚C

Ambient temp. with power applied................. -65˚C to +125˚C

ESD protection on all pads.............................................

≥

4 kV

*Notice:

Stresses above those listed under “Maximum ratings”

may cause permanent damage to the device. This is a stress rat-

ing only and functional operation of the device at those or any

other conditions above those indicated in the operational listings

of this specification is not implied. Exposure to maximum rating

conditions for extended periods may affect device reliability.

TABLE 1-1: PAD FUNCTION TABLE

1.2 P

ad Descriptions

1.2.1 SDA (Serial Data)

This is a bi-directional pad used to transfer addresses

and data into and data out of the device. It is an open

drain terminal, therefore the SDA bus requires a pull-up

resistor to V

CC

(typical 10 K

Ω

for 100 kHz, 2 K

Ω

for

400 kHz).

For normal data transfer SDA is allowed to change only

during SCL low. Changes during SCL high are reserved

for indicating the START and STOP conditions.

1.2.2 SCL (Serial Clock)

This input is used to synchronize the data transfer from

and to the device.

Name Function

V

SS

SDA

SCL

V

CC

Ground

Serial Address/Data I/O

Serial Clock

+2.5V to 5.5V Power Supply

TABLE 1-1 DC CHARACTERISTICS

All Parameters apply across the recom-

mended operating ranges unless other-

wise noted.

Commercial (C): Tamb = 0˚C to +70˚C, V

CC

= 2.5V to 5.5V

Parameter Symbol Min. Max. Units Conditions

SCL and SDA pins:

High level input voltage V

IH

0.7 V

CC

V (Note)

Low level input voltage V

IL

0.3 V

CC

V (Note)

Hysteresis of Schmitt trigger inputs V

HYS

0.05 V

CC

— V Vcc

≥

2.5V (Note)

Low level output voltage V

OL

0.40 V I

OL

= 3.0 mA, V

CC

= 4.5V

I

OL

= 2.1 mA, V

CC

= 2.5V

Input leakage current I

LI

-10 10

µ

A V

IN

= V

CC

or V

SS

Output leakage current I

LO

-10 10

µ

A V

OUT

= V

CC

or V

SS

Pin capacitance (all inputs/outputs) C

IN

,

C

OUT

— 10 pF V

CC

= 5.0V (Note)

Tamb = 25˚C, f = 1 MHz

Operating current I

CC

Write — 3 mA V

CC

= 5.5V, SCL = 400 kHz

I

CC

Read — 1 mA V

CC

= 5.5V, SCL = 400 kHz

Standby current I

CCS

— 100

µ

A V

CC

= 5.5V, SDA = SCL = V

CC

Note:

This parameter is periodically sampled and not 100% tested.

24LC01B/02B Modules

1997 Microchip Technology Inc. DS21222A-page 3

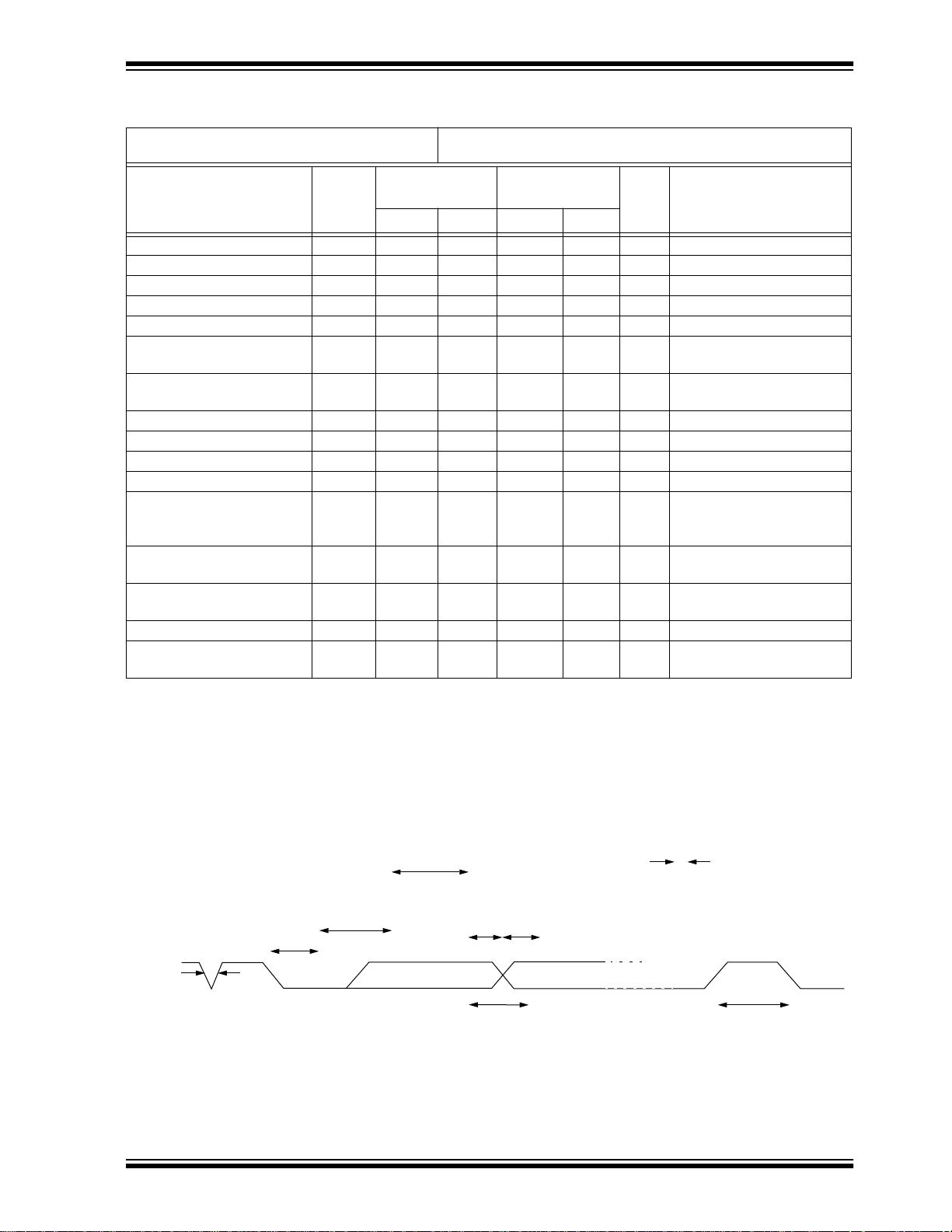

TABLE 1-2 AC CHARACTERISTICS

FIGURE 1-1: BUS TIMING DATA

All parameters apply across the specified operat-

ing ranges unless otherwise noted.

Vcc = 2.5V to 5.5V

Commercial (C): Tamb = 0

°

C to +70

°

C

Parameter Symbol

Vcc = 2.5V - 5.5V

STD MODE

Vcc = 4.5V - 5.5V

FAST MODE

Units Remarks

Min. Max. Min. Max.

Clock frequency F

CLK

— 100 — 400 kHz

Clock high time T

HIGH

4000 — 600 — ns

Clock low time T

LOW

4700 — 1300 — ns

SDA and SCL rise time T

R

— 1000 — 300 ns (Note 1)

SDA and SCL fall time T

F

— 300 — 300 ns (Note 1)

START condition hold time T

HD

:

STA

4000 — 600 — ns After this period the first

clock pulse is generated

START condition setup time T

SU

:

STA

4700 — 600 — ns Only relevant for repeated

START condition

Data input hold time T

HD

:

DAT

0 — 0 — ns (Note 2)

Data input setup time T

SU

:

DAT

250 — 100 — ns

STOP condition setup time T

SU

:

STO

4000 — 600 — ns

Output valid from clock T

AA

— 3500 — 900 ns (Note 2)

Bus free time T

BUF

4700 — 1300 — ns Time the bus must be free

before a new transmission

can start

Output fall time from V

IH

minimum to V

IL

maximum

T

OF

— 250 20 +0.1

C

B

250 ns (Note 1), C

B

≤

100 pF

Input filter spike suppression

(SDA and SCL pins)

T

SP

— 50 — 50 ns (Notes 1, 3)

Write cycle time T

WC

— 10 — 10 ms Byte or Page mode

Endurance 1M — 1M — cycles 25

°

C, V

CC

= 5.0V, Block

Mode (Note 4)

Note 1:

Not 100% tested. C

B

= total capacitance of one bus line in pF.

2:

As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region

(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3:

The combined T

SP

and V

HYS

specifications are due to Schmitt trigger inputs which provide improved noise

spike suppression. This eliminates the need for a TI specification for standard operation.

4:

This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific

application, please consult the Total Endurance Model which can be obtained on our BBS or website.

剩余11页未读,继续阅读

资源评论

jennygoo

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Python 程序语言设计模式思路-行为型模式:职责链模式:将请求从一个处理者传递到下一个处理者

- 9241703124789646.16健身系统2.apk

- postgresql-16.3-1-windows-x64.exe

- Python 程序语言设计模式思路-结构型模式:装饰器讲解及利用Python装饰器模式实现高效日志记录和性能测试

- 基于YOLOv5和DeepSORT的多目标跟踪仿真与记录

- Python 程序语言设计模式思路-创建型模式:原型模式:通过复制现有对象来创建新对象,面向对象编程

- 卸载软件geek卸载软件geek

- Python 程序语言设计模式思路-创建型模式:单例模式,确保一个类的唯一实例(装饰器)面向对象编程、继承

- skywalking-plugins.jar skywalking-alarm.jar

- 独栋别墅图纸D020-两层-10.00&11.00米- 施工图.dwg

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功