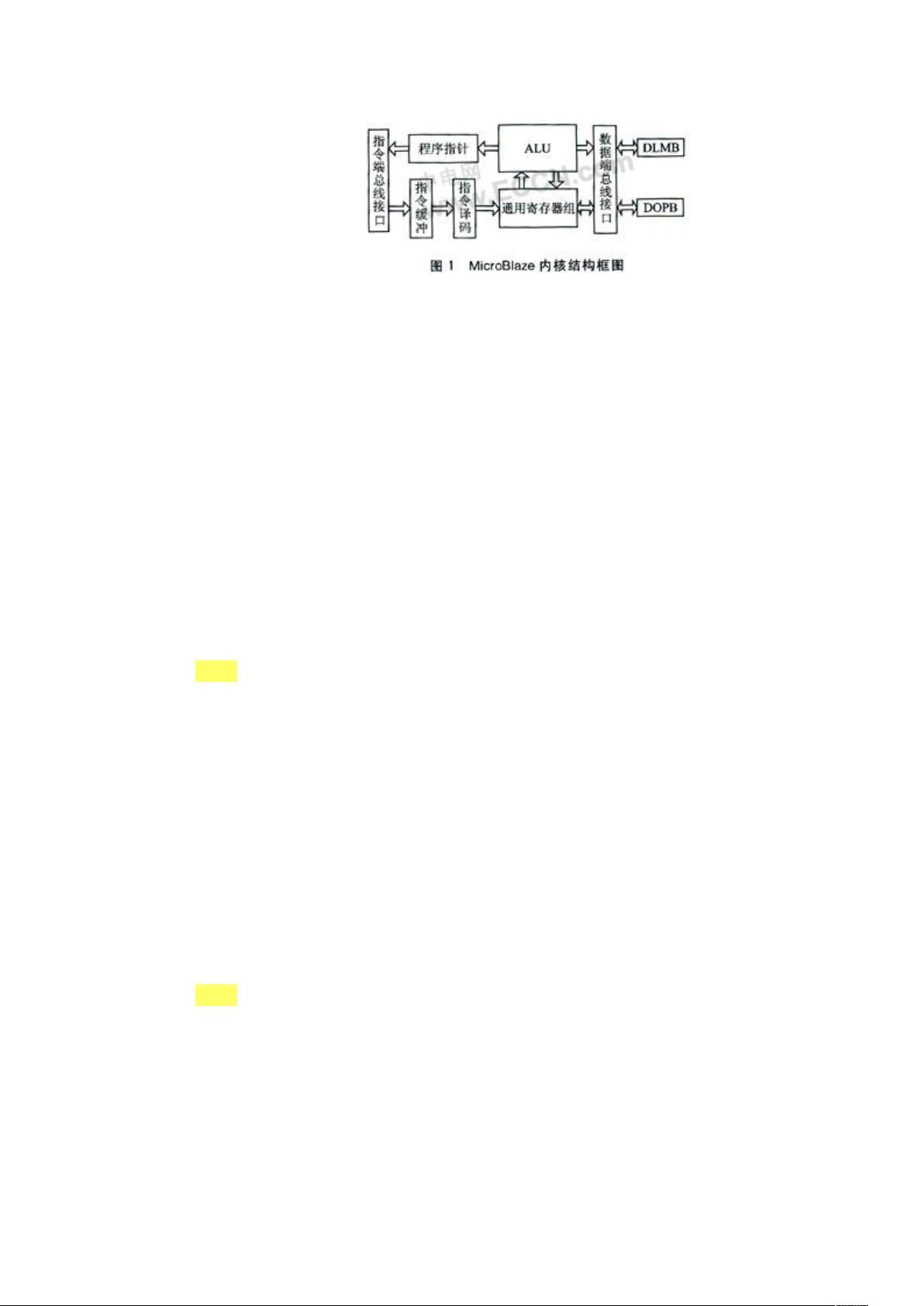

### 基于FSL总线的UART外设IP核设计 #### 引言与背景 在嵌入式系统设计领域,特别是在Xilinx FPGA平台上,MicroBlaze软核处理器因其高性能与灵活性,成为构建可编程系统芯片(SOPC)的理想选择。然而,将用户自定义的IP核整合至MicroBlaze系统时,需考虑不同总线接口的适用性。OPB总线适合低速设备,而FSL总线则专为高速、高性能的IP核设计,以实现硬件加速。鉴于Xilinx官方未提供基于FSL总线的UART IP核,本文旨在探讨基于FSL总线的UART外设设计,以满足高速系统中对时间敏感的应用需求。 #### MicroBlaze体系结构 ##### 内核结构 MicroBlaze采用32位RISC架构,拥有哈佛结构的指令和数据总线,能以150MHz的时钟频率运行,提供125 DMIPS的性能,特别适用于网络、电信及数据通信领域的复杂嵌入式系统设计。其内核结构集成了多种功能单元,确保了高效的数据处理与存储访问能力。 ##### 总线接口 MicroBlaze处理器软核具备多种总线接口,包括OPB、LMB、FSL、XCL及MDM接口。其中,FSL总线是MicroBlaze特有的一种基于FIFO的单向链路,用于实现用户自定义IP核与处理器内部寄存器的高速直连,显著提升了数据交换速率。 #### 基于FSL总线的UART IP核设计 ##### UART简介 UART(Universal Asynchronous Receiver/Transmitter)是一种广泛应用于串行数据传输的协议,支持全双工通信,常见于RS232-C异步串行接口。传统的UART器件,如8250、8251、NS16450,虽功能齐全,但集成度高,可能包含不必要的辅助模块,如FIFO,对于某些应用场景来说显得冗余。利用FPGA的可编程特性,可以将UART的核心功能定制化,实现更紧凑、稳定的设计。 ##### FSL总线接口特性 FSL总线作为一种高速点对点通信总线,采用非共享、无仲裁的通信机制,支持控制位与数据的分离传输,基于FIFO模式,数据宽度可配置,通信速度最高可达600MHz,是实现高速数据交互的理想选择。 ##### UART硬件设计要点 设计基于FSL总线的UART IP核,关键在于构建UART模块与MicroBlaze之间的通信桥梁。此设计不仅需涵盖UART的基本功能,如数据总线接口、控制逻辑、波特率发生器、发送与接收部件,还需重点优化与FSL总线的接口设计,确保UART能够充分利用FSL总线的高速特性,实现高效的数据传输。相较于基于OPB总线的UART,基于FSL总线的设计将显著提升UART在高速系统中的性能表现。 基于FSL总线的UART外设IP核设计,是针对嵌入式系统中高速数据通信需求的重要解决方案。它不仅弥补了Xilinx官方IP库的空白,更为设计者提供了在MicroBlaze平台上实现高效、定制化UART功能的可能。随着嵌入式系统对实时性和数据吞吐量要求的不断提升,此类设计的重要性将愈发凸显。

剩余7页未读,继续阅读

- 粉丝: 4

- 资源: 15

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 自动折盒贴标机sw16可编辑全套技术资料100%好用.zip

- 平安夜祝福+圣诞树代码,巨漂亮,心动

- 基于Springboot+Vue健身房管理系统源码+数据库+视频教程+文档

- 用户登录数据库SQL,用户登录数据库

- 300元花钱买来的一款企业发卡程序源码+短链接+二维码修复(站长亲测)

- Java毕业设计-基于Springboot+Vue健身房管理系统源码+数据库+视频教程+文档

- 基于springboot+vue的健身管理平台源码+数据库+视频教程+文档

- Java毕业设计-基于springboot+vue的健身管理平台源码+数据库+视频教程+文档

- C#常用工具类源代码(Excel操作类 FTP操作类 JSON操作类等等)

- 多线程扫描文件夹下的文件

- HENU河南大学 计算机学院 计网期末复习知识点

- CNC封闭式自动化上下料设备step全套技术资料100%好用.zip

- 伺服电机驱动机械臂step全套技术资料100%好用.zip

- 用户登录界面,验证成功界面,数据库

- 侧吸式油烟机sw16可编辑全套技术资料100%好用.zip

- 新界面企业版自动售卡发卡平台系统网站源码对接易支付接口

信息提交成功

信息提交成功