没有合适的资源?快使用搜索试试~ 我知道了~

HC31_T7_Pulp.pdf

资源推荐

资源详情

资源评论

2

Integrated Systems Laboratory

1

Department of Electrical, Electronic

and Information Engineering

RISC-V Tutorial at HotChips 2019 18 Aug 2019

Fabian Schuiki

and the entire PULP team

pulp-platform.org

The Parallel Ultra Low Power Platform

Project started in 2013 by Luca Benini

A collaboration between University of Bologna and ETH Zürich

Large team. In total we are about 60 people, not all are working on PULP

Key goal is

We were able to start with a clean slate, no need to remain compatible

to legacy systems.

Parallel Ultra Low Power (PULP)

How to get the most BANG

for the ENERGY consumed

in a computing system

Our research was not developing processors…

… but we needed good processors for systems we build for research

Initially (2013) our options were

Build our own (support for SW and tools)

Use a commercial processor (licensing, collaboration issues)

Use what is openly available (OpenRISC,.. )

We started with OpenRISC

First chips until mid-2016 were all using OpenRISC cores

We spent time improving the microarchitecture

Moved to RISC-V later

Larger community, more momentum

Transition was relatively simple (new decoder)

How we started with open source processors

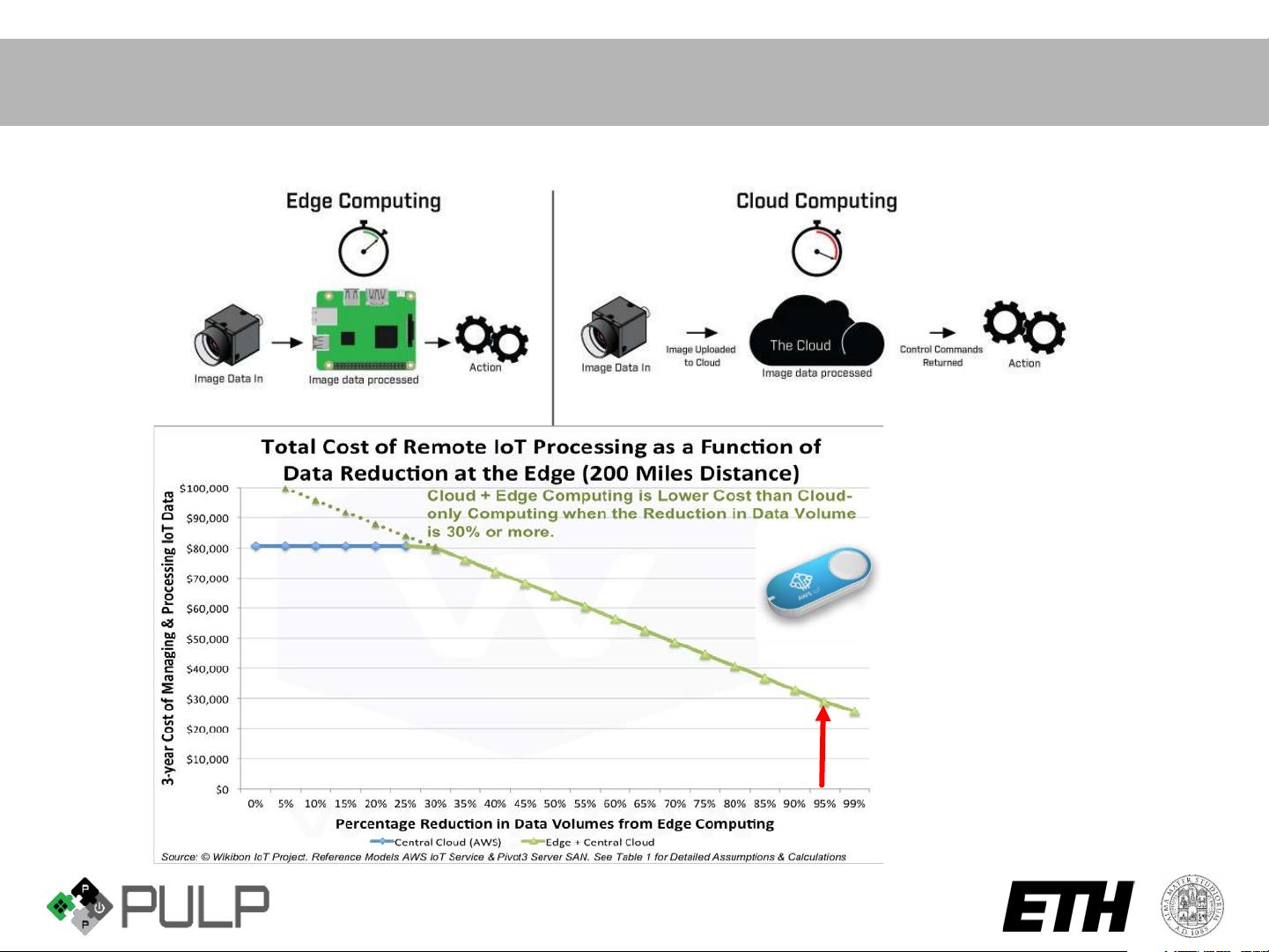

Motivation: Cloud Edge Extreme Edge AI

4

3x Cost reduction if data

volume is reduced by 95%

Latency,

Privacy

Cost

Extreme edge AI

challenge:

• AI capabilities

below 1 pJ/op

(MCU power

envelope)

• Mops to Tops

• Beyond fp32/fp64

2013: Parallel Ultra Low Power PULP!

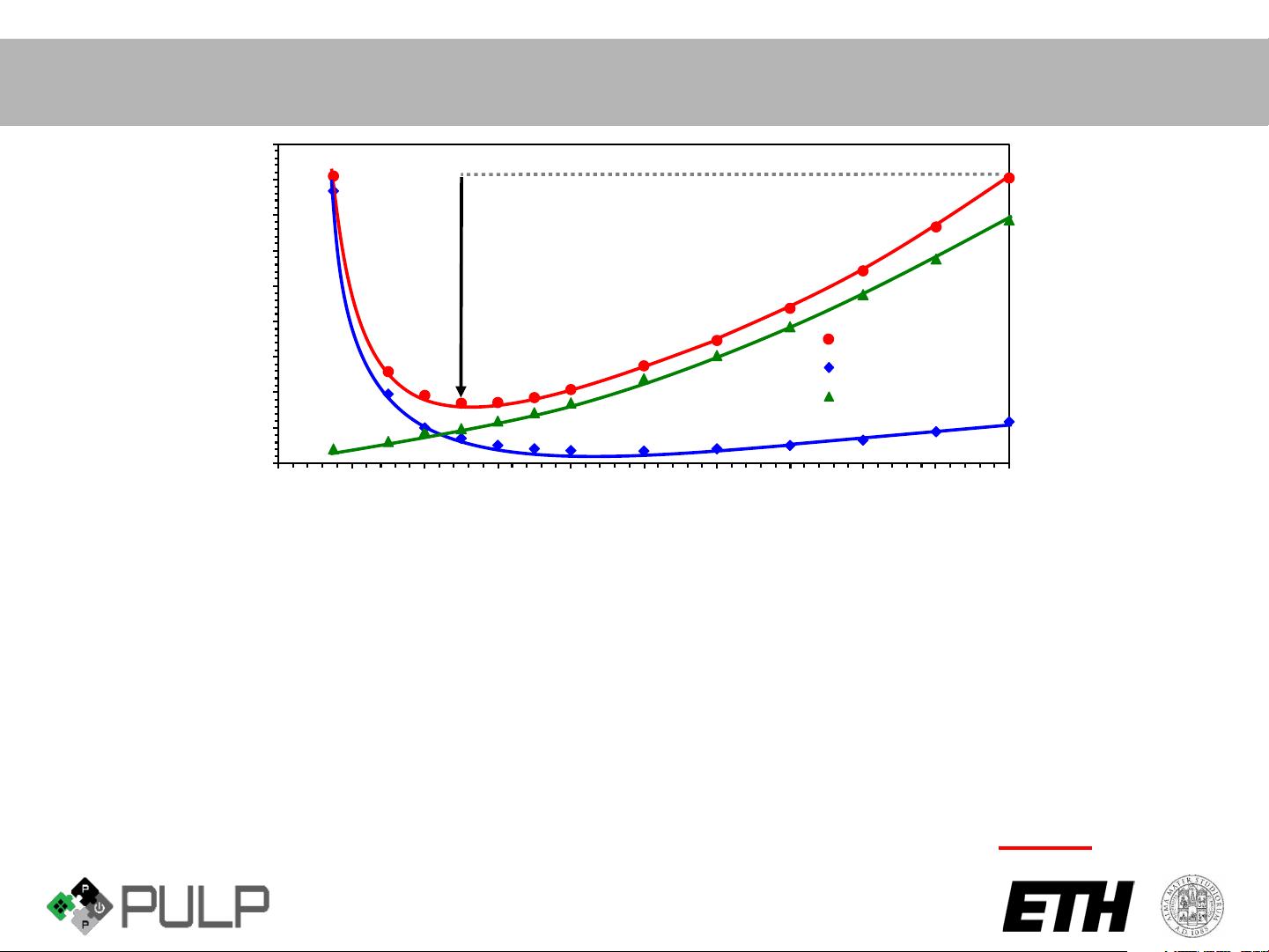

5

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2

Total Energy

Leakage Energy

Dynamic Energy

0.55 0.55 0.55 0.55 0.6 0.7 0.8 0.9 1 1.1 1.2

Energy/Cycle (nJ)

32nm CMOS, 25

o

C

4.7X

Logic Vcc / Memory Vcc (V)

Source: Vivek De, INTEL – Date 2013

Near-Threshold Computing (NTC):

1. Don’t waste energy pushing devices in strong inversion

2. Recover performance with parallel execution

3. Core with ‘naked’ L1 interface to create cluster coupled at L1 level

4. Manage Leakage, PVT variability and SRAM limiting NT!

Need Strong ISA, Need full access to “deep” core interfaces, need to tune pipeline!

OPEN ISA: RISC-V RV32IMC + New, Open Microarchitecture RI5CY!

剩余58页未读,继续阅读

资源评论

iiiiiiicer

- 粉丝: 1

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功