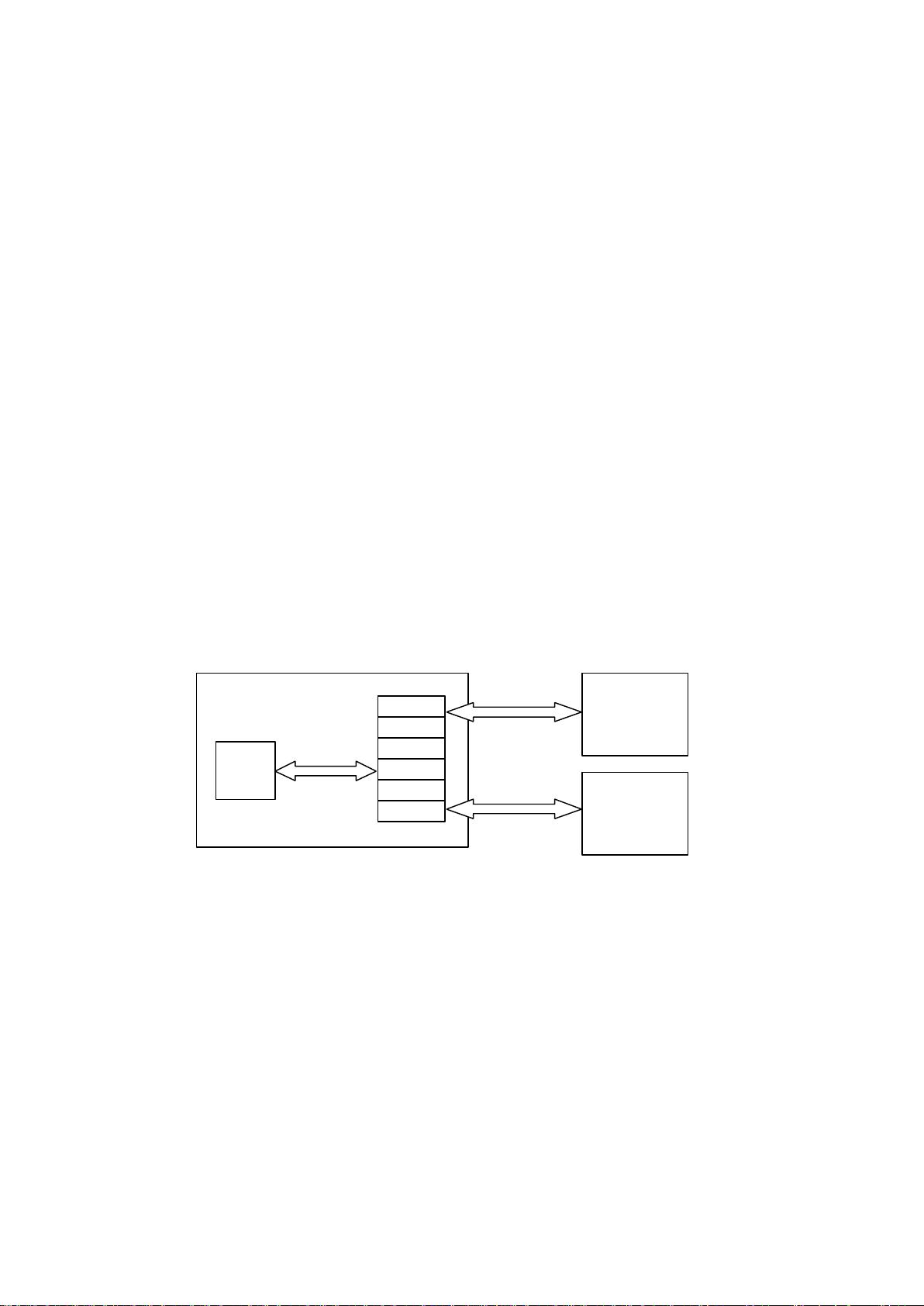

我将一个具有实时任务切换功能的小型嵌入式操作系统内核成功的从具有ARM7内核的ADUC7024芯片移植到了具有cortex内核的LM3S8962芯片,然而在移植到同样具有cortex内核的STM32F103VB芯片上却出了问题,程序运行一段时间就跑飞,最终查明是任务切换过程破坏了cortex内核的中断机制所致,但为何同样采用了cortex内核的LM3S8962芯片却没有出现该问题?本文将向你讲述这其中的原因,同时你还可以了解到操作系统任务切换的基本原理以及cortex中断方面的一些知识。 ### 破坏STM32中断机制引发的异常 #### 现象描述与问题背景 在本案例中,一位开发者成功地将一个具备实时任务切换功能的小型嵌入式操作系统内核从ARM7内核的ADUC7024芯片移植到了Cortex内核的LM3S8962芯片上,但在进一步尝试将其移植至同样采用Cortex内核的STM32F103VB芯片时遇到了问题:程序在运行一段时间后出现了异常行为,最终问题定位为任务切换过程中破坏了Cortex内核的中断机制。 值得注意的是,在LM3S8962芯片上并未出现同样的问题,这引发了进一步的思考:同样是Cortex内核,为何在不同芯片上表现不同? 为了解决这个问题,首先需要理解操作系统任务切换的基本原理以及Cortex中断的相关知识。 #### 实时嵌入式操作系统任务切换原理 在嵌入式设备中,程序通常存储在ROM中,运行时可能直接在ROM中执行或被搬移到RAM中执行。无论哪种情况,程序执行过程中都需要使用芯片内的寄存器,这些寄存器用于存放运行时所需的数据,并指示芯片状态。寄存器距离内核最近,访问速度最快,支持更多的寻址方式,因此程序执行过程中的大部分操作都依赖于这些寄存器。 芯片通过寄存器执行程序空间中的指令,不断地将临时数据从寄存器存储到数据空间,再从数据空间读取临时数据回寄存器参与计算,这一过程构成了程序的运行流程。任务切换的本质即为将当前任务的寄存器数据保存到数据空间,然后从数据空间恢复下一个任务的数据到寄存器中,以此实现任务间的上下文切换。 #### Cortex中断机制详解 在Cortex内核中,中断处理机制是确保系统稳定性和响应实时性的关键。当硬件定时器产生的tick中断到达时,操作系统会产生调度信号,触发寄存器的备份与恢复操作,进而完成任务之间的切换。而对于非tick中断(如外部中断等),虽然不需要触发任务切换,但中断发生时同样会触发寄存器的备份与恢复操作。 Cortex内核在中断发生时,硬件会自动将特定寄存器(XPSR、PC、LR、R12、R3、R2、R1和R0)压入栈中,而其他寄存器(如R4~R11、LR、XPSR)则需要由C编译器进行备份。这种差异源于AAPCS(Procedure Call Standard for the ARM Architecture)标准的规定,该标准定义了函数调用过程中寄存器的使用规则,特别是R0~R3和R12作为接口寄存器,用于父函数向子函数传递参数。为了避免破坏这些寄存器中的数据,C编译器需要在中断服务程序中对所有寄存器进行备份后再使用。 #### STM32中断机制分析 STM32系列微控制器基于Cortex-M内核设计,拥有强大的中断处理能力。在STM32中断机制中,当发生中断时,硬件会自动备份一部分寄存器(如上所述的XPSR、PC、LR、R12、R3、R2、R1和R0)。其余寄存器则需要通过C编译器进行备份。这一机制确保了在中断服务程序执行过程中不会破坏原有的寄存器内容,从而保证了程序的正常运行。 ### 问题根源及解决方案 根据上述分析,STM32F103VB芯片上出现的任务切换问题可能是因为在任务切换过程中未能正确处理中断机制中的寄存器备份与恢复,导致中断处理不当。与LM3S8962相比,两者虽然都基于Cortex内核,但在具体实现细节上可能存在差异,例如中断处理机制的不同配置或寄存器管理策略的不同。 解决这一问题的关键在于确保任务切换过程中所有必要的寄存器都能被正确地备份与恢复。这可能涉及到对中断服务程序的修改,确保在中断发生时能够完整地保存所有关键寄存器的内容,以及在中断退出时能够准确恢复这些内容。此外,还需要检查操作系统内核与STM32F103VB芯片特性的兼容性,确保任务切换逻辑与芯片硬件特性相匹配。 深入理解Cortex中断机制和STM32的具体实现细节是解决问题的基础。通过仔细分析和适当调整,可以有效地避免此类问题的发生,确保嵌入式系统的稳定性和可靠性。

- 粉丝: 129

- 资源: 27

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功