RapidIO.org

3.2, 1/2016

© Copyright RapidIO.org

RapidIO

™

Interconnect Specification

Part 1: Input/Output Logical

Specification

RapidIO.org

NO WARRANTY. RAPIDIO.ORG PUBLISHES THE SPECIFICATION “AS IS”. RAPIDIO.ORG MAKES NO WARRANTY,

REPRESENTATION OR COVENANT, EXPRESS OR IMPLIED, OF ANY KIND CONCERNING THE SPECIFICATION, INCLUDING,

WITHOUT LIMITATION, NO WARRANTY OF NON INFRINGEMENT, NO WARRANTY OF MERCHANTABILITY AND NO

WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE. USER AGREES TO ASSUME ALL OF THE RISKS ASSOCIATED WITH

ANY USE WHATSOEVER OF THE SPECIFICATION. WITHOUT LIMITING THE GENERALITY OF THE FOREGOING, USER IS

RESPONSIBLE FOR SECURING ANY INTELLECTUAL PROPERTY LICENSES OR RIGHTS WHICH MAY BE NECESSARY TO

IMPLEMENT OR BUILD PRODUCTS COMPLYING WITH OR MAKING ANY OTHER SUCH USE OF THE SPECIFICATION.

DISCLAIMER OF LIABILITY. RAPIDIO.ORG SHALL NOT BE LIABLE OR RESPONSIBLE FOR ACTUAL, INDIRECT, SPECIAL,

INCIDENTAL, EXEMPLARY OR CONSEQUENTIAL DAMAGES (INCLUDING, WITHOUT LIMITATION, LOST PROFITS)

RESULTING FROM USE OR INABILITY TO USE THE SPECIFICATION, ARISING FROM ANY CAUSE OF ACTION WHATSOEVER,

INCLUDING, WHETHER IN CONTRACT, WARRANTY, STRICT LIABILITY, OR NEGLIGENCE, EVEN IF RAPIDIO.ORG HAS BEEN

NOTIFIED OF THE POSSIBILITY OF SUCH DAMAGES.

Questions regarding RapidIO.org, specifications, or membership should be forwarded to:

RapidIO.org

8650 Spicewood Springs #145-515

Austin, TX 78759

512-827-7680 Tel.

RapidIO and the RapidIO logo are trademarks and service marks of RapidIO.org. All other trademarks are the property of their respective owners.

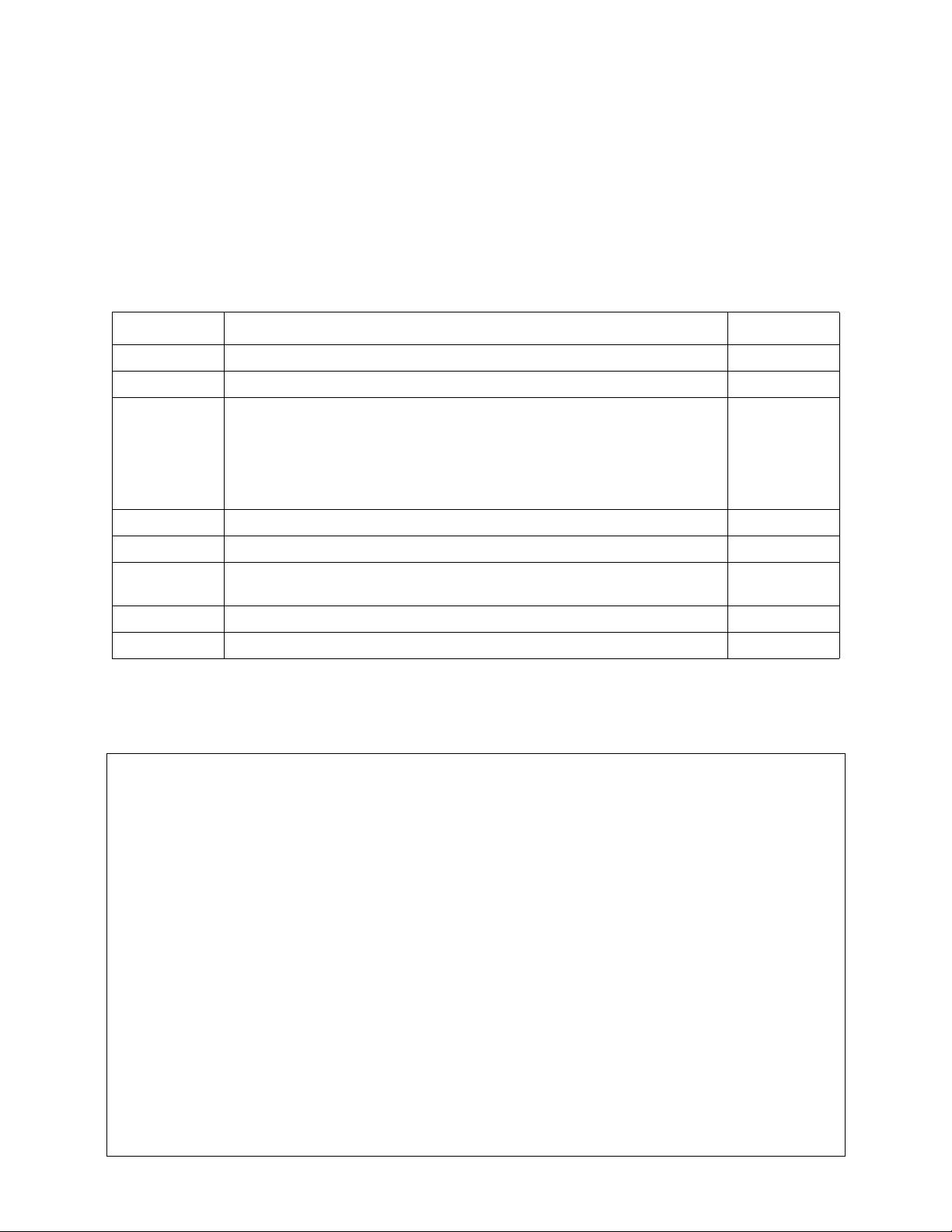

Revision History

Revision Description Date

1.1 First public release 03/08/2001

1.2 Technical changes: incorporate Rev. 1.1 errata rev. 1.1.1, errata 3 06/26/2002

1.3 Technical changes: incorporate Rev 1.2 errata 1 as applicable,

the following errata showings:

03-05-00006.001, 03-12-00001.001, 04-02-00001.002

and the following new features showings:

04-05-00005.001

Converted to ISO-friendly templates, re-formatted

02/23/2005

2.0 Technical changes: errata showings 06-11-00000.001, 06-11-00001.004 06/14/2007

2.1 Technical changes: errata showing 07-06-00000.010 07/09/2009

2.2 Technical changes: errata showings 09-09-00001.002, 10-08-00000.003,

10-08-00001.005, Consolidated Comments on 11-01-00000.000

05/05/2011

3.0 Changed RTA contact information. No technical changes. 11/9/2013

3.1 Addition of LCS Disable functionality. 09/18/2014

3.2 No technical changes. 01/28/2016

Table of Contents

RapidIO.org 3

RapidIO Part 1: Input/Output Logical Specification 3.2

Chapter 1 Overview

1.1 Introduction............................................................................................................. 9

1.2 Overview................................................................................................................. 9

1.3 Features of the Input/Output Specification........................................................... 10

1.3.1 Functional Features........................................................................................... 10

1.3.2 Physical Features .............................................................................................. 10

1.3.3 Performance Features ....................................................................................... 10

1.4 Contents ................................................................................................................ 11

1.5 Terminology.......................................................................................................... 11

1.6 Conventions .......................................................................................................... 11

Chapter 2 System Models

2.1 Introduction........................................................................................................... 13

2.2 Processing Element Models.................................................................................. 13

2.2.1 Processor-Memory Processing Element Model................................................ 13

2.2.2 Integrated Processor-Memory Processing Element Model .............................. 14

2.2.3 Memory-Only Processing Element Model ....................................................... 14

2.2.4 Processor-Only Processing Element................................................................. 15

2.2.5 I/O Processing Element .................................................................................... 15

2.2.6 Switch Processing Element............................................................................... 15

2.3 System Issues........................................................................................................ 16

2.3.1 Operation Ordering........................................................................................... 16

2.3.2 Transaction Delivery......................................................................................... 18

2.3.2.1 Unordered Delivery System Issues............................................................... 18

2.3.2.2 Ordered Delivery System Issues................................................................... 19

2.3.3 Deadlock Considerations.................................................................................. 19

Chapter 3 Operation Descriptions

3.1 Introduction........................................................................................................... 21

3.2 I/O Operations Cross Reference ........................................................................... 22

3.3 I/O Operations....................................................................................................... 22

3.3.1 Read Operations................................................................................................ 23

3.3.2 Write and Streaming-Write Operations............................................................ 23

3.3.3 Write-With-Response Operations..................................................................... 24

3.3.4 Atomic (Read-Modify-Write) Operations ........................................................ 24

3.4 System Operations................................................................................................ 25

3.4.1 Maintenance Operations ................................................................................... 25

3.5 Endian, Byte Ordering, and Alignment ................................................................ 25

4 RapidIO.org

Table of Contents

RapidIO Part 1: Input/Output Logical Specification 3.2

Chapter 4 Packet Format Descriptions

4.1 Request Packet Formats........................................................................................ 29

4.1.1 Addressing and Alignment ............................................................................... 30

4.1.2 Field Definitions for All Request Packet Formats............................................ 30

4.1.3 Type 0 Packet Format (Implementation-Defined)............................................ 33

4.1.4 Type 1 Packet Format (Reserved) .................................................................... 33

4.1.5 Type 2 Packet Format (Request Class)............................................................. 33

4.1.6 Type 3–4 Packet Formats (Reserved)............................................................... 34

4.1.7 Type 5 Packet Format (Write Class)................................................................. 34

4.1.8 Type 6 Packet Format (Streaming-Write Class)............................................... 35

4.1.9 Type 7 Packet Format (Reserved) .................................................................... 36

4.1.10 Type 8 Packet Format (Maintenance Class)..................................................... 36

4.1.11 Type 9–11 Packet Formats (Reserved)............................................................. 38

4.2 Response Packet Formats ..................................................................................... 38

4.2.1 Field Definitions for All Response Packet Formats ......................................... 38

4.2.2 Type 12 Packet Format (Reserved) .................................................................. 39

4.2.3 Type 13 Packet Format (Response Class) ........................................................ 39

4.2.4 Type 14 Packet Format (Reserved) .................................................................. 40

4.2.5 Type 15 Packet Format (Implementation-Defined).......................................... 40

Chapter 5 Input/Output Registers

5.1 Register Summary................................................................................................. 41

5.2 Reserved Register, Bit and Bit Field Value Behavior .......................................... 42

5.3 Extended Features Data Structure......................................................................... 43

5.4 Capability Registers (CARs) ................................................................................ 45

5.4.1 Device Identity CAR ........................................................................................ 45

5.4.2 Device Information CAR.................................................................................. 46

5.4.3 Assembly Identity CAR.................................................................................... 47

5.4.4 Assembly Information CAR............................................................................. 48

5.4.5 Processing Element Features CAR................................................................... 49

5.4.6 Switch Port Information CAR .......................................................................... 50

5.4.7 Source Operations CAR.................................................................................... 51

5.4.8 Destination Operations CAR ............................................................................ 52

5.5 Command and Status Registers (CSRs)................................................................ 53

5.5.1 Processing Element Logical Layer Control CSR ............................................. 53

5.5.2 Local Configuration Space Base Address 0 CSR............................................. 54

5.5.3 Local Configuration Space Base Address 1 CSR............................................. 55

List of Figures

RapidIO.org 5

RapidIO Part 1: Input/Output Logical Specification 3.2

2-1 A Possible RapidIO-Based Computing System..............................................................13

2-2 Processor-Memory Processing Element Example..........................................................14

2-3 Integrated Processor-Memory Processing Element Example.........................................14

2-4 Memory-Only Processing Element Example .................................................................15

2-5 Processor-Only Processing Element Example................................................................15

2-6 Switch Processing Element Example .............................................................................16

3-1 Read Operation ...............................................................................................................23

3-2 Write and Streaming-Write Operations ..........................................................................24

3-3 Write-With-Response Operation ....................................................................................24

3-4 Atomic (Read-Modify-Write) Operation........................................................................25

3-5 Maintenance Operation...................................................................................................25

3-6 Byte Alignment Example................................................................................................26

3-7 Half-Word Alignment Example......................................................................................26

3-8 Word Alignment Example..............................................................................................26

3-9 Data Alignment Example................................................................................................27

4-1 Type 2 Packet Bit Stream Format...................................................................................34

4-2 Type 5 Packet Bit Stream Format...................................................................................35

4-3 Type 6 Packet Bit Stream Format...................................................................................36

4-4 Type 8 Request Packet Bit Stream Format.....................................................................37

4-5 Type 8 Response Packet Bit Stream Format ..................................................................38

4-6 Type 13 Packet Bit Stream Format.................................................................................39

5-1 Example Extended Features Data Structure ...................................................................44

评论1

最新资源