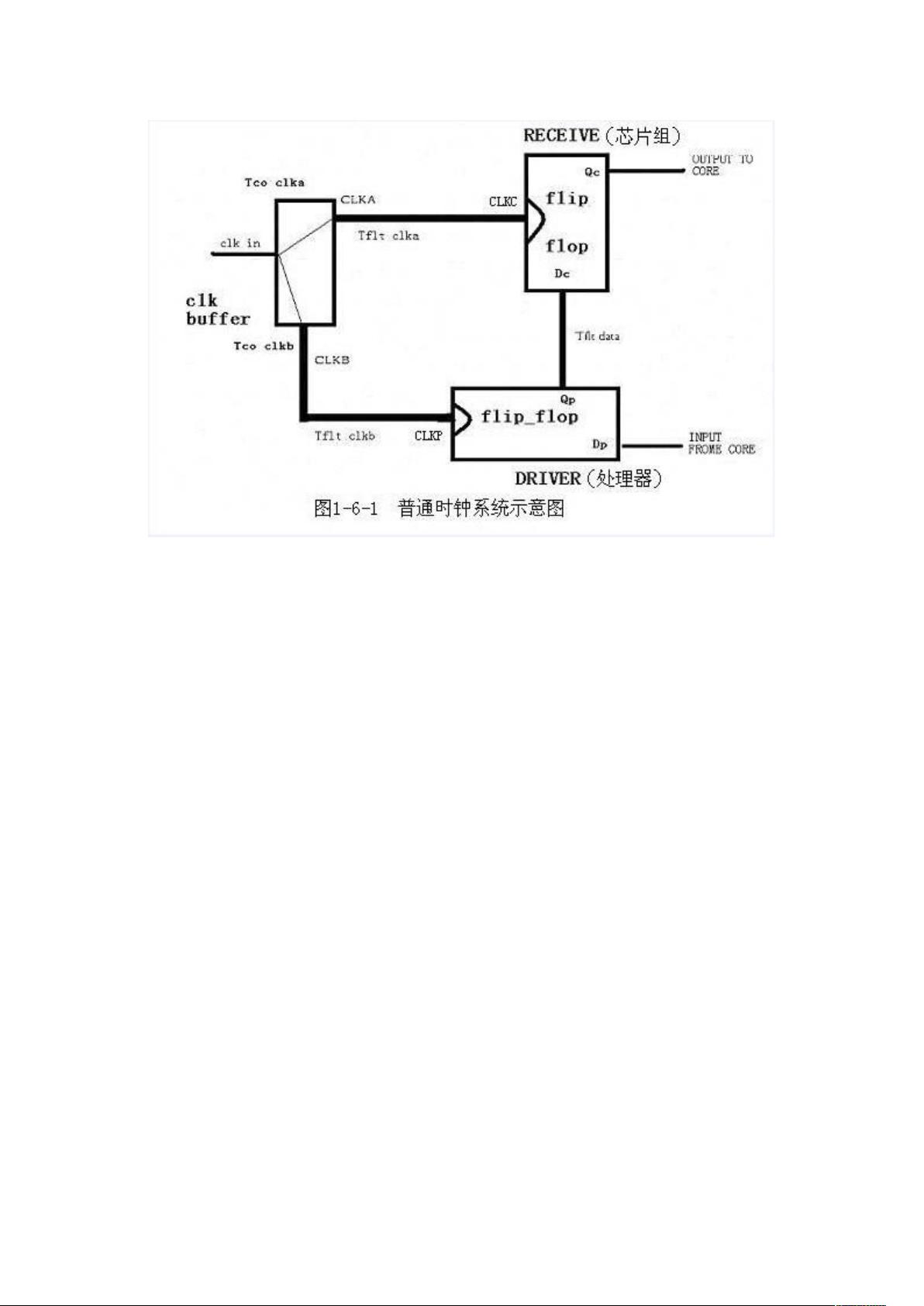

【FPGA时序分析理论】是FPGA设计中不可或缺的一部分,尤其在高速系统设计中,时序正确性至关重要。随着时钟频率的提高,数据传输的窗口期变得更短,因此需要精确的时序计算和分析以确保数据完整传输。同时,时序与信号完整性密切相关,任何信号质量问题都可能导致时序问题。 **一、普通时序系统(共同时钟系统)** 普通时序系统是指驱动端和接收端共享同一时钟源。在这样的系统中,例如CPU与芯片组之间的连接,数据传输分为三个步骤:1) 数据产生;2) 在第一个时钟上升沿,数据锁存在驱动端;3) 数据在第二个时钟上升沿到达接收端并被读取。时钟信号的延迟(Tflight clka 和 Tflight clkb)应保持同步,确保数据在时钟周期内传输完成。建立时间(Setup Time)是指数据必须在接收端时钟上升沿之前稳定,而保持时间(Hold Time)是指数据在时钟上升沿后需保持稳定的时间。如果传输延迟超过时钟周期,就会导致建立时间不足,引起数据错误。普通时序系统频率受限于时钟周期,过高则可能导致传输延迟超出限制。 **二、时序参数的确定** 深入理解时序参数至关重要。Tco(输出时钟到输出数据延迟)包含缓冲延时(buffer delay)和逻辑延时,用于衡量器件内部延迟。缓冲延时仅测量信号通过缓冲器达到稳定电压的时间。传播延迟关注信号在线路中的传播时间,而飞行时间(Flight Time)考虑了信号的变化速度,包括最大和最小飞行时间,它们受负载影响,用于时序估算。在时序分析中,应使用仿真测量最大/最小飞行时间,而非传播延迟。 在进行时序计算时,通常取最大上升沿和下降沿飞行时间的最长值,最小飞行时间的最短值。某些工具如Cadence中,最大飞行时间可能被称为最终稳定延迟(Final Settle Delay)。 **总结** FPGA设计中的时序分析涉及多个关键参数,如建立时间、保持时间、Tco、缓冲延时、传播延迟和飞行时间等。理解和掌握这些概念对于设计出稳定、高效的FPGA系统至关重要。随着技术的发展,时序问题的解决变得更为复杂,但通过精确的计算和仿真,可以确保系统在高速运行时仍能保持正确时序,避免数据错误,实现高效的数据传输。

剩余16页未读,继续阅读

- 粉丝: 5

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- dnSpy-net-win32-222.zip

- mongoose-free-6.9

- 德普微一级代理 DP100N06MGL PDFN3.3*3.3 TRMOS N-MOSFET 60V, 8mΩ, 45A

- 【java毕业设计】SpringBoot+Vue幼儿园管理系统 源码+sql脚本+论文 完整版

- 德普微一级代理 DP021N03FGLI DFN5*6 DPMOS N-MOSFET 30V 180A 1.8mΩ

- 巨潮资讯网5000只股票orgId-dict加密字典

- 基于java实现的快速排序代码

- 德普微一级代理 DP3145D SOT23-6 USB PD 协议单口控制器

- 【一文搞懂:什么是集成学习-原理+python代码】

- 国际象棋检测7-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma、TFRecord数据集合集.rar

信息提交成功

信息提交成功