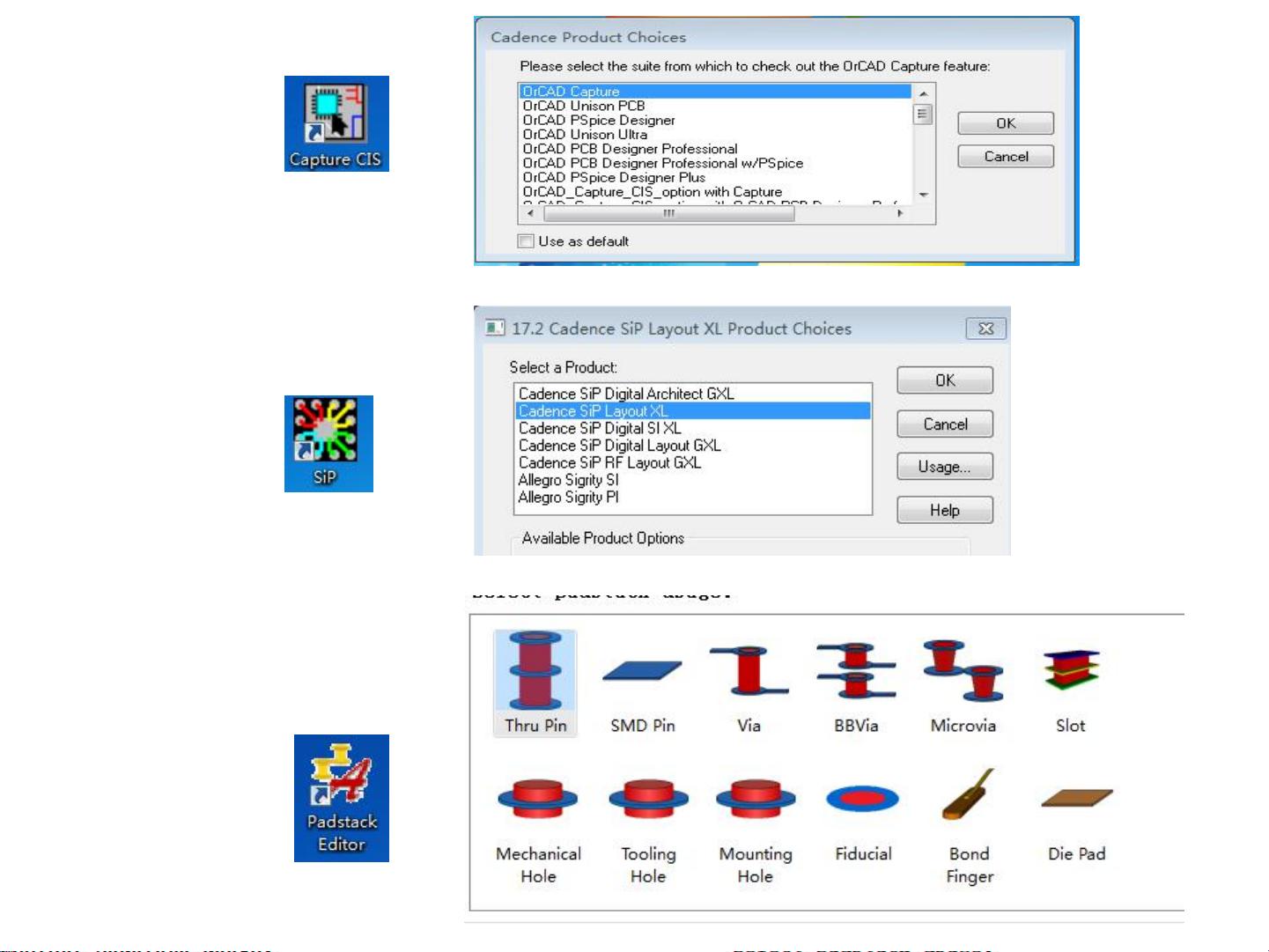

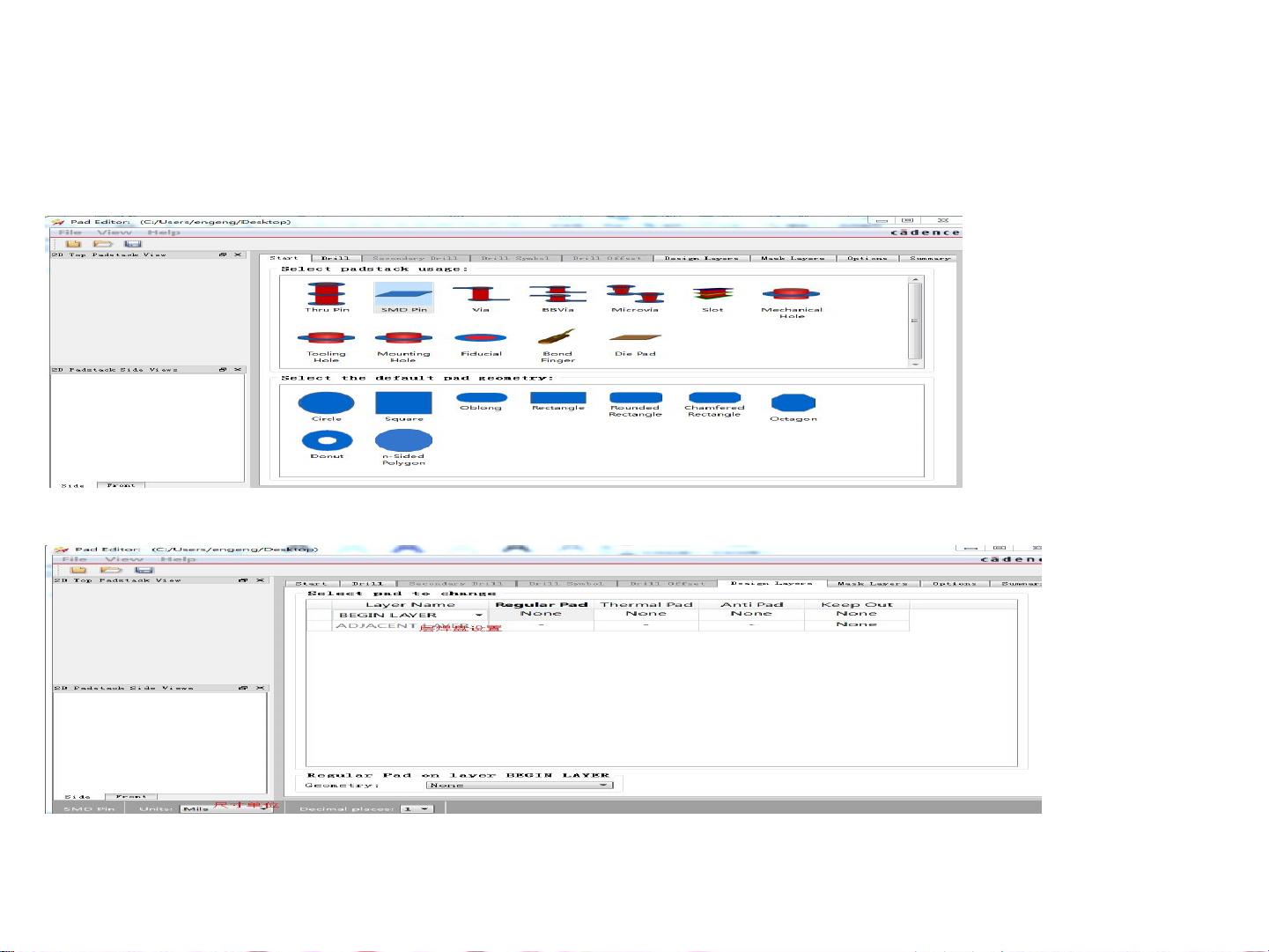

Cadence 17.2-2016-SIP-系统级别封装 Cadence 17.2-2016-SIP-系统级别封装是指多个半导体芯片或无源器件集成于一个封装内,形成一个功能性器件。这种系统级别封装具有多个优点,包括成本低、密度高、性能高、功耗低、设计周期短、灵活性高等。 系统级别封装的设计流程包括系统设计、原理图设计、SIP设计、基板制造、封装、性能/功能验证等几个阶段。在设计过程中,需要使用Cadence 17.2软件来进行设计和仿真。 Cadence 17.2提供了强大的设计工具和功能,能够满足复杂的系统级别封装设计需求。 在SIP设计中,需要考虑到多个方面的因素,包括IC的选择、封装的设计、信号完整性的优化、热设计、电源设计等。 Cadence 17.2提供了强大的设计工具和功能,能够帮助设计者快速完成SIP设计。在设计过程中,需要进行多个步骤,包括三维的DIE的创建和编辑、IC和封装的连接和优化、倒装焊工艺和自动扇出和布线等。 在原理图设计中,需要使用ORCAD文件来建立工程文件,并使用Library来建立元器件。设计者可以使用design功能来进行原理图设计,并使用 Place-part功能来添加元器件到电路中。设计完成后,需要进行DRC检查,以确保设计的正确性。 在焊盘设计中,需要考虑到焊盘的形状和尺寸。 Cadence 17.2提供了多种焊盘形状,包括圆形、正方形、长方形等。设计者可以根据不同的要求来设置焊盘的形状和尺寸。 Cadence 17.2-2016-SIP-系统级别封装设计需要具备强大的设计工具和功能,以满足复杂的系统级别封装设计需求。Cadence 17.2提供了强大的设计工具和功能,能够帮助设计者快速完成SIP设计。 知识点: 1. 系统级别封装的定义和特点 2. 系统级别封装的设计流程 3. Cadence 17.2软件的应用 4. SIP设计的优点和挑战 5. 原理图设计的步骤和工具 6. 焊盘设计的考虑因素和方法 7. Cadence 17.2-2016-SIP-系统级别封装设计的流程和要求 Cadence 17.2-2016-SIP-系统级别封装设计需要具备强大的设计工具和功能,以满足复杂的系统级别封装设计需求。设计者需要具备良好的设计经验和技能,以确保设计的正确性和可靠性。

剩余51页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功