1G/2.5G PCS/PMA or SGMII v16.1 5

PG047 November 14, 2018 www.xilinx.com Product Specification

Introduction

The LogiCORE™ IP 1G/2.5G Ethernet PCS/PMA

or Serial Gigabit Media Independent Interface

(SGMII) core provides a flexible solution for

connection to an Ethernet Media Access

Controller (MAC) or other custom logic. It

supports two standards: the 1000BASE-X and

2500BASE-X Physical Coding Sublayer (PCS)

and Physical Medium Attachment (PMA)

operation, as defined in the IEEE 802.3-2008

standard and the Gigabit Media Independent

Interface (GMII) to Serial-GMII (SGMII) bridge

or SGMII to GMII bridge, as defined in the

Serial-GMII Specification V1.7 (CISCO SYSTEMS,

ENG-46158) [Ref 1].

Dynamic switching between 1000BASE-X and

SGMII standards is also supported.

Features

The LogiCORE™ IP 1G/2.5G Ethernet PCS/PMA

or SGMII core provides the following

capabilities:

• Supported physical interfaces

for

1000

BASE-X and 2500BASE-X, SGMII,

or

2.5G

SGMII standards

• Integrated device-specific transc

eiver

interface

•

Support for SGMII over Select Input/Output

(I/O) Low Voltage Differentia

l Signaling

(L

VDS) in Zynq-7000, UltraScale, and

7series devices

• Configured and monitored through MDIO

• 1000BASE-X or 2500BASE-X and SGMI

I

Au

to-Negotiation supported

• Support for full duplex only

• Support preamble shrinkage for 2.

5G core

spe

e

d.

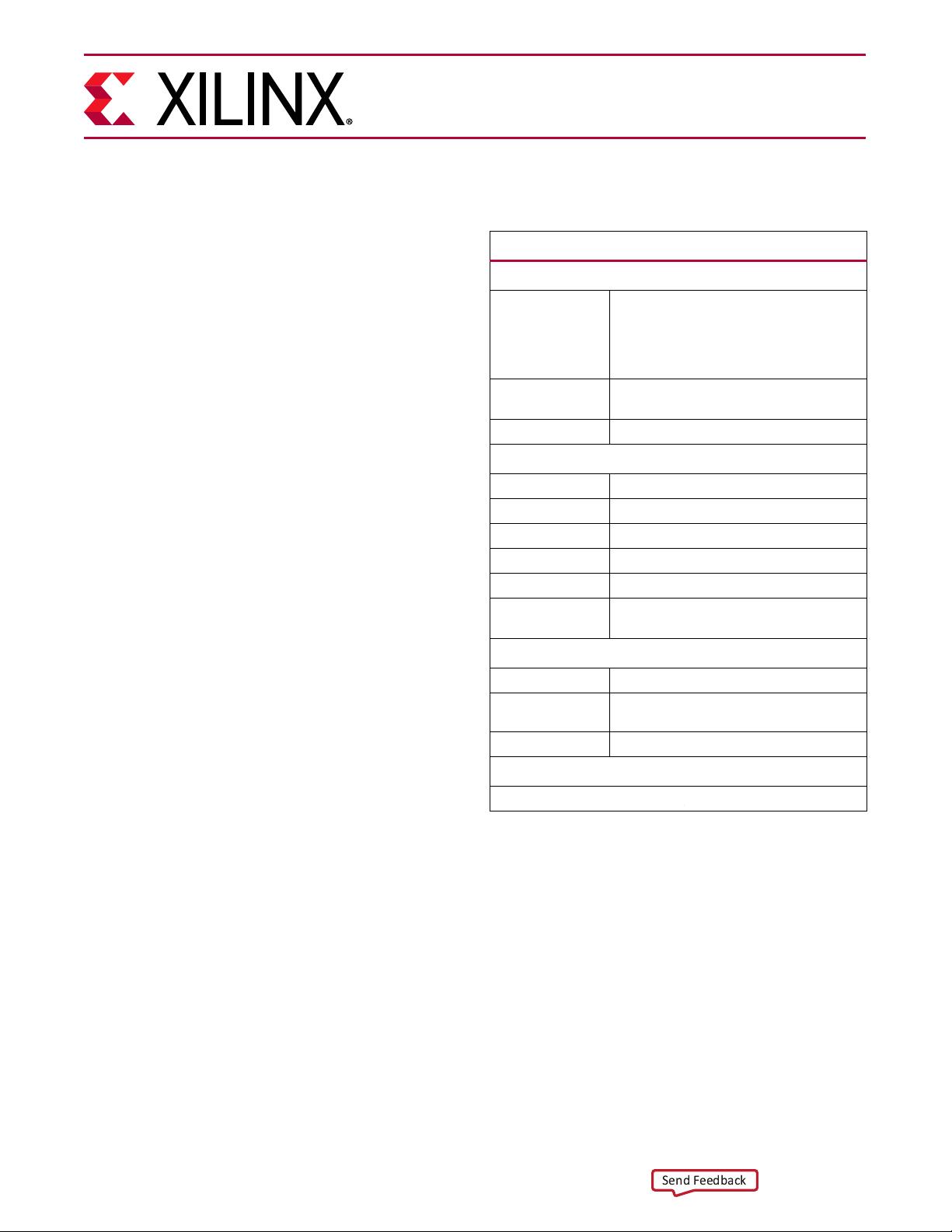

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported Device

Family

(1)

UltraScale+™

UltraScale™

Zynq® UltraScale+™ MPSoC

Zynq®-7000 SoC

7 Series

Supported User

Interfaces

GMII

(2)

Resources Performance and Resource Utilization

Provided with Core

Design Files Encrypted RTL

Example Designs Verilog and VHDL

Test Bench Demonstration Test Bench

Constraints File Xilinx Design Constraints (XDC)

Simulation Model Verilog and VHDL

Supported S/W

Driver

NA

Tested Design Flows

(3)

Design Entry Vivado® Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado I

P

ca

talog. For supported family configurations see Table 2- 1

.

For

supported speed grades see Speed Grades.

2. MII is supported only when used with EMAC0/EMAC1 present

in the Zynq-7000 SoC and Zynq UltraScale+ M

PSoC

p

rocessing subsystem (PS).

3. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

评论0

最新资源