Spartan-6 CSG324 FPGA Packaging and Pinouts Specification.pdf

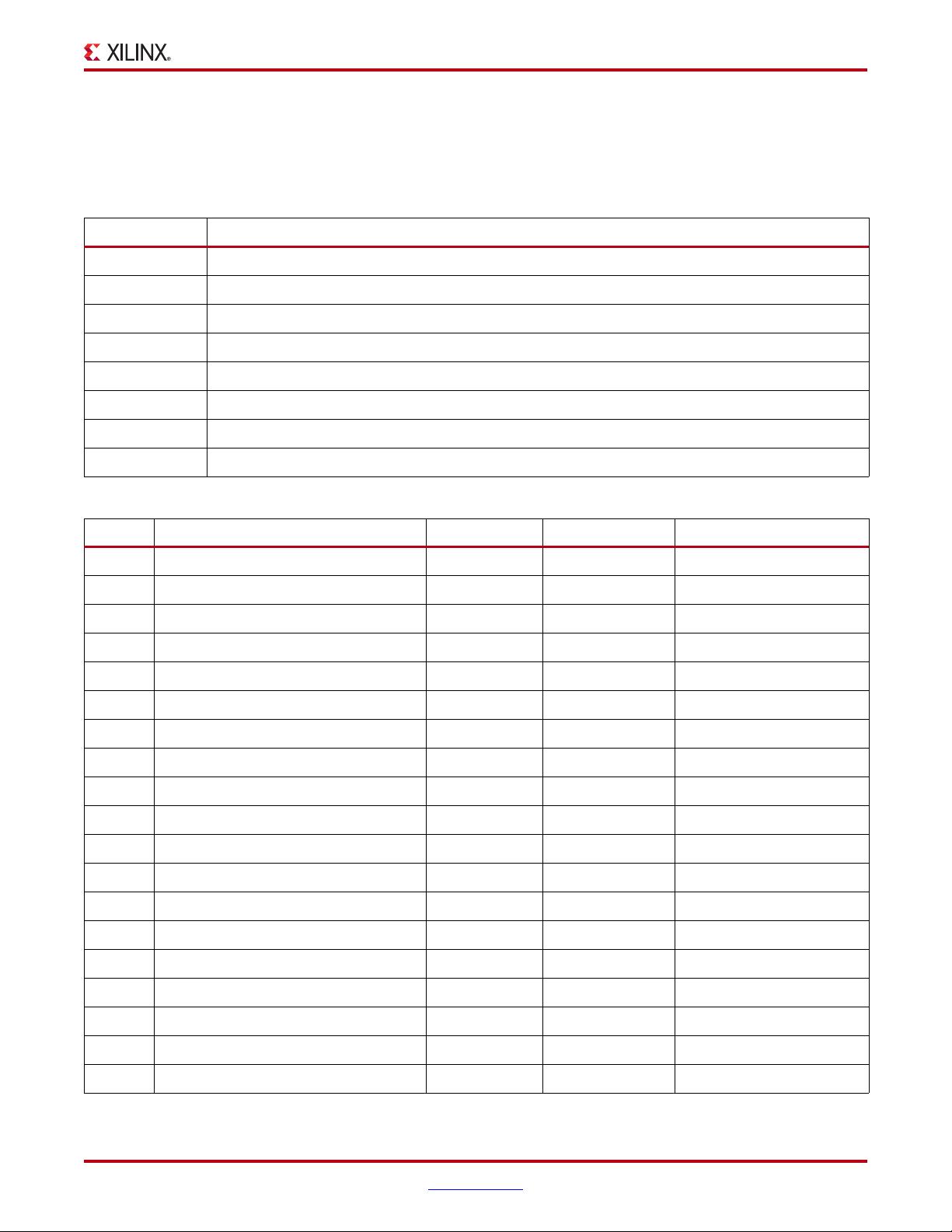

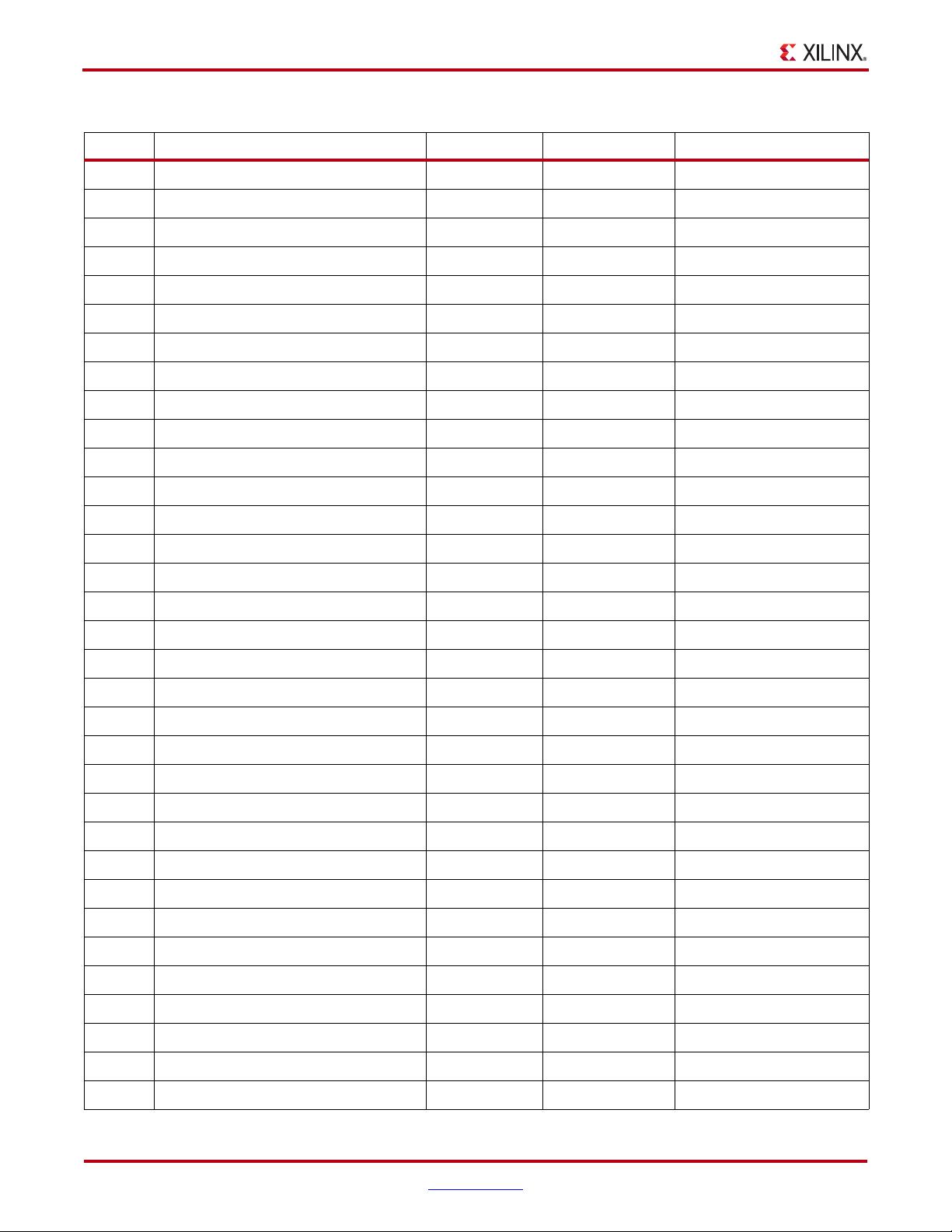

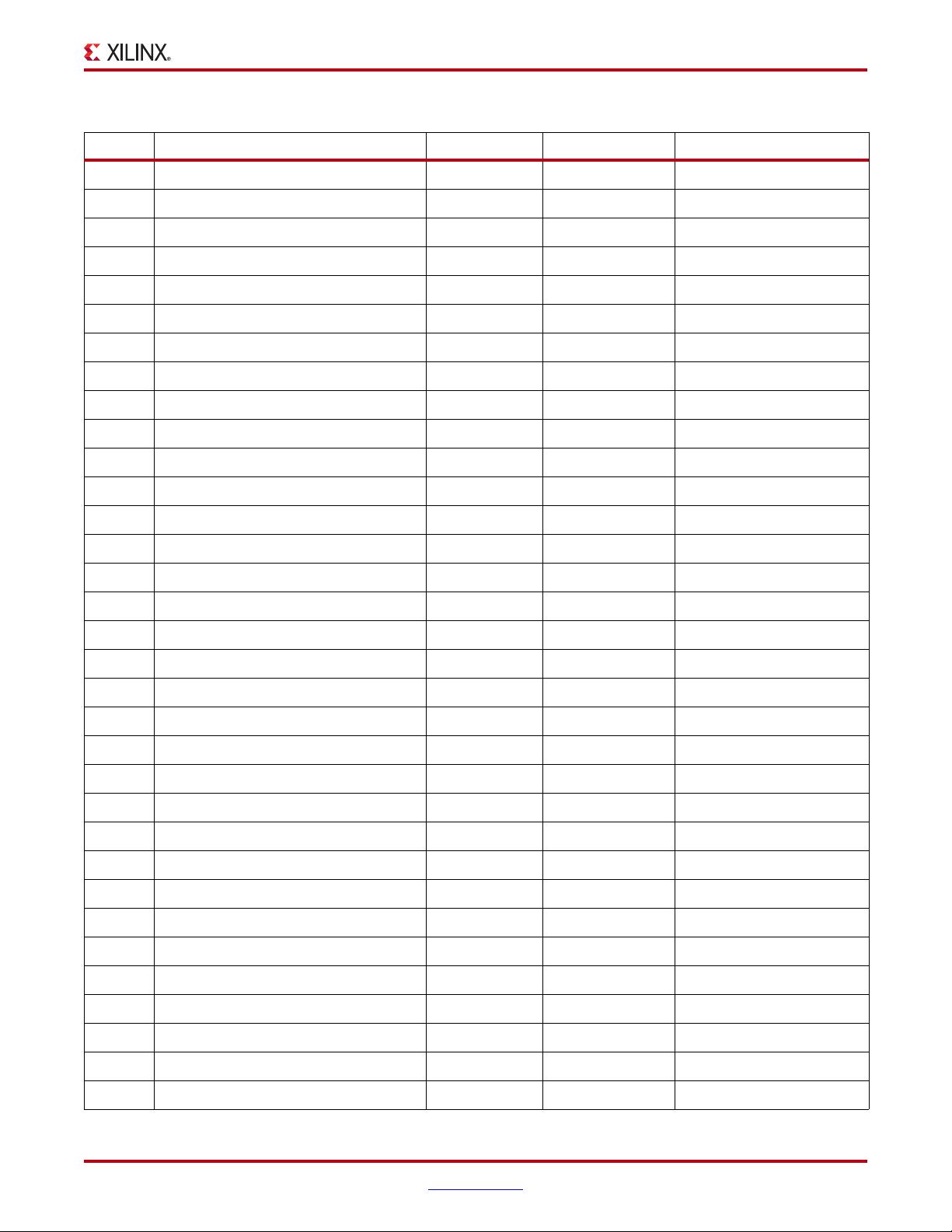

Spartan-6 FPGA Packaging and Pinouts Specification Spartan-6 FPGA 是 Xilinx 公司的一种 Field-Programmable Gate Array (FPGA),它提供了高性能、低功耗和灵活的解决方案,广泛应用于通信、数据中心、汽车电子、消费电子等领域。本文档详细介绍了 Spartan-6 FPGA 的封装和引脚规格,涵盖了 CSG324 封装的 LX9、LX16、LX25 和 LX45 设备。 BUFIO2 时钟区域 BUFIO2 时钟区域是 Spartan-6 FPGA 中的一个重要组件,它提供了时钟信号给 I/O 锁相器。BUFIO2 时钟区域位于 FPGA 的 left side of bank 0 (top) 和 right side of bank 0 (top),分别对应 TL 和 TR 引脚。BUFIO2 时钟区域还可以位于 top side of bank 1 (right) 和 bottom side of bank 1 (right),分别对应 RT 和 RB 引脚。 BUFIO2 时钟区域的主要特点是它可以提供高频率的时钟信号,最高达 640 MHz。这使得 Spartan-6 FPGA 能够满足高速数据传输和高速计算的需求。BUFIO2 时钟区域还支持多种时钟模式,包括single-ended 和 differential 模式,以满足不同的应用需求。 CSG324 封装 CSG324 封装是 Spartan-6 FPGA 的一种常见封装形式,它提供了 324 引脚,包括 I/O 引脚、时钟引脚、电源引脚等。CSG324 封装的尺寸为 17mm x 17mm,Thickness 为 1.4mm,非常适合小型化设计和高密度封装。 Pinout 表 Pinout 表是 Spartan-6 FPGA 的一个重要组件,它提供了每个引脚的详细信息,包括引脚名称、引脚类型、引脚功能等。Pinout 表还提供了 BUFIO2 时钟区域的详细信息,包括时钟信号的来源和时钟频率等。 在 Spartan-6 FPGA 中,Pinout 表主要包括以下几个部分: * I/O 引脚:包括数字 I/O、模拟 I/O 和专用 I/O 等。 * 时钟引脚:包括 BUFIO2 时钟区域和其他时钟信号。 * 电源引脚:包括电源输入、电源输出和地线等。 Spartan-6 FPGA 的封装和引脚规格是 FPGA 设计和开发的重要组件,需要根据具体应用需求进行选择和设计。本文档提供了 Spartan-6 FPGA 的详细信息,帮助开发者更好地理解和使用 Spartan-6 FPGA。

剩余10页未读,继续阅读

- 粉丝: 333

- 资源: 2100

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 人和箱子检测2-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 清华大学2022年秋季学期 高等数值分析课程报告

- GEE错误集-Cannot add an object of type <Element> to the map. Might be fixable with an explicit .pdf

- 清华大学2022年秋季学期 高等数值分析课程报告

- 矩阵与线程的对应关系图

- 人体人员检测46-YOLO(v5至v9)、COCO、Darknet、TFRecord数据集合集.rar

- GEMM优化代码实现1

- java实现的堆排序 含代码说明和示例.docx

- 资料阅读器(先下载解压) 5.0.zip

- 人、垃圾、非垃圾检测18-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

信息提交成功

信息提交成功