i.MX 6Dual/6Quad Applications

Processor Reference Manual

Document Number: IMX6DQRM

Rev 2, 06/2014

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

2 Freescale Semiconductor, Inc.

Contents

Section number Title Page

Chapter 1

Introduction

1.1 About This Document...................................................................................................................................................197

1.1.1 Audience.................................................................................................................................................... 197

1.1.2 Organization...............................................................................................................................................197

1.1.3 Suggested Reading.....................................................................................................................................198

1.1.3.1 General Information...............................................................................................................198

1.1.3.2 Related Documentation..........................................................................................................198

1.1.4 Conventions............................................................................................................................................... 198

1.1.5 Register Access..........................................................................................................................................200

1.1.5.1 Register Diagram Field Access Type Legend........................................................................200

1.1.5.2 Register Macro Usage............................................................................................................200

1.1.6 Signal Conventions.................................................................................................................................... 201

1.1.7 Acronyms and Abbreviations.....................................................................................................................202

1.2 Introduction...................................................................................................................................................................203

1.3 Target Applications.......................................................................................................................................................204

1.4 Features.........................................................................................................................................................................204

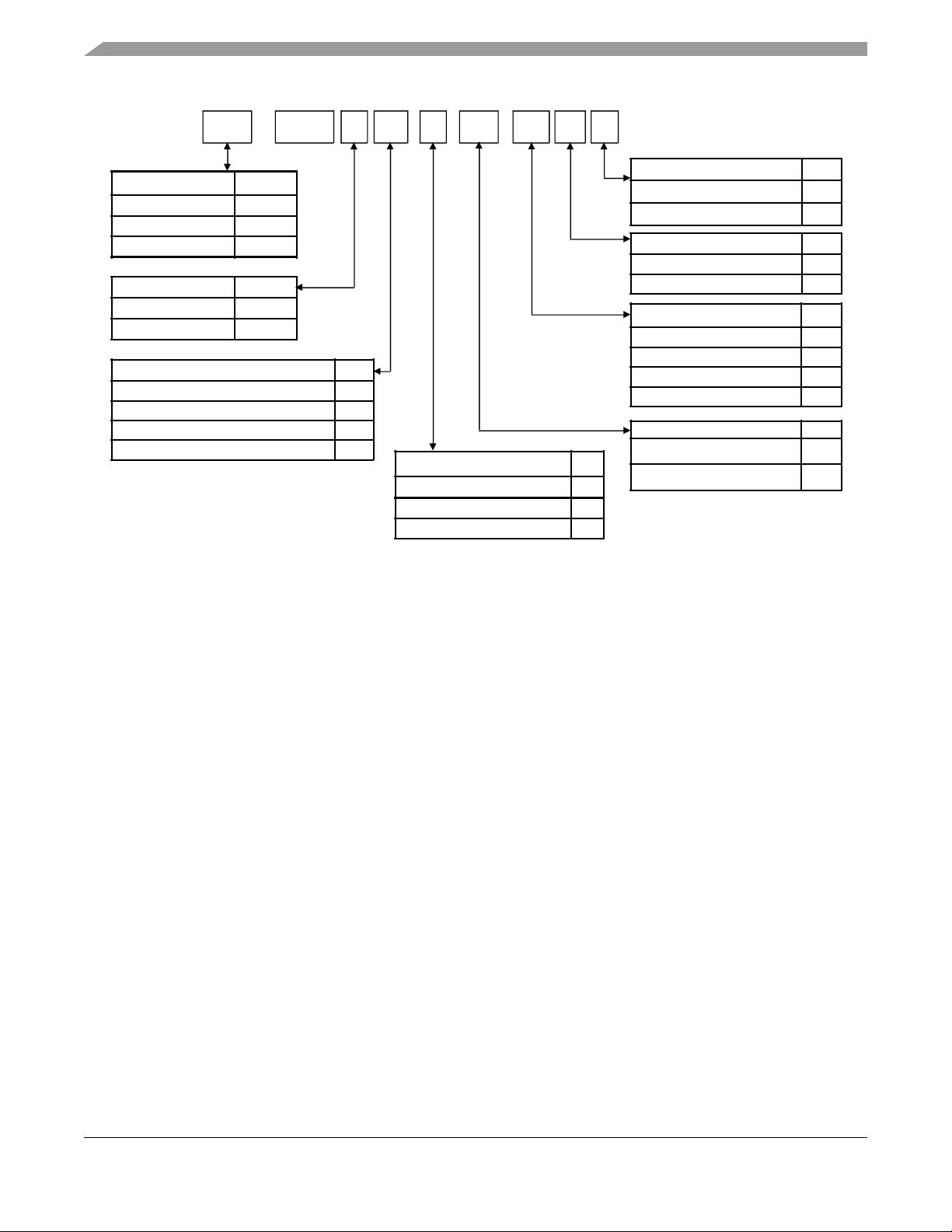

1.5 Architectural Overview.................................................................................................................................................208

1.5.1 Block Diagram........................................................................................................................................... 208

1.5.1.1 Simplified Block Diagram..................................................................................................... 208

1.5.2 Architectural Partitioning...........................................................................................................................209

1.5.3 Endianness Support....................................................................................................................................211

1.5.4 Memory Interfaces..................................................................................................................................... 211

Chapter 2

Memory Maps

2.1 Memory system overview.............................................................................................................................................213

2.2 ARM platform memory map........................................................................................................................................ 213

2.3 DDR mapping to MMDC controller ports....................................................................................................................218

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

Freescale Semiconductor, Inc. 3

Section number Title Page

2.4 DMA memory map.......................................................................................................................................................219

Chapter 3

Interrupts and DMA Events

3.1 Overview.......................................................................................................................................................................221

3.2 A9 interrupts................................................................................................................................................................. 221

3.3 SDMA event mapping.................................................................................................................................................. 225

Chapter 4

External Signals and Pin Multiplexing

4.1 Overview.......................................................................................................................................................................229

4.1.1 Pin Assignments.........................................................................................................................................229

4.1.2 Muxing Options......................................................................................................................................... 293

Chapter 5

Fusemap

5.1 Fusemap........................................................................................................................................................................335

5.2 Fusemap Description Table.......................................................................................................................................... 344

Chapter 6

External Memory Controllers

6.1 Overview.......................................................................................................................................................................351

6.2 Multi-mode DDR controller (MMDC) overview and feature summary...................................................................... 351

6.3 Raw NAND Flash controller overview.........................................................................................................................353

6.3.1 NAND interface features........................................................................................................................... 354

6.3.2 NAND control features.............................................................................................................................. 355

6.3.3 Internal interface features...........................................................................................................................355

6.3.4 APBH-DMA overview.............................................................................................................................. 355

6.3.5 ECC-BCH features.....................................................................................................................................355

6.4 EIM-PSRAM/NOR Flash controller overview.............................................................................................................356

6.4.1 EIM features...............................................................................................................................................356

6.4.2 EIM boot scenarios.................................................................................................................................... 357

6.4.3 EIM boot configuration..............................................................................................................................357

6.4.4 OneNAND requirements............................................................................................................................357

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

4 Freescale Semiconductor, Inc.

Section number Title Page

Chapter 7

System Debug

7.1 Overview.......................................................................................................................................................................359

7.2 Chip and Cortex-A9 Core Platform Debug Architecture............................................................................................. 359

7.2.1 Debug Features.......................................................................................................................................... 360

7.2.2 Debug System components........................................................................................................................361

7.2.2.1 AMBA trace bus (ATB).........................................................................................................362

7.2.2.2 ATB replicator....................................................................................................................... 362

7.2.2.3 Embedded Cross Triggering.................................................................................................. 362

7.2.2.3.1 Cross-Trigger Matrix (CTM)..........................................................................363

7.2.2.3.2 Cross-Trigger Interface (CTI).........................................................................364

7.2.2.4 Debug Access Port (DAP)..................................................................................................... 364

7.2.3 i.MX6Dual/6Quad-Specific SJC Features................................................................................................. 365

7.2.3.1 JTAG Disable Mode.............................................................................................................. 365

7.2.3.2 JTAG ID.................................................................................................................................365

7.2.4 System JTAG Controller - SJC..................................................................................................................366

7.2.5 System JTAG controller main features......................................................................................................366

7.2.6 SJC TAP Port.............................................................................................................................................366

7.2.7 SJC main blocks.........................................................................................................................................366

7.3 Smart DMA (SDMA) core............................................................................................................................................367

7.3.1 SDMA On Chip Emulation Module (OnCE) Feature Summary............................................................... 368

7.3.1.1 Other SDMA Debug Functionality........................................................................................368

7.3.1.2 SDMA ROM Patching...........................................................................................................369

7.4 Miscellaneous............................................................................................................................................................... 369

7.4.1 Clock/Reset/Power.....................................................................................................................................369

7.5 Supported tools............................................................................................................................................................. 370

Chapter 8

System Boot

8.1 Overview.......................................................................................................................................................................371

i.MX 6Dual/6Quad Applications Processor Reference Manual, Rev. 2, 06/2014

Freescale Semiconductor, Inc. 5