没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

FIFO Generator v13.2

LogiCORE IP Product Guide

Vivado Design Suite

PG057 October 4, 2017

FIFO Generator v13.2 www.xilinx.com 2

PG057 October 4, 2017

Table of Contents

IP Facts

Chapter 1: Overview

Native Interface FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

AXI Interface FIFOs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Initializing the FIFO Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

FIFO Usage and Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Actual FIFO Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Special Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Chapter 4: Design Flow Steps

Customizing and Generating the Native Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Customizing and Generating the AXI Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Chapter 5: Detailed Example Design

Implementing the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Send Feedback

FIFO Generator v13.2 www.xilinx.com 3

PG057 October 4, 2017

Simulating the Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Chapter 6: Test Bench

Test Bench Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Customizing the Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Messages and Warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Appendix A: Verification, Compliance, and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Appendix C: Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Appendix D: dout Reset Value Timing

Appendix E: FIFO Generator Files

Appendix F: Supplemental Information

Appendix G: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Send Feedback

FIFO Generator v13.2 www.xilinx.com 4

PG057 October 4, 2017 Product Specification

Introduction

The Xilinx LogiCORE™ IP FIFO Generator core is

a fully verified first-in first-out (FIFO) memory

queue for applications requiring in-order

storage and retrieval. The core provides an

optimized solution for all FIFO configurations

and delivers maximum performance (up to 500

MHz) while utilizing minimum resources.

Delivered through the Vivado® Design Suite,

you can customize the width, depth, status

flags, memory type, and the write/read port

aspect ratios.

The FIFO Generator core supports Native

interface FIFOs, AXI Memory Mapped interface

FIFOs and AXI4-Stream interface FIFOs. Native

interface FIFO cores are optimized for

buffering, data width conversion and clock

domain decoupling applications, providing

ordered storage and retrieval.

AXI Memory Mapped and AXI4-Stream

interface FIFOs are derived from the Native

interface FIFO. Three AXI Memory Mapped

interface styles are available: AXI4, AXI3 and

AXI4-Lite.

For more details on the features of each

interface, see Feature Summary in Chapter 1.

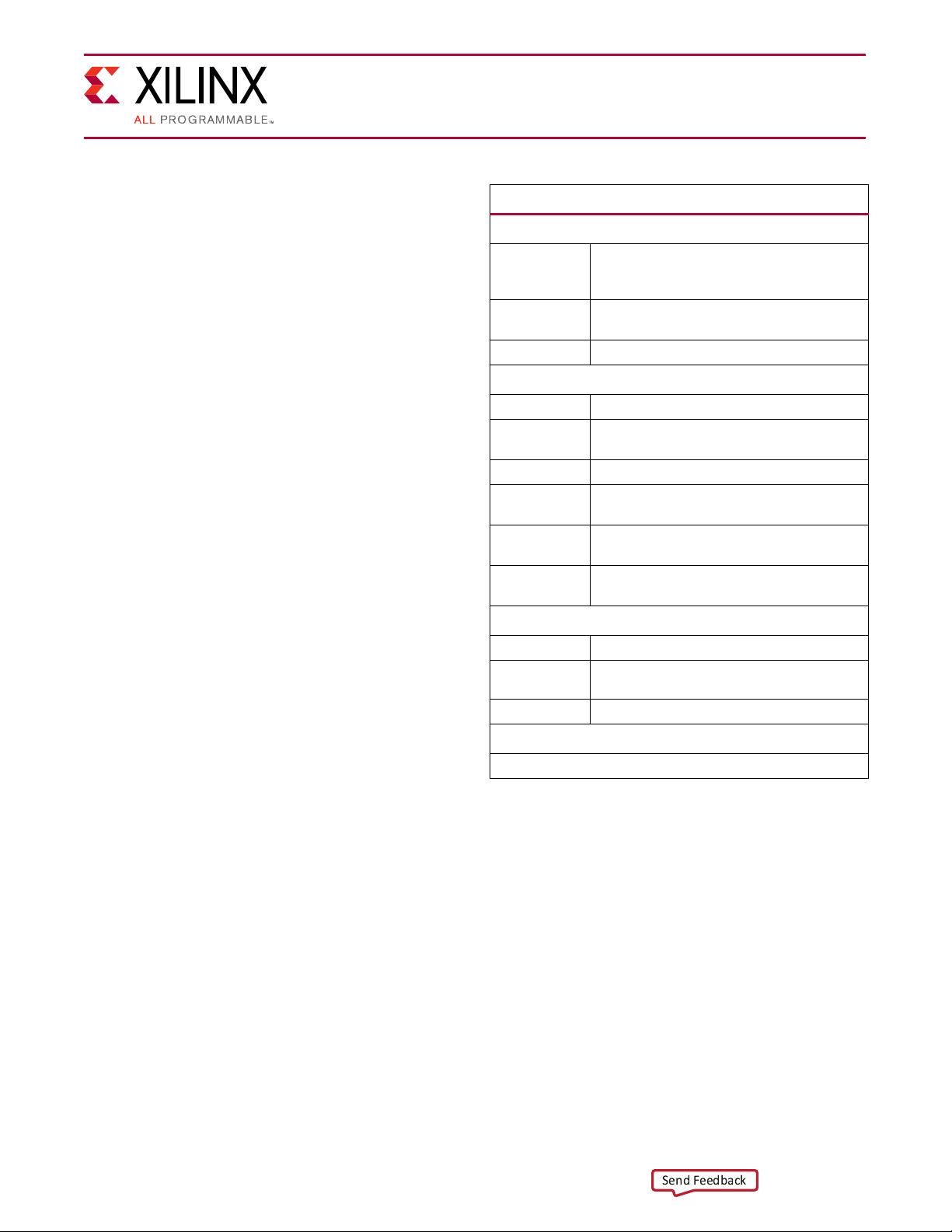

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

UltraScale+™ Families,

UltraScale™ Architecture, Zynq®-7000, 7 Series

Supported

User Interfaces

Native, AXI4-Stream, AXI4, AXI3, AXI4-Lite

Resources Performance and Resource Utilization web page

Provided with Core

Design Files Encrypted RTL

Example

Design

VHDL

Test Bench VHDL

Constraints

File

XDC

Simulation

Model

Verilog Behavioral

(2)

Supported

S/W Driver

N/A

Tested Design Fl ows

(4)

Design Entry Vivado Design Suite

Simulation

(3)

For other supported simulators, see the Xilinx

Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete listing of supported devices, see the Vivado IP

catalog.

2. Behavioral model does not model synchronization delay.

See

Simulation in Chapter 4 for details.

3. The FIFO Generator core supports the UniSim simulation

model.

4. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide.

Send Feedback

FIFO Generator v13.2 www.xilinx.com 5

PG057 October 4, 2017

Chapter 1

Overview

The FIFO Generator core is a fully verified first-in first-out memory queue for use in any

application requiring ordered storage and retrieval, enabling high-performance and

area-optimized designs. The core provides an optimized solution for all FIFO configurations

and delivers maximum performance (up to 500 MHz) while using minimum resources.

This core supports Native interface FIFOs, AXI Memory Mapped interface FIFOs and

AXI4-Stream interface FIFOs. AXI Memory Mapped and AXI4-Stream interface FIFOs are

derived from the Native interface FIFO. Three AXI Memory Mapped interface styles are

available: AXI4, AXI3 and AXI4-Lite.

This core can be customized using the Vivado IP customizers in the IP catalog as a complete

solution with control logic already implemented, including management of the read and

write pointers and the generation of status flags.

Note:

The Memory Mapped interface FIFO and AXI4-Stream interface FIFO are referred as "AXI

FIFO" throughout this document.

Native Interface FIFOs

The Native interface FIFO can be customized to utilize block RAM, distributed RAM or

built-in FIFO resources available in some FPGA families to create high-performance,

area-optimized FPGA designs.

Standard mode and First Word Fall Through are the two operating modes available for

Native interface FIFOs.

Send Feedback

剩余220页未读,继续阅读

资源评论

DBMY2024-02-01文件真实有效

DBMY2024-02-01文件真实有效

greengood

- 粉丝: 0

- 资源: 9

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于python实现的基于PyQt5和爬虫的小说阅读系统.zip

- 机械设计整经机上纱自动化sw20非常好的设计图纸100%好用.zip

- Screenshot_20240427_031602.jpg

- 网页PDF_2024年04月26日 23-46-14_QQ浏览器网页保存_QQ浏览器转格式(6).docx

- 直接插入排序,冒泡排序,直接选择排序.zip

- 在排序2的基础上,再次对快排进行优化,其次增加快排非递归,归并排序,归并排序非递归版.zip

- 实现了7种排序算法.三种复杂度排序.三种nlogn复杂度排序(堆排序,归并排序,快速排序)一种线性复杂度的排序.zip

- 冒泡排序 直接选择排序 直接插入排序 随机快速排序 归并排序 堆排序.zip

- 课设-内部排序算法比较 包括冒泡排序、直接插入排序、简单选择排序、快速排序、希尔排序、归并排序和堆排序.zip

- Python排序算法.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功