没有合适的资源?快使用搜索试试~ 我知道了~

ARM Neon指令的介绍

需积分: 5 3 下载量 144 浏览量

2023-02-26

08:58:28

上传

评论

收藏 2.98MB PDF 举报

温馨提示

试读

185页

ARM Neon指令的介绍

资源推荐

资源详情

资源评论

Arm Neon Intrinsics

Reference for ACLE Q3 2020

Non-Confidential

Issue G

Copyright © 2014 - 2020 Arm Limited (or its affiliates).

All rights reserved.

IHI 0073G

Arm Neon Intrinsics Reference

IHI 0073G

Copyright © 2014 - 2020 Arm Limited (or its affiliates). All rights reserved.

Non-Confidential

Page 2 of 185

Arm Neon Intrinsics

Reference

Copyright

©

2014 - 2020 Arm Limited (or its affiliates). All rights reserved.

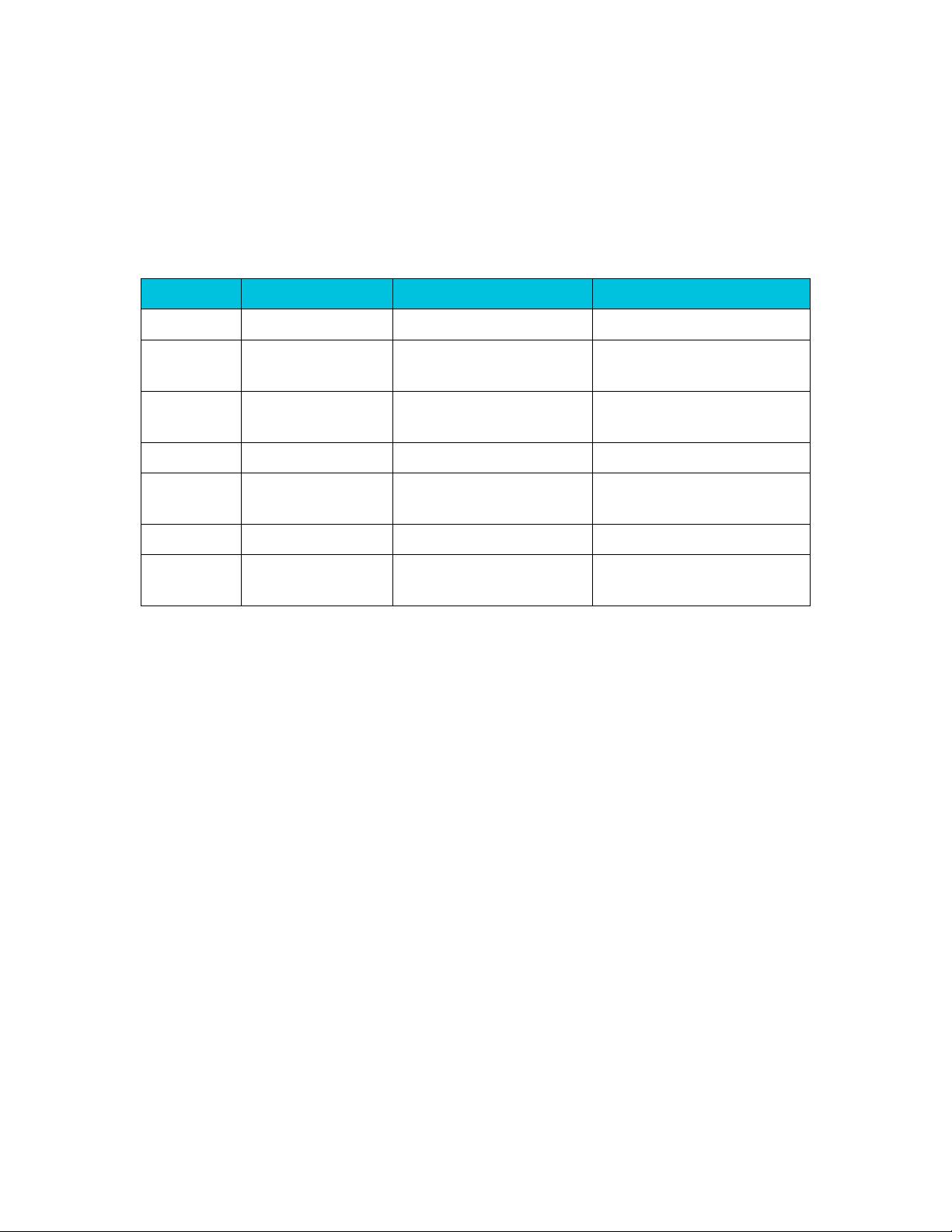

Release information

Document history

Issue

Date

Confidentiality

Change

A

09 May 2014

Non-Confidential

First release

B

24 March

2016

Non-Confidential

Updated for ARMv8.1

C

30 March

2019

Non-Confidential

Version ACLE Q1 2019.

D

30 June 2019

Non-Confidential

Version ACLE Q2 2019.

E

30 September

2019

Non-Confidential

Version ACLE Q3 2019

F

30 May 2020

Non-Confidential

Version ACLE Q2 2020

G

30 October

2020

Non-Confidential

Version ACLE Q3 2020

Non-Confidential Proprietary Notice

This document is protected by copyright and other related rights and the practice or implementation

of the information contained in this document may be protected by one or more patents or pending

patent applications. No part of this document may be reproduced in any form by any means without

the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise

to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not

use or permit others to use the information for the purposes of determining whether implementations

infringe any third party patents.

THIS DOCUMENT IS PROVIDED “AS IS”. ARM PROVIDES NO REPRESENTATIONS AND NO

WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE

IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-

INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE

DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has

undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade

secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY

DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL,

INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND

Arm Neon Intrinsics Reference

IHI 0073G

Copyright © 2014 - 2020 Arm Limited (or its affiliates). All rights reserved.

Non-Confidential

Page 3 of 185

REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT,

EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use,

duplication or disclosure of this document complies fully with any relevant export laws and regulations

to assure that this document or any portion thereof is not exported, directly or indirectly, in violation

of such export laws. Use of the word “partner” in reference to Arm's customers is not intended to

create or refer to any partnership relationship with any other company. Arm may make changes to this

document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through

or signed written agreement covering this document with Arm, then the click through or signed

written agreement prevails over and supersedes the conflicting provisions of these terms. This

document may be translated into other languages for convenience, and you agree that if there is any

conflict between the English version of this document and any translation, the terms of the English

version of the Agreement shall prevail.

The Arm corporate logo and words marked with

®

or ™ are registered trademarks or trademarks of

Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and

names mentioned in this document may be the trademarks of their respective owners. Please follow

Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright

©

2014 - 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject

to license restrictions in accordance with the terms of the agreement entered into by Arm and the

party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

Arm Neon Intrinsics Reference

IHI 0073G

Copyright © 2014 - 2020 Arm Limited (or its affiliates). All rights reserved.

Non-Confidential

Page 5 of 185

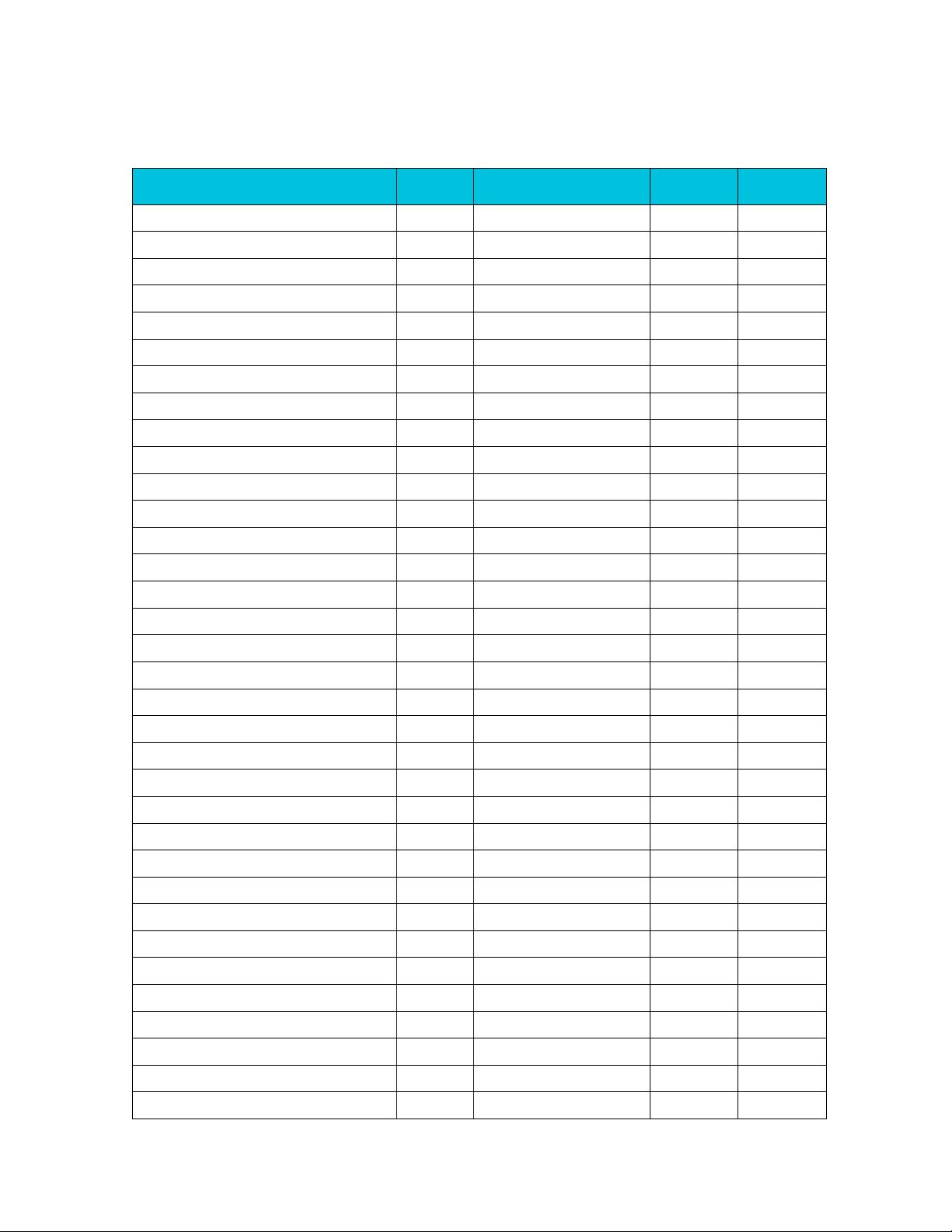

List of Intrinsics

Intrinsic

Argument

Preparation

Instruction

Result

Supported

Architectures

int8x8_t vadd_s8(int8x8_t a, int8x8_t b)

a -> Vn.8B

b -> Vm.8B

ADD Vd.8B,Vn.8B,Vm.8B

Vd.8B -> result

v7/A32/A64

int8x16_t vaddq_s8(int8x16_t a, int8x16_t b)

a -> Vn.16B

b -> Vm.16B

ADD Vd.16B,Vn.16B,Vm.16B

Vd.16B ->

result

v7/A32/A64

int16x4_t vadd_s16(int16x4_t a, int16x4_t b)

a -> Vn.4H

b -> Vm.4H

ADD Vd.4H,Vn.4H,Vm.4H

Vd.4H -> result

v7/A32/A64

int16x8_t vaddq_s16(int16x8_t a, int16x8_t b)

a -> Vn.8H

b -> Vm.8H

ADD Vd.8H,Vn.8H,Vm.8H

Vd.8H -> result

v7/A32/A64

int32x2_t vadd_s32(int32x2_t a, int32x2_t b)

a -> Vn.2S

b -> Vm.2S

ADD Vd.2S,Vn.2S,Vm.2S

Vd.2S -> result

v7/A32/A64

int32x4_t vaddq_s32(int32x4_t a, int32x4_t b)

a -> Vn.4S

b -> Vm.4S

ADD Vd.4S,Vn.4S,Vm.4S

Vd.4S -> result

v7/A32/A64

int64x1_t vadd_s64(int64x1_t a, int64x1_t b)

a -> Dn

b -> Dm

ADD Dd,Dn,Dm

Dd -> result

v7/A32/A64

int64x2_t vaddq_s64(int64x2_t a, int64x2_t b)

a -> Vn.2D

b -> Vm.2D

ADD Vd.2D,Vn.2D,Vm.2D

Vd.2D -> result

v7/A32/A64

uint8x8_t vadd_u8(uint8x8_t a, uint8x8_t b)

a -> Vn.8B

b -> Vm.8B

ADD Vd.8B,Vn.8B,Vm.8B

Vd.8B -> result

v7/A32/A64

uint8x16_t vaddq_u8(uint8x16_t a, uint8x16_t b)

a -> Vn.16B

b -> Vm.16B

ADD Vd.16B,Vn.16B,Vm.16B

Vd.16B ->

result

v7/A32/A64

uint16x4_t vadd_u16(uint16x4_t a, uint16x4_t b)

a -> Vn.4H

b -> Vm.4H

ADD Vd.4H,Vn.4H,Vm.4H

Vd.4H -> result

v7/A32/A64

uint16x8_t vaddq_u16(uint16x8_t a, uint16x8_t b)

a -> Vn.8H

b -> Vm.8H

ADD Vd.8H,Vn.8H,Vm.8H

Vd.8H -> result

v7/A32/A64

uint32x2_t vadd_u32(uint32x2_t a, uint32x2_t b)

a -> Vn.2S

b -> Vm.2S

ADD Vd.2S,Vn.2S,Vm.2S

Vd.2S -> result

v7/A32/A64

uint32x4_t vaddq_u32(uint32x4_t a, uint32x4_t b)

a -> Vn.4S

b -> Vm.4S

ADD Vd.4S,Vn.4S,Vm.4S

Vd.4S -> result

v7/A32/A64

uint64x1_t vadd_u64(uint64x1_t a, uint64x1_t b)

a -> Dn

b -> Dm

ADD Dd,Dn,Dm

Dd -> result

v7/A32/A64

uint64x2_t vaddq_u64(uint64x2_t a, uint64x2_t b)

a -> Vn.2D

b -> Vm.2D

ADD Vd.2D,Vn.2D,Vm.2D

Vd.2D -> result

v7/A32/A64

float32x2_t vadd_f32(float32x2_t a, float32x2_t b)

a -> Vn.2S

b -> Vm.2S

FADD Vd.2S,Vn.2S,Vm.2S

Vd.2S -> result

v7/A32/A64

float32x4_t vaddq_f32(float32x4_t a, float32x4_t b)

a -> Vn.4S

b -> Vm.4S

FADD Vd.4S,Vn.4S,Vm.4S

Vd.4S -> result

v7/A32/A64

float64x1_t vadd_f64(float64x1_t a, float64x1_t b)

a -> Dn

b -> Dm

FADD Dd,Dn,Dm

Dd -> result

A64

float64x2_t vaddq_f64(float64x2_t a, float64x2_t b)

a -> Vn.2D

b -> Vm.2D

FADD Vd.2D,Vn.2D,Vm.2D

Vd.2D -> result

A64

int64_t vaddd_s64(int64_t a, int64_t b)

a -> Dn

b -> Dm

ADD Dd,Dn,Dm

Dd -> result

A64

uint64_t vaddd_u64(uint64_t a, uint64_t b)

a -> Dn

b -> Dm

ADD Dd,Dn,Dm

Dd -> result

A64

int16x8_t vaddl_s8(int8x8_t a, int8x8_t b)

a -> Vn.8B

b -> Vm.8B

SADDL Vd.8H,Vn.8B,Vm.8B

Vd.8H -> result

v7/A32/A64

int32x4_t vaddl_s16(int16x4_t a, int16x4_t b)

a -> Vn.4H

b -> Vm.4H

SADDL Vd.4S,Vn.4H,Vm.4H

Vd.4S -> result

v7/A32/A64

int64x2_t vaddl_s32(int32x2_t a, int32x2_t b)

a -> Vn.2S

b -> Vm.2S

SADDL Vd.2D,Vn.2S,Vm.2S

Vd.2D -> result

v7/A32/A64

uint16x8_t vaddl_u8(uint8x8_t a, uint8x8_t b)

a -> Vn.8B

b -> Vm.8B

UADDL Vd.8H,Vn.8B,Vm.8B

Vd.8H -> result

v7/A32/A64

uint32x4_t vaddl_u16(uint16x4_t a, uint16x4_t b)

a -> Vn.4H

b -> Vm.4H

UADDL Vd.4S,Vn.4H,Vm.4H

Vd.4S -> result

v7/A32/A64

uint64x2_t vaddl_u32(uint32x2_t a, uint32x2_t b)

a -> Vn.2S

b -> Vm.2S

UADDL Vd.2D,Vn.2S,Vm.2S

Vd.2D -> result

v7/A32/A64

int16x8_t vaddl_high_s8(int8x16_t a, int8x16_t b)

a -> Vn.16B

b -> Vm.16B

SADDL2 Vd.8H,Vn.16B,Vm.16B

Vd.8H -> result

A64

int32x4_t vaddl_high_s16(int16x8_t a, int16x8_t b)

a -> Vn.8H

b -> Vm.8H

SADDL2 Vd.4S,Vn.8H,Vm.8H

Vd.4S -> result

A64

int64x2_t vaddl_high_s32(int32x4_t a, int32x4_t b)

a -> Vn.4S

b -> Vm.4S

SADDL2 Vd.2D,Vn.4S,Vm.4S

Vd.2D -> result

A64

uint16x8_t vaddl_high_u8(uint8x16_t a, uint8x16_t b)

a -> Vn.16B

b -> Vm.16B

UADDL2 Vd.8H,Vn.16B,Vm.16B

Vd.8H -> result

A64

uint32x4_t vaddl_high_u16(uint16x8_t a, uint16x8_t

b)

a -> Vn.8H

b -> Vm.8H

UADDL2 Vd.4S,Vn.8H,Vm.8H

Vd.4S -> result

A64

uint64x2_t vaddl_high_u32(uint32x4_t a, uint32x4_t

b)

a -> Vn.4S

b -> Vm.4S

UADDL2 Vd.2D,Vn.4S,Vm.4S

Vd.2D -> result

A64

剩余184页未读,继续阅读

资源评论

加菲猫0320

- 粉丝: 3

- 资源: 34

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 论文(最终)_20240430235101.pdf

- 基于python编写的Keras深度学习框架开发,利用卷积神经网络CNN,快速识别图片并进行分类

- 最全空间计量实证方法(空间杜宾模型和检验以及结果解释文档).txt

- 5uonly.apk

- 蓝桥杯Python组的历年真题

- 2023-04-06-项目笔记 - 第一百十九阶段 - 4.4.2.117全局变量的作用域-117 -2024.04.30

- 2023-04-06-项目笔记 - 第一百十九阶段 - 4.4.2.117全局变量的作用域-117 -2024.04.30

- 前端开发技术实验报告:内含4四实验&实验报告

- Highlight Plus v20.0.1

- 林周瑜-论文.docx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功