计算机组成原理大型实验-实验报告及源代码.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

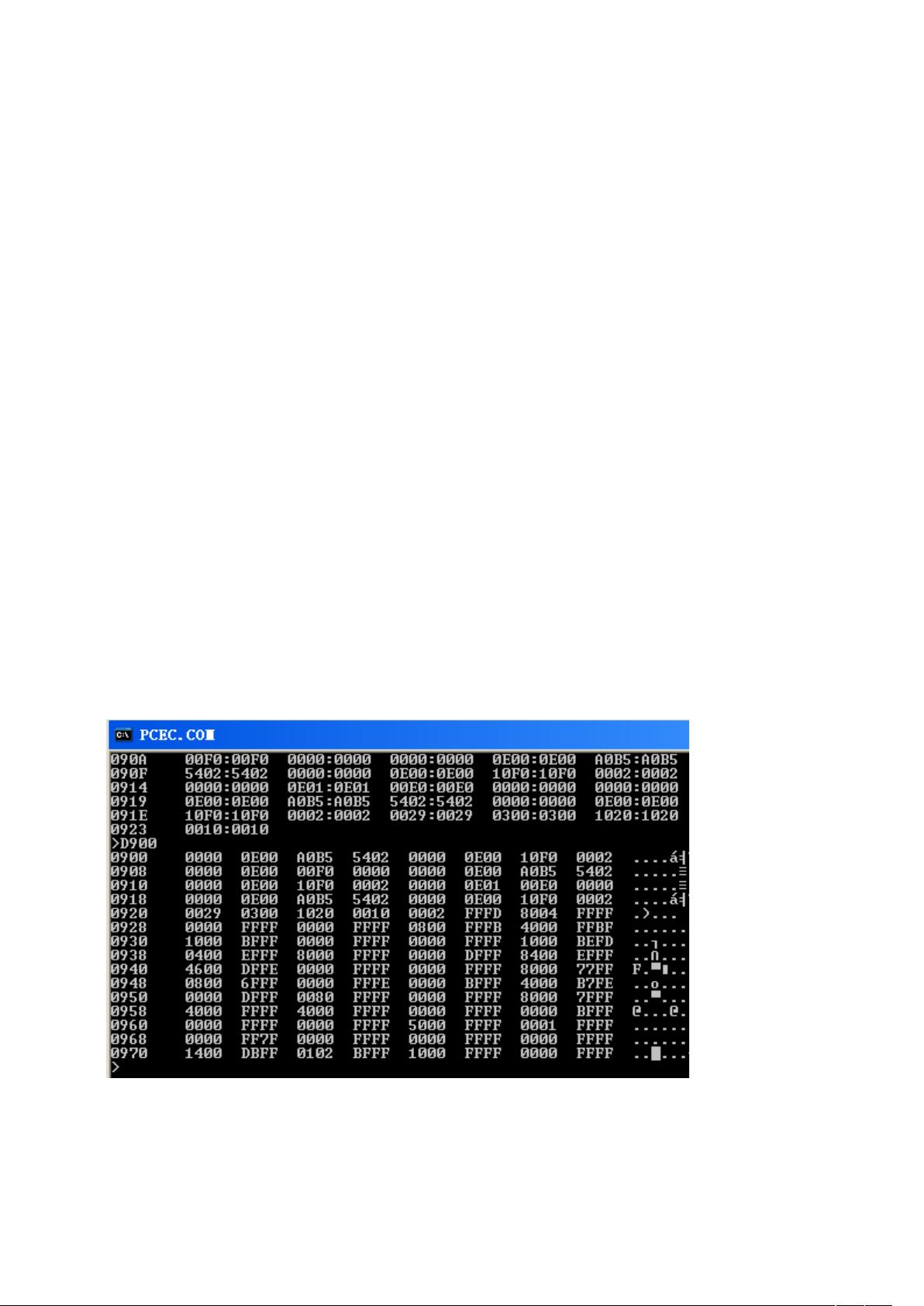

【计算机组成原理大型实验】是计算机科学领域中的一个重要实践环节,旨在通过实际操作来加深对计算机内部工作原理的理解。实验报告及源代码是这个实验的重要组成部分,它涵盖了实验的目标、内容、要求以及具体的指令设计和微程序实现。 一、实验目的: 本实验的主要目标是让学生深入理解计算机指令的执行流程,掌握控制器的构造,了解指令系统和微程序设计的基本概念。特别是动态微程序设计,这是一种允许在运行时改变控制逻辑的设计方法,可以提高计算机系统的灵活性和可扩展性。 二、实验说明: 实验基于TEC-2机器模型进行,学生需要熟悉TEC-2的功能部件、连接关系以及各个部件的具体作用。此外,还需要掌握TEC-2支持的指令格式、微指令结构,以及AM2910芯片的应用。通过分析已经实现的指令执行实例,学习如何设计新指令,并理解其执行顺序。 三、实验内容: 1. 设计一个四字指令,将两个绝对地址存储单元的内容相加,结果存储到第三个存储单元。指令格式为D4XX,ADDR1,ADDR2,ADDR3,控制存储器入口为100H。 2. 实现一个双字指令,将一个通用寄存器的内容减去内存单元的内容,结果存入另一个寄存器。指令格式为E0 DR SR,ADDR,控制存储器入口为130H。 3. 设计一个转移指令,比较两个通用寄存器的内容,如果相等则转移到指定地址,否则继续顺序执行。指令格式为E5 DR SR,ADDR,控制存储器入口为140H。 四、实验要求: 1. 学生需要自行设计相关指令的微程序,并在非上机时间完成。 2. 编写测试程序,准备实验数据,并进行上机调试。 3. 完成实验报告,包括设计目的、设计内容、微程序设计(包含指令格式、功能、设计和微程序)以及实验数据(测试指令的程序和结果)。 4. 实验报告需打印成册,按照规定的时间提交。 以第一条指令为例,加法指令D4XX,ADDR1,ADDR2,ADDR3的微程序设计包括一系列的控制信号产生,如读取内存、累加、更新内存和条件判断等操作。微程序设计的步骤通常包括分析指令格式,确定微操作序列,分配微指令地址,编写微指令代码,并进行调试验证。 通过这样的实验,学生不仅可以学习到计算机硬件层面的操作,还能了解到软件和硬件之间的交互,这对于理解计算机系统的工作原理至关重要。此外,设计和调试微程序的过程也有助于培养学生的逻辑思维能力和问题解决能力。

剩余11页未读,继续阅读

- 粉丝: 15

- 资源: 19万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于Spring Boot框架的报表管理系统.zip

- (源码)基于树莓派和TensorFlow Lite的智能厨具环境监测系统.zip

- (源码)基于OpenCV和Arduino的面部追踪系统.zip

- (源码)基于C++和ZeroMQ的分布式系统中间件.zip

- (源码)基于SSM框架的学生信息管理系统.zip

- (源码)基于PyTorch框架的智能视频分析系统.zip

- (源码)基于STM32F1的Sybertooth电机驱动系统.zip

- (源码)基于PxMATRIX库的嵌入式系统显示与配置管理.zip

- (源码)基于虚幻引擎的舞蹈艺术节目包装系统.zip

- (源码)基于Dubbo和Redis的用户中台系统.zip

信息提交成功

信息提交成功