tutorial_quartusii_simulation_vhdl.pdf

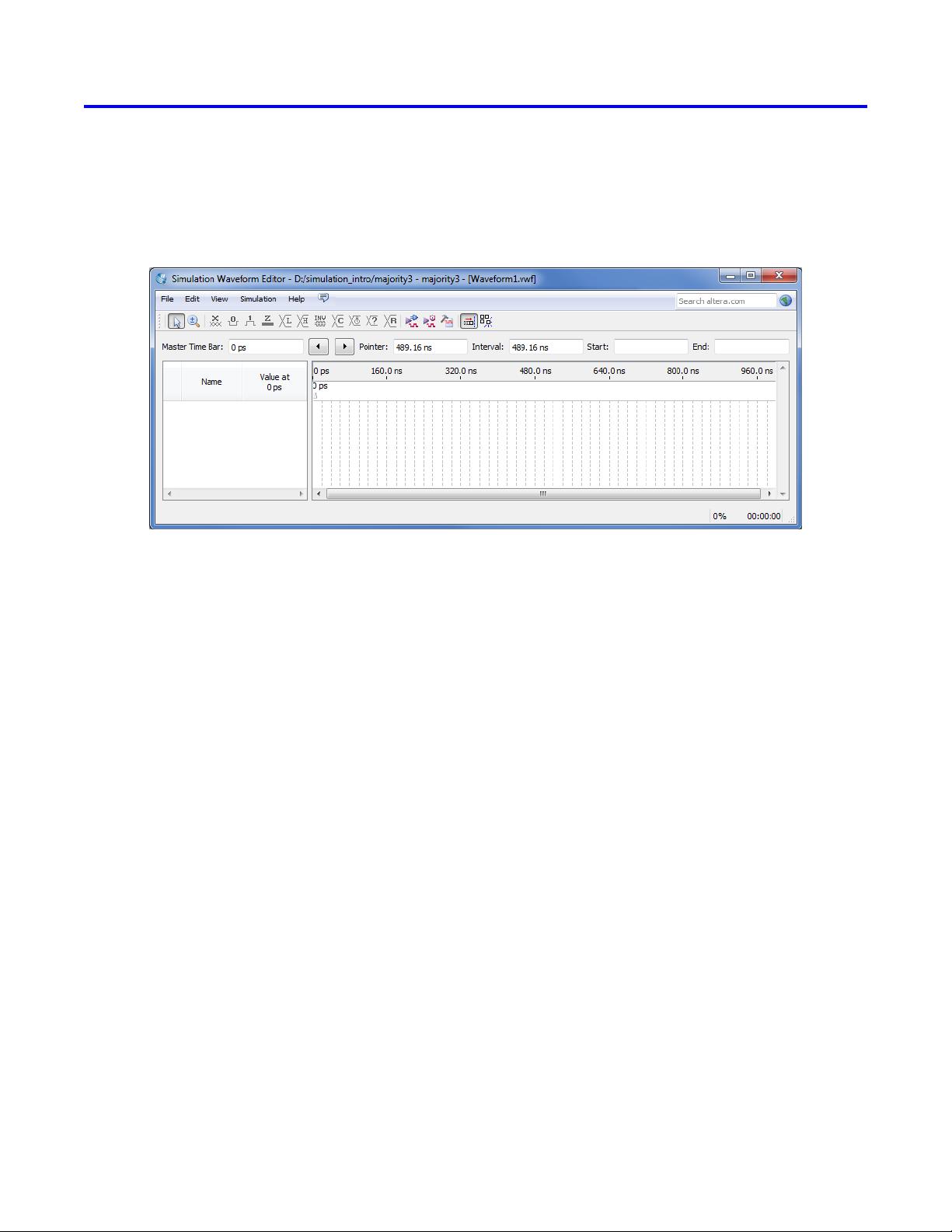

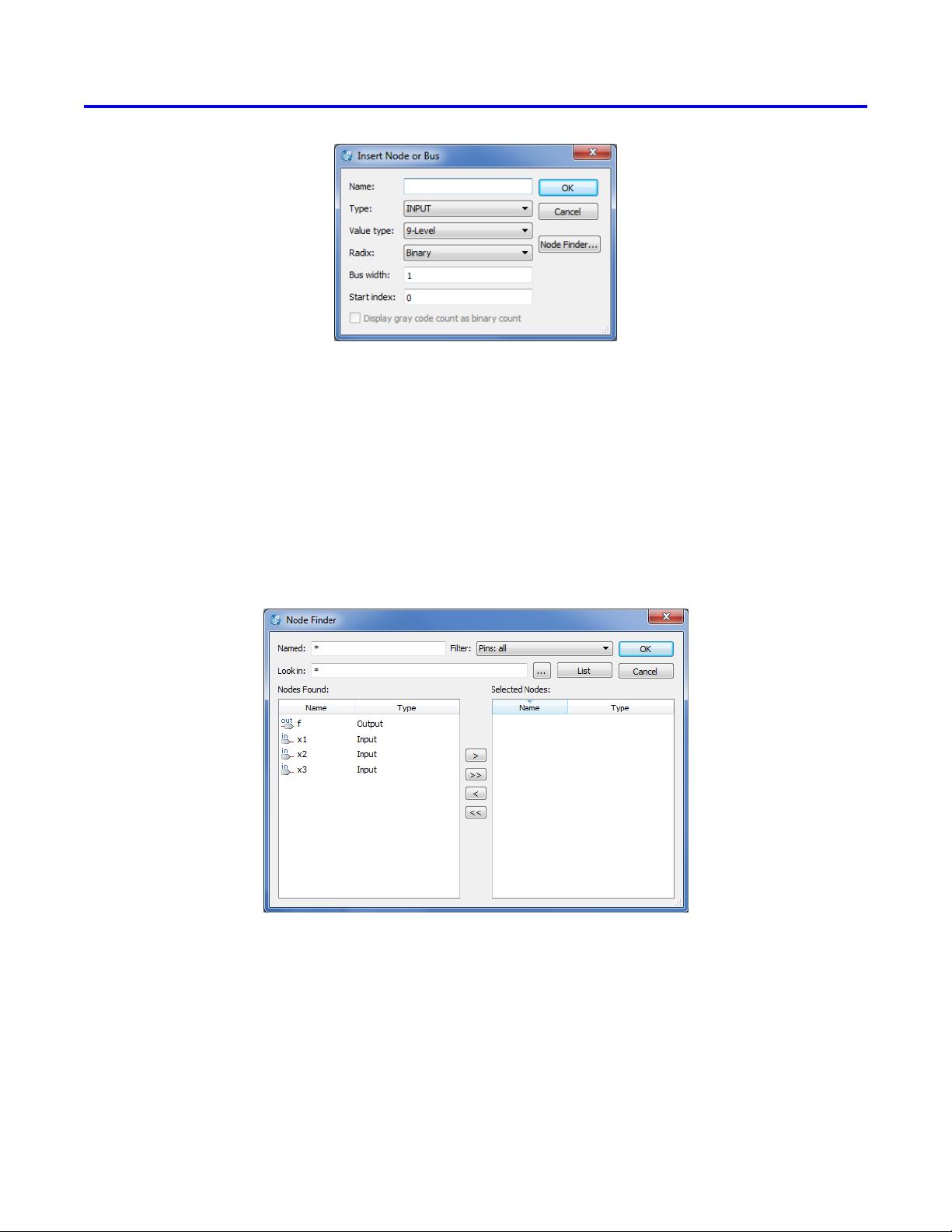

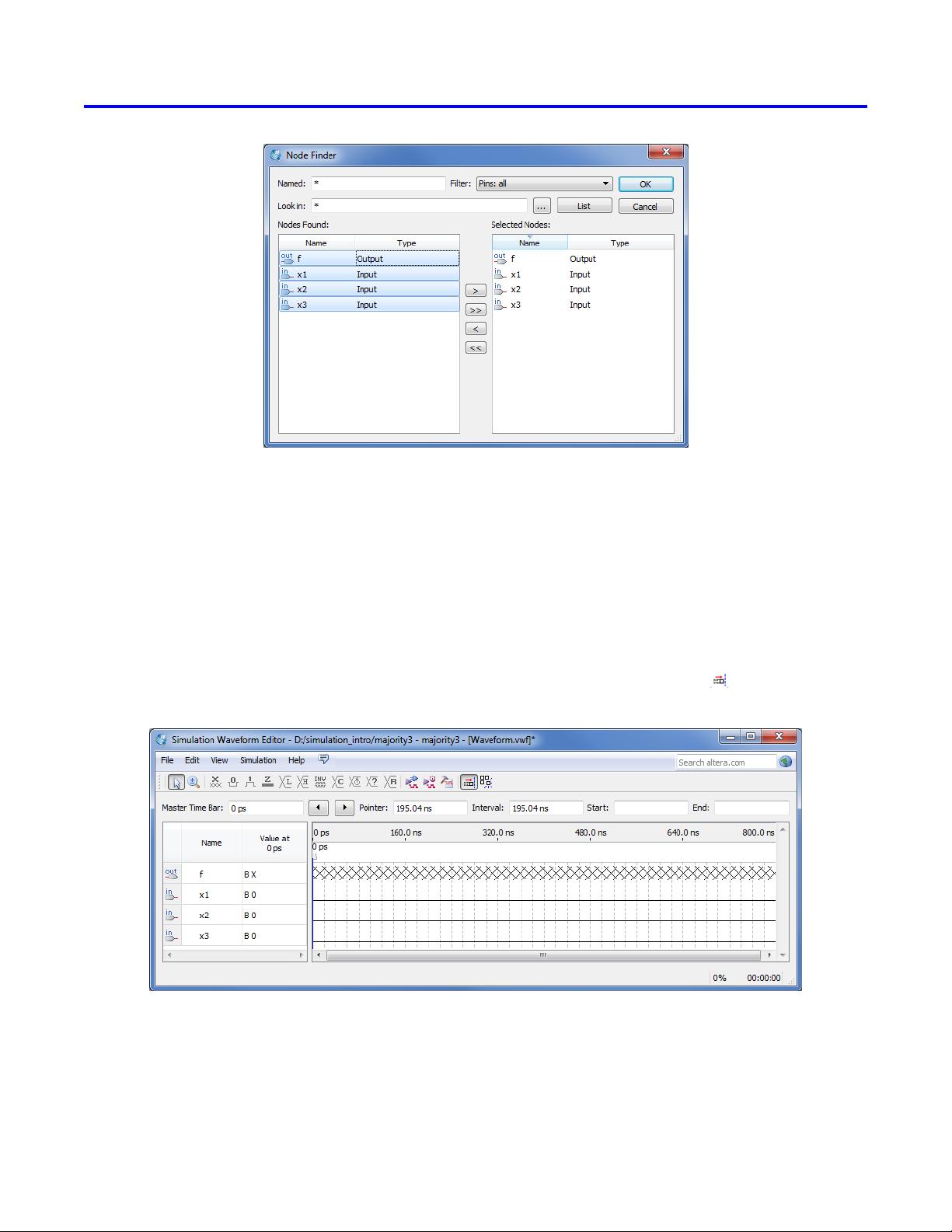

本篇教程文件名为tutorial_quartusii_simulation_vhdl.pdf,主要目的是介绍使用Altera提供的仿真工具——仿真波形编辑器(Simulation Waveform Editor)来模拟VHDL设计的行为。这项仿真技术是确定逻辑电路正确性的一种有效方式,教程面向的是那些正在逻辑电路设计课程中学习的学生。通过本教程的学习,读者将会掌握如何使用Quartus II软件包中与仿真相关的工具来执行VHDL描述的电路仿真。 文档中提到仿真工具是作为Quartus II CAD系统的一部分,并且适用于Quartus II软件版本13.0或更高版本。在进行仿真之前,用户需要应用输入向量(test vectors),即测试向量,到设计好的电路中,然后观察电路产生的响应输出。仿真过程由三个主要部分构成:设计项目、仿真过程以及波形创建。 在设计项目部分,教程展示了一个简单的逻辑电路来说明整个模拟过程,该电路是一个实现三个输入x1、x2和x3的多数逻辑函数(majority function),其VHDL代码如下: ```vhdl LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY majority3 IS PORT (x1, x2, x3: IN STD_LOGIC; f: OUT STD_LOGIC); END majority3; ARCHITECTURE majority3_rtl OF majority3 IS BEGIN f <= (x1 AND x2) OR (x1 AND x3) OR (x2 AND x3); END majority3_rtl; ``` 用户需要将以上代码保存在一个名为majority3.vhd的文件中,并首先在Quartus II项目中实现这个电路。创建新目录(folder)来启动项目后,就可以导入此代码文件。 接下来是仿真部分,文档中介绍了如何在仿真波形编辑器中创建波形,以及如何进行仿真设置。在这一过程中,读者会学习到如何确定测试向量、如何在仿真波形编辑器中绘制测试向量、功能仿真和时序仿真等概念。 功能仿真(Functional simulation)用于验证已综合电路的功能正确性。时序仿真(Timing simulation)则用于验证综合后电路中信号的时间参数。这两种仿真在数字逻辑电路设计中都是至关重要的环节,功能仿真保证电路按照预期逻辑运行,时序仿真确保电路中的信号能够按时到达,满足设计要求。 文档末尾提到,对于偏好使用Verilog硬件描述语言的用户,也有相应的教程可供学习。在教程的给出了结论性评述,强调了仿真在设计周期中的重要性,并建议读者将模拟作为设计和验证过程中的一个常规步骤。 总而言之,通过本次教程,用户不仅能学习到使用Quartus II进行VHDL设计的仿真,而且还会对仿真波形编辑器有深入的理解,这是逻辑电路设计的重要工具。教程适用于对VHDL具有基础了解的读者,有助于他们更好地理解电路的模拟过程。

剩余26页未读,继续阅读

- 粉丝: 0

- 资源: 25

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于c语言的线性链表的实现和应用

- 艾利和iriver Astell&Kern SP3000 V1.20升级固件

- 律师事务所网站建设与管理功能概述

- Python 端口访问邮件提醒工具

- 基于springboot的抗疫物资管理系统

- 基于C语言的二叉树构建及遍历

- 587833617736230KEY_C0091 STM32简易交通灯仿真设计.zip

- 垃圾废物检测19-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 专项资金申报平台需求规范文档解析及关键技术要求

- TMS320F28377原理图

- Docker以及Docker-Compose的安装与卸载

- 艾利和iriver Astell&Kern SP3000 V1.31升级固件

- 基于C语言的图的实现和遍历

- 周勤富恒升职业学校网络安全渗透测试及解决方案第2版.doc

- images(5).zip

- 计算机程序设计员三级(选择题)

信息提交成功

信息提交成功