eetop.cn_综合与Design Compiler(很好).pdf

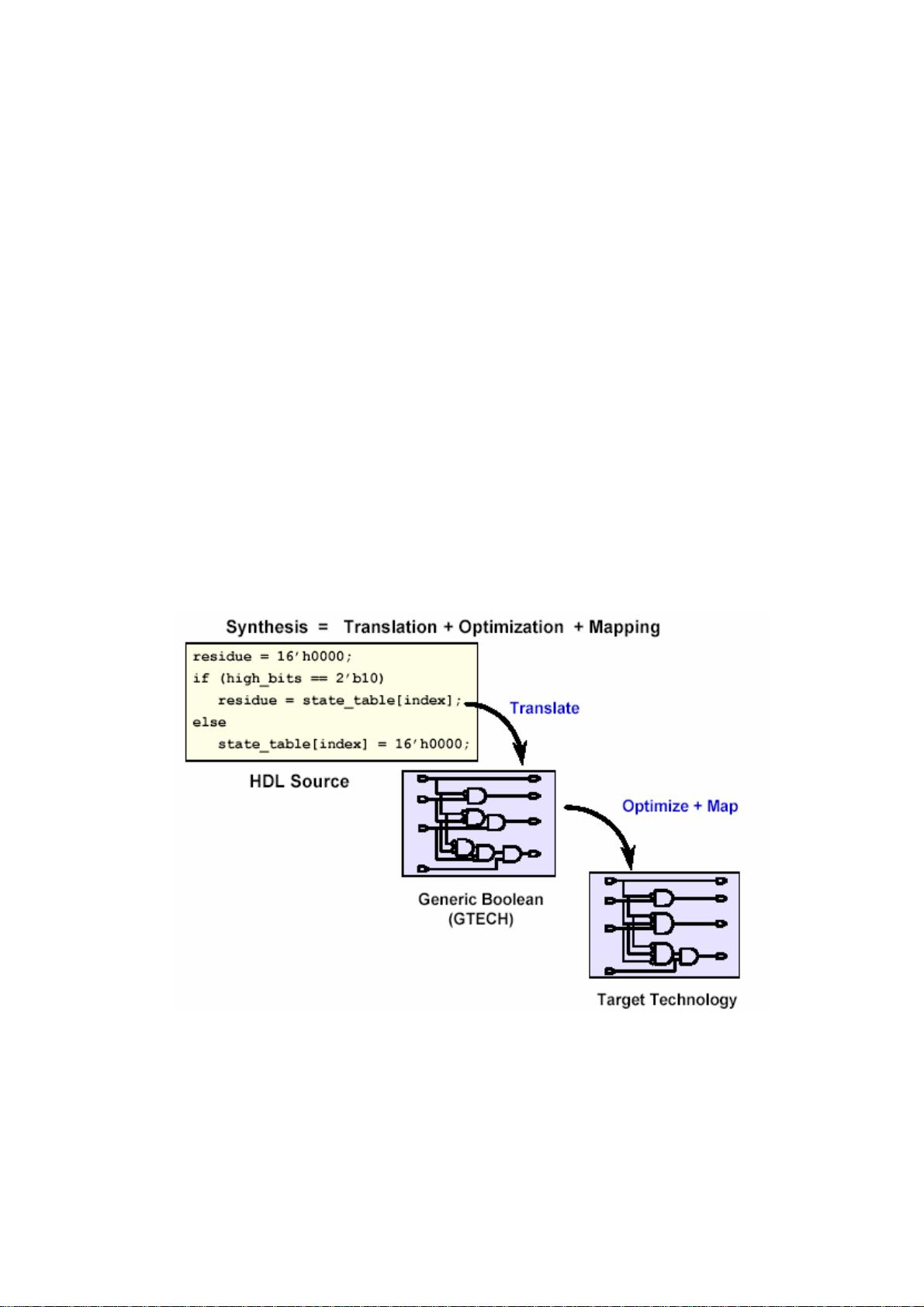

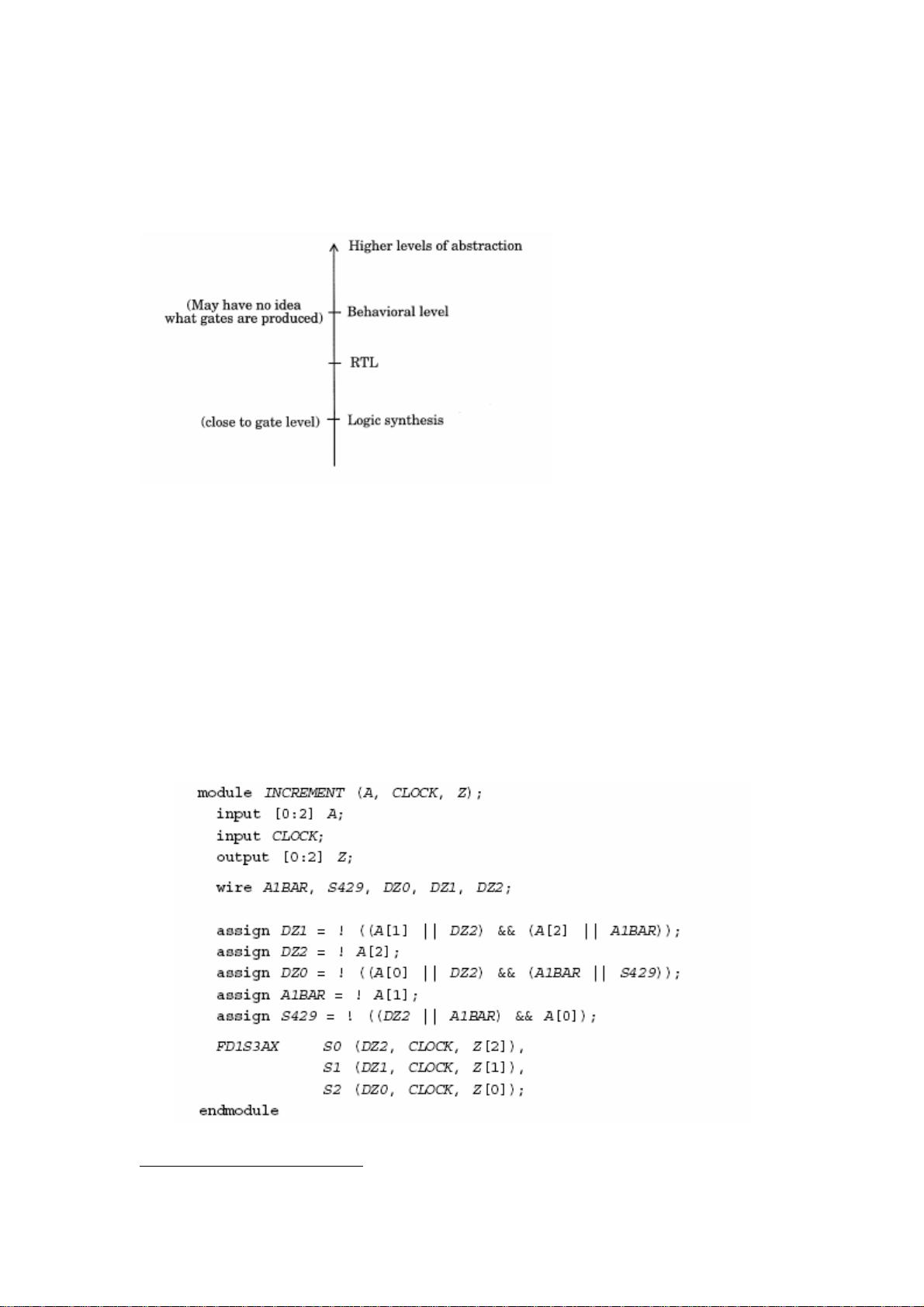

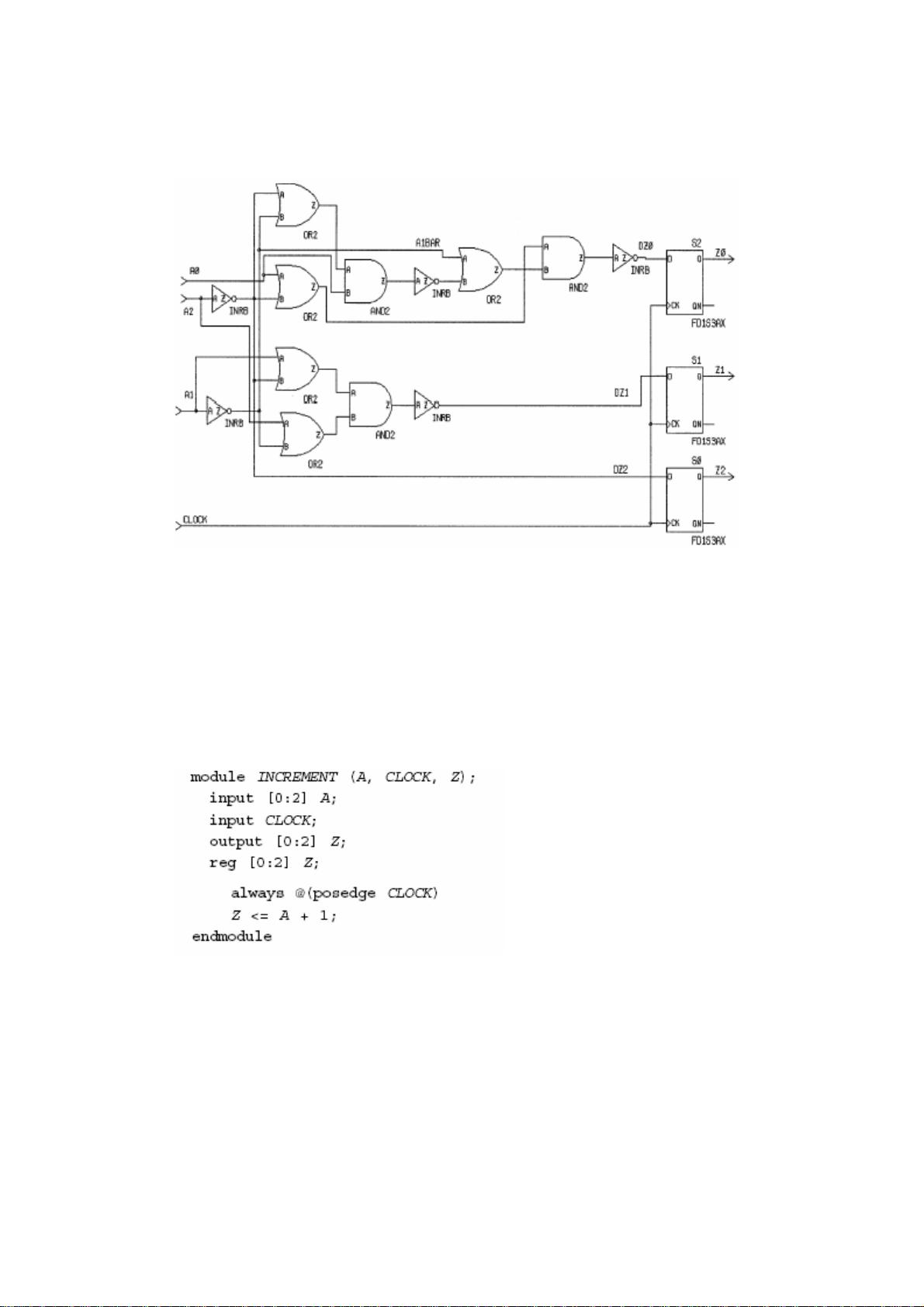

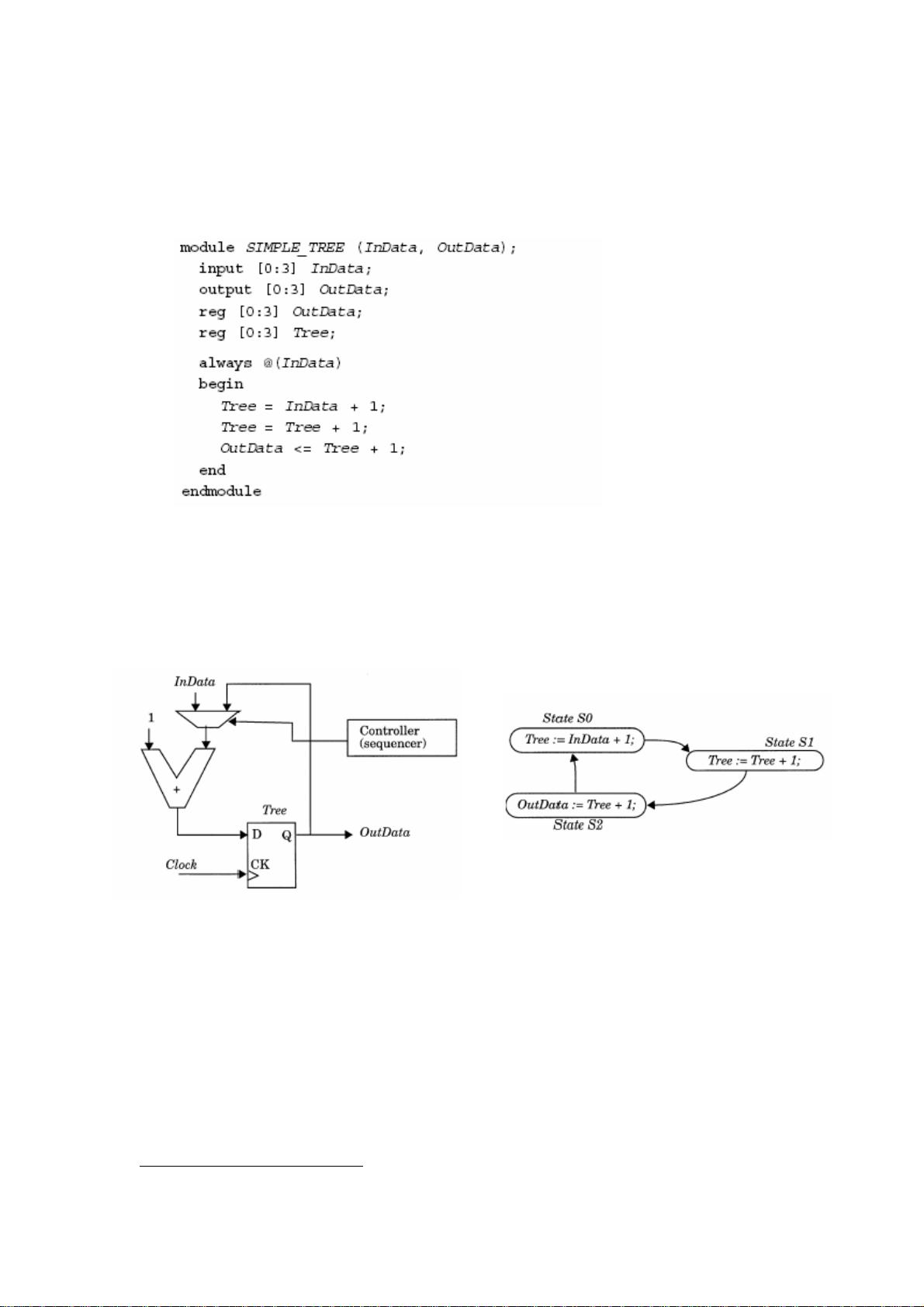

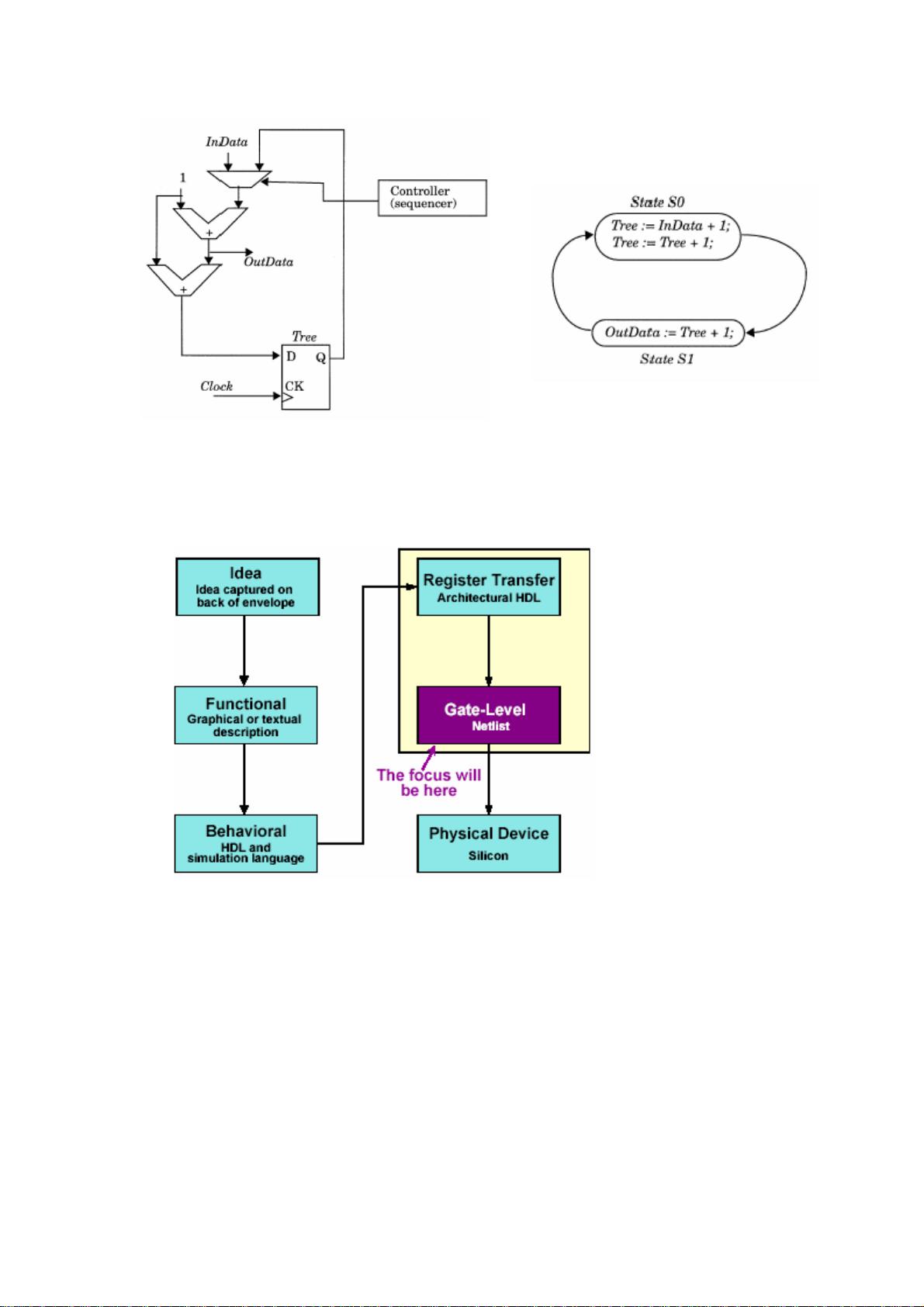

标题:“***_综合与Design Compiler(很好).pdf” 描述:“数字IC后端ASIC中,DC综合入门绝佳手册” 标签:“Design Compiler” 在数字集成电路(IC)的设计流程中,后端ASIC(Application Specific Integrated Circuit)设计占据了非常关键的地位。其中,Design Compiler(DC)是一款由Synopsys公司开发的逻辑综合工具,它在IC设计中扮演着至关重要的角色,特别是在数字逻辑综合方面。从给定的文件内容和标题来看,本手册主要针对数字IC后端设计中Design Compiler的综合流程进行了介绍,是一份入门级的绝佳参考资料。 Design Compiler的功能和特点: 1. RTL到门级综合:Design Compiler能将寄存器传输级(Register Transfer Level,RTL)的代码综合到门级网表。RTL代码通常是用硬件描述语言(HDL),如Verilog或VHDL编写的。综合过程包括优化、转换和映射步骤,以达到面积、速度、功耗等设计要求。 2. 优化技术:Design Compiler采用多种优化技术,如结构优化、逻辑优化、延迟优化等,以提高电路的性能并满足设计约束。 3. 设计约束:设计工程师可以定义一系列的约束条件,如时序约束、面积约束、功耗约束等,并通过Design Compiler进行施加。约束条件将指导综合过程,以确保结果满足设计规格。 4. 技术映射:综合过程中的技术映射指的是将逻辑门映射到特定工艺库中的元件,即逻辑综合后的门级网表需要选择最合适的物理单元(如标准单元库中的基本逻辑门)来实现。 5. 工艺节点:随着IC工艺的发展,Design Compiler支持多种工艺节点。例如,0.18微米、0.25微米、0.5微米甚至更小的深亚微米(DSM)或极深亚微米(VDSM)工艺节点。这些工艺节点要求综合工具考虑更多的物理效应,例如布线延迟、功耗密度和工艺变化对电路性能的影响。 文件内容中还提到了一些Verilog HDL语言的构造,这是在使用Design Compiler进行综合时必须熟练掌握的知识点: 1. always语句:在Verilog中,always语句用于描述时序逻辑和组合逻辑的行为。Design Compiler在综合时会根据always块内的逻辑来实现硬件电路。 2. if、case语句:if和case是Verilog中常用的条件控制语句,它们被用来描述硬件逻辑中的分支结构。Design Compiler会根据这些语句进行逻辑优化,如常量传播、条件逻辑简化等。 3. latch和flip-flop:在数字电路设计中,latch和flip-flop是两种常见的存储元素。latch是电平触发的,而flip-flop是边沿触发的。综合工具需要能够从代码中推断出正确的存储元件,因为它们在电路中有着不同的性能特性。 4. synthesis directive:综合指示(synthesis directive)允许设计工程师通过特定的注释或命令来指导综合过程。例如,“synopsys full_case”指令可以指示综合工具在case语句中自动添加缺失的分支,以确保电路在所有可能的输入条件下都能工作。 5. Verilog代码的其他特性:包括Verilog中对各种数据类型、模块实例化、位宽的处理等,这些都在综合过程中得到实现。 文中还提到了一些专业术语,如物理综合(Physical Synthesis)、物理编译器(Physical Compiler)和DSM、VDSM,这些都与集成电路的物理设计密切相关。物理综合是在综合过程中考虑物理设计的效应,而物理编译器则是一种专门处理物理布局和布线的工具。 文件中还提到DSM和VDSM技术。随着集成电路制造技术的进步,特征尺寸不断缩小,DSM和VDSM技术的引入是为了克服深亚微米工艺中出现的一系列设计挑战,例如短通道效应、串扰、功耗密度等问题。 总结而言,这份手册是学习Design Compiler和数字IC后端ASIC设计不可或缺的入门资源。掌握Design Compiler的基本使用,理解综合过程中的优化技术、设计约束、技术映射以及对HDL代码的综合指示对于进行有效的IC设计至关重要。随着集成电路设计复杂度的增加,了解深亚微米工艺对综合流程的影响,以及学会应对这些挑战,将是IC设计师必须具备的能力。

剩余114页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Keil C51 插件 检测所有if语句

- 各种排序算法java实现的源代码.zip

- 金山PDF教育版编辑器

- 基于springboot+element的校园服务平台源代码项目包含全套技术资料.zip

- 自动化应用驱动的容器弹性管理平台解决方案

- 各种排序算法 Python 实现的源代码

- BlurAdmin 是一款使用 AngularJs + Bootstrap实现的单页管理端模版,视觉冲击极强的管理后台,各种动画效果

- 基于JSP+Servlet的网上书店系统源代码项目包含全套技术资料.zip

- GGJGJGJGGDGGDGG

- 基于SpringBoot的毕业设计选题系统源代码项目包含全套技术资料.zip

信息提交成功

信息提交成功