COA课程设计

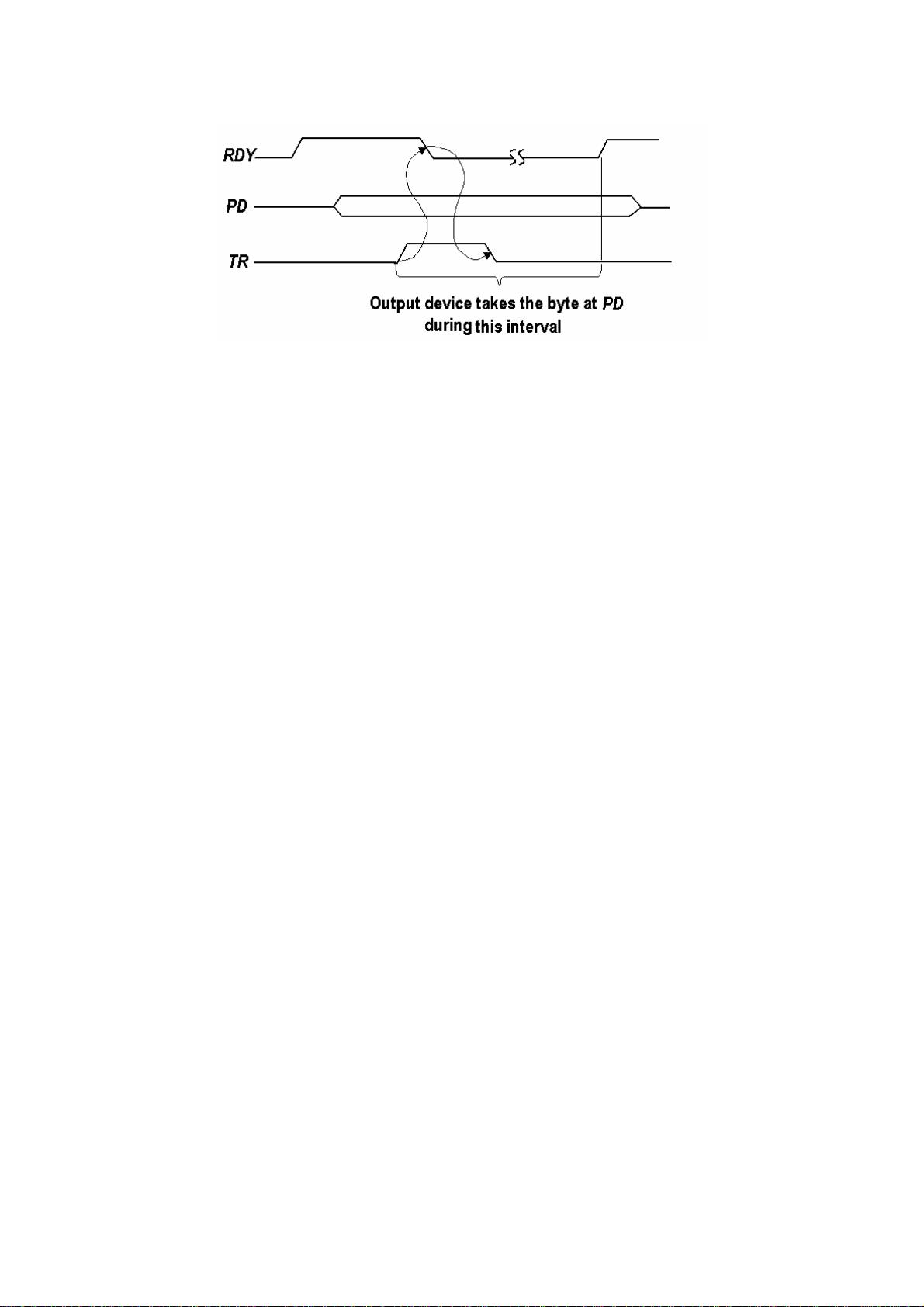

### COA课程设计:CPU设计准则与平行输出控制器(POC)详解 #### CPU设计准则概览 在《计算机组织与架构:为性能而设计》一书中,作者威廉·斯托林斯深入探讨了计算机系统中CPU的设计准则,这对于理解处理器如何高效运行以及如何优化系统性能至关重要。CPU设计涉及多个层面,包括但不限于指令集架构(ISA)、微架构、时序控制、数据路径设计、缓存管理、功耗和散热考虑等。 - **指令集架构(ISA)**:ISA定义了处理器可以执行的指令集,它决定了软件如何与硬件交互。有效的ISA设计应该平衡指令的简洁性与表达力,同时考虑到兼容性和可扩展性。 - **微架构**:微架构关注的是如何实现ISA的物理结构,包括寄存器文件、ALU、内存访问机制等。高效的微架构设计需要考虑到流水线的深度、分支预测、多线程支持等因素。 - **时序控制与数据路径**:这是确保指令正确执行的关键部分。时序控制机制必须精确同步各个硬件组件,而数据路径设计则需确保数据流畅通无阻。 - **缓存管理**:缓存是提高处理器性能的重要手段,通过存储最近或频繁使用的数据,减少主存访问延迟。缓存的设计需考虑容量、关联度、替换策略等因素。 - **功耗与散热**:随着处理器频率和核心数量的增加,功耗和散热成为限制因素。设计时必须考虑到能效比,避免过热导致的性能下降。 #### 平行输出控制器(POC)设计与操作原理 POC是一种常见的I/O模块,作为计算机系统总线与外围设备(如打印机或其他输出设备)之间的接口。POC的设计目标是提供一种高效且可靠的通信机制,使系统能够将数据发送到打印机,同时监测打印机的状态,确保数据传输的准确性和完整性。 - **手握手协议**:POC与打印机之间的通信通过“手握手”协议进行,这是一种确保双方准备就绪的信号交换机制。当打印机准备好接收字符时,它会将RDY(Ready)信号置为1。此时,POC应将字符置于PD(Parallel Data)端口,并通过TR(Transfer Request)端口发出脉冲,通知打印机接收数据。打印机收到数据后,会将RDY信号置为0,直到完成打印,之后再次设置RDY为1,表明已准备好接收下一个字符。 - **缓冲寄存器(BR)与状态寄存器(SR)**:BR用于存储通过系统总线发送的字符,直到该字符被传送给打印机。SR具有多种功能,其中SR7用作系统总线传输至BR的准备标志,类似于打印机RDY信号对于从POC到打印机的数据传输的作用;SR0用于启用或禁用POC的中断请求。当SR0为1时,POC将在准备接收字符时(即SR7为1时)产生中断;若SR0为0,则POC不会产生中断。 #### 设计提示与挑战 设计POC时,设计师需考虑以下几点: - **时序控制**:确保所有信号的同步,特别是在发送数据和响应打印机状态变化时。 - **错误检测与处理**:实施机制来检测和处理潜在的错误,如数据损坏或打印机未准备好接收数据的情况。 - **性能优化**:通过改进数据路径设计、采用更高效的缓存策略和功耗管理方案,提升POC的总体性能。 POC的设计不仅需要对CPU设计准则有深刻理解,还要掌握复杂的信号交互和数据管理技术,以实现高效、可靠的数据传输。这是一项综合性的工程挑战,要求设计师具备扎实的理论基础和实践经验。

剩余17页未读,继续阅读

- 粉丝: 1

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论1