目 录

一、设计任务和要求…………………………………………2

二、系统总体设计方案………………………………………2

三、系统分析与设计…………………………………………

四、系统硬件连接、软件编程和调试………………………

五、改进意见与收获体会……………………………………

六、主要参考资料……………………………………………

1

一、 设计任务和要求

1. 设计任务

① 完成滤波器的选型和滤波器的设计;

② 使用 C5402DSP 实验箱连接电路,编程实现设计的滤波器;

③ 完成滤波器的性能测试;

④ 完成课程设计说明书。

2. 设计要求

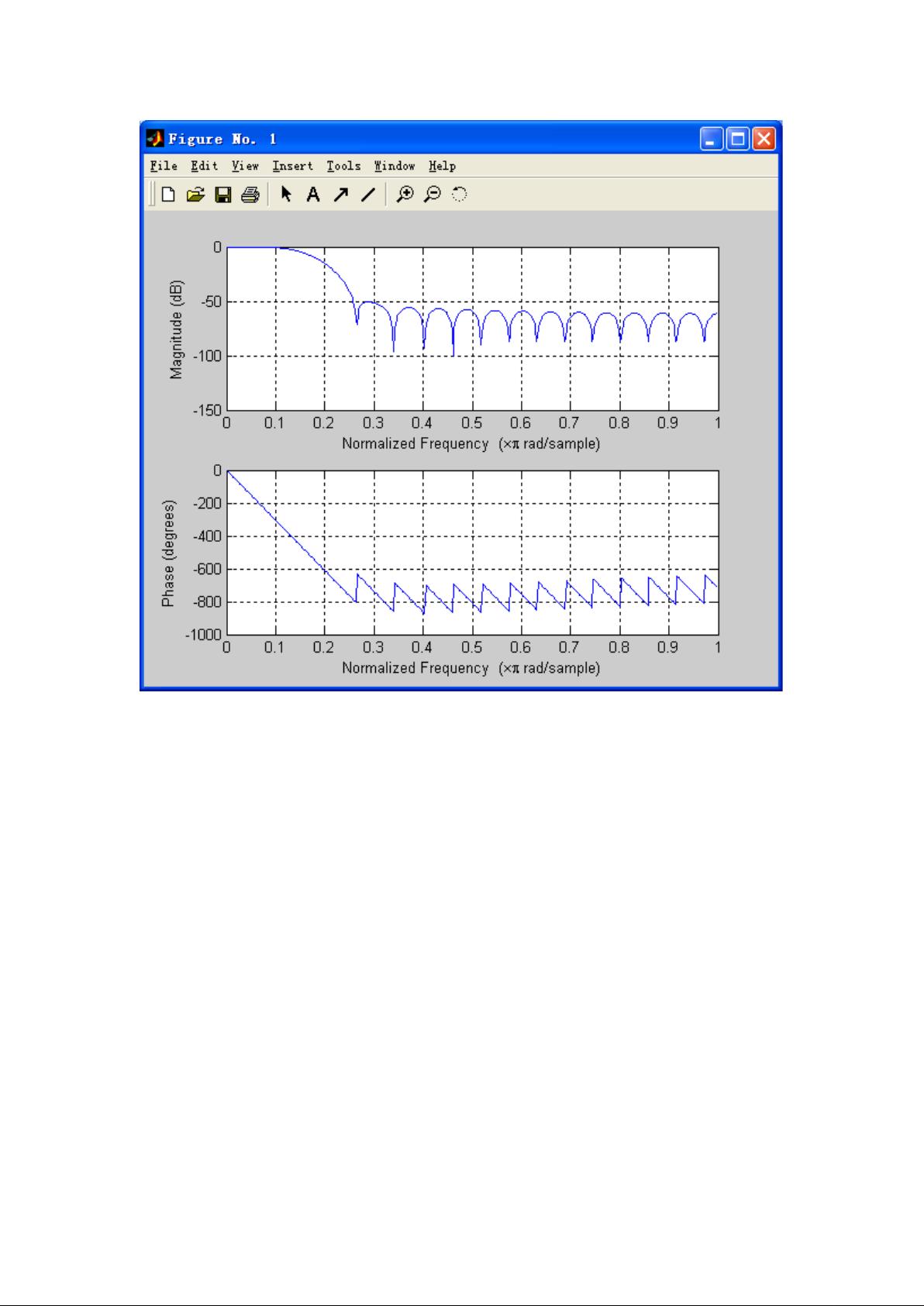

利用 C5402DSP 实验箱设计一个简单数字信号处理系统,指标为:输入信号 AD 采

样频率为 50KHZ;设计一个低通滤波器(FIR),要求截止频率为 4KHZ,过渡

带 2KHZ,阻带衰减大于 40dB;将滤波后的信号通过 DA 输出。

二、 系统总体设计方案

三、 系统分析与设计

1. 硬件电路设计

(1)DSP 芯片

根据设计原理,实现的核心器件采用美国德州仪器公司生产的低功耗定点数字信号处

理

器芯片 TMS320C5402。选择该芯片主要是因为它是目前最常用的低成本 DSP 芯片,而

且包括

以下主要特点:

① 运算速度快,最快可达 532MIPS;

② 多总线结构,片内共有 8 条总线(1 条程序存储器总线、3 条数据存储总线和 4 条

地址总线);

③CPU 采用冯·诺依曼并行结构设计,使其能在一条指令周期内,高速地完成多项算术

运算;

④ 片内集成了 4K×16bitROM 和 16K×16bit 的双存取 RAM;

⑤ 丰富的片上外围电路(通用 I/O 引脚,定时器,时钟发生器, HPI 接口,多通道缓

冲串行口 McBSP)使其与外部接口方便;

⑥3.3V I/O 电压,1.8V 核点压,工作电流平均值为 75mA,其中核 45mA,I/O 约

30mA;⑦ 144 脚 BGA 封装,使体积减少,功耗降低。

2

(2)AD 电路和 DA 电路

AD1674 是美国AD 公司推出的一种12 位带并行微机接口的逐次逼近型模数转

换芯

片。该芯片内部自带采样保持器(SHA)、10 伏基准电压源、时钟源以及可和微处理器

总线

直接接口的暂存/三态输出缓冲器。AD1674 的基本特点和参数如下:

①带有内部采样保持的完全12 位逐次逼近(SAR)型模/数转换器;

②采样频率为100kHz,转换时间为10μs;

③具有±1/2LSB 的积分非线性(INL)以及12 位无漏码的差分非线性(DNL);

④满量程校准误差为0.125%;

⑤内有+10V 基准电源,也可使用外部基准源,四种单极或双极电压输入范围分别为

±5V,±10V,0V~10V 和0V~20V;

⑥数据可并行输出,采用8/12 位可选微处理器总线接口;

⑦内部带有防静电保护装置(ESD),放电耐压值可达4000V;

⑧采用双电源供电:模拟部分为±12V/±15V,数字部分为+5V;

⑨采用28 脚密封陶瓷DIP 或SOIC 封装形式。

⑩功耗低,仅为385mW。

AD767

(3)电源电路

根据DSP芯片工作的电压电流需求,及芯片采用双电源供电对加电顺序的要求,考

虑使用TI公司的电源转换芯片TPS73HD318,其输出电压为一路3.3V、一路1.8V,每路电

源的最大输出电流为750mA,能满足本系统的供电需求。而且TPS73xx具有非常低的静

态电流,能使稳压器输出稳定。

(4)时钟电路

C54xx系列的时钟端子为X1和X2/CLKIN,采用无源晶振提供时钟信号,由于DSP有

一

组端子可以用来调整其工作频率的高低,故对晶振频率大小的选定没有特别的要求,这里

选用10Mhz的晶振。

(5)复位电路

为了克服DSP系统因时钟频率较高导致在运行时可能发生的干扰和被干扰的现象,最

好是使用具有监视(Watchdog)功能的自动复位电路,于是采用专门的自动复位芯片

MAX706。MAX706的电源为3.1V~5.0V,低电平复位输出,复位门限为3.08V。

(6)未用端子处理

根据使用DSP芯片的相关原则,以及芯片手册具体决定未用端子是接上拉电阻还是悬

空。

7、基于上述的各部分电路组成,可以得出DSP数字滤波器的整体硬件电路连线图,

如下所示

2. 程序设计

I、设计思路

⑴在DSP进行数字滤波运算前首先要进行初始化,只有正确设置了DSP的初始状态才

能保证芯片能正常运行。本系统主要进行以下两方面的初始化:

①寄存器初始化:状态寄存器ST0、状态寄存器ST1、处理器模式控制寄存器

PMST、软件等待状态寄存器SWWSR、组交换控制寄存器BSCR和时钟模式寄存器等。

3

②中断矢量表初始化:根据DSP芯片对各中断矢量的设置位置编写一个子程序;设置

PMST控制寄存器;连接时将矢量表重定位到IPTR指定的地址。

⑵其次就是FIR 数字滤波的子程序设计,主要步骤如下:

①查询SPCR11寄存器的第二位,当为1时说明read ready,将DRR11的值读入

AR3所指向的地址,该值为最新的采样值。

②将最新的采样值减去200h,然后AR3的值减1。

③执行MAC指令。

④将累加器的值送给变量Y,并将Y加上200h。

⑤查询SPCR20寄存器的第二位,当为1时说明writeready,将Y值赋给DXR10,该

值为滤波器输出值。

⑥循环执行上面步骤。

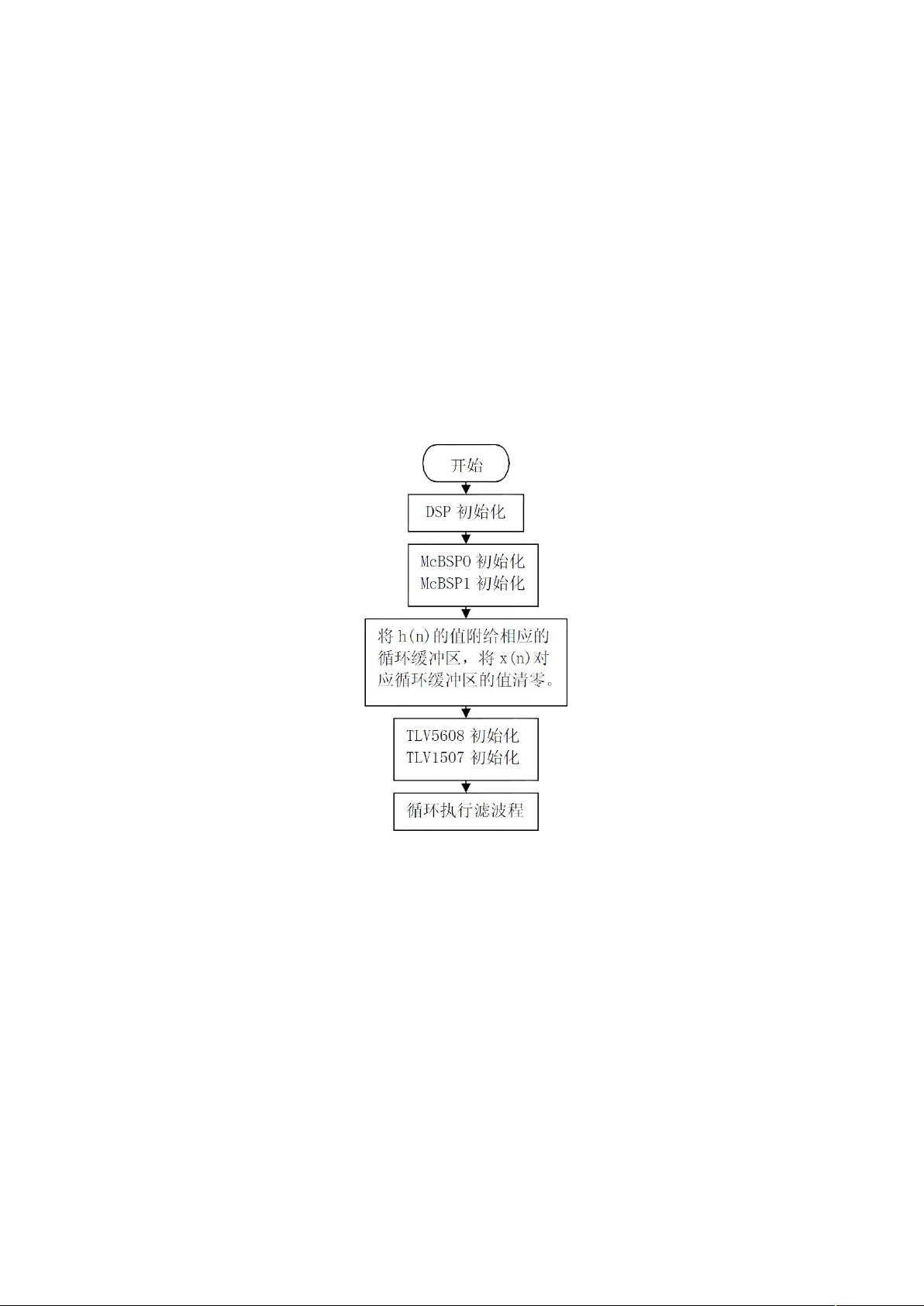

II、程序流程图

依据上述程序设计思路可以得到利用DSP实现FIR滤波器设计的程序流程图,如下:

III. 编辑程序

(1) 试验准备

仿真器的仿真头连接试验箱的 JTAG 口,USB 接头与计算机连接,打开试验箱电源,启

动计算机,启动 Code Composer Studio 2.2。

(2)创建工程:

① 创建新的工程文件:

选择菜单“Projects”的“New…”项。建立新工程文件 exam8.pjt。

展开主窗口左侧工程管理窗口中“Projects”下新建立的“exam8.pjt”,其中各项均为空。

② 新建编辑源程序文件:

选择菜单“File”的“New…”的“Source File…”项,新建源程序文件,保存源程序文件为

exam8.asm。编辑源程序文件内容:

.mmregs

.def start

.global TINT0_ISR

4