第四章 综合与 Design Compiler

综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL 级的

电路转换到门级的过程;Design Compiler 是 Synopsys 公司用于做电路综合的核心工具,它

可以方便地将 HDL 语言描述的电路转换到基于工艺库的门级网表。本章将初步介绍综合的

原理以及使用 Design Compiler 做电路综合的全过程。

4.1 综合综述

4.1.1 综合及其在集成电路设计流程中的地位

4.1.1.1 什么是综合?

综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给

综合工具的一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包

含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑

网络结构的最佳实现方案。即实现在满足设计电路的功能、速度及面积等限制条

件下,将行为级描述转化为指定的技术库中单元电路的连接。

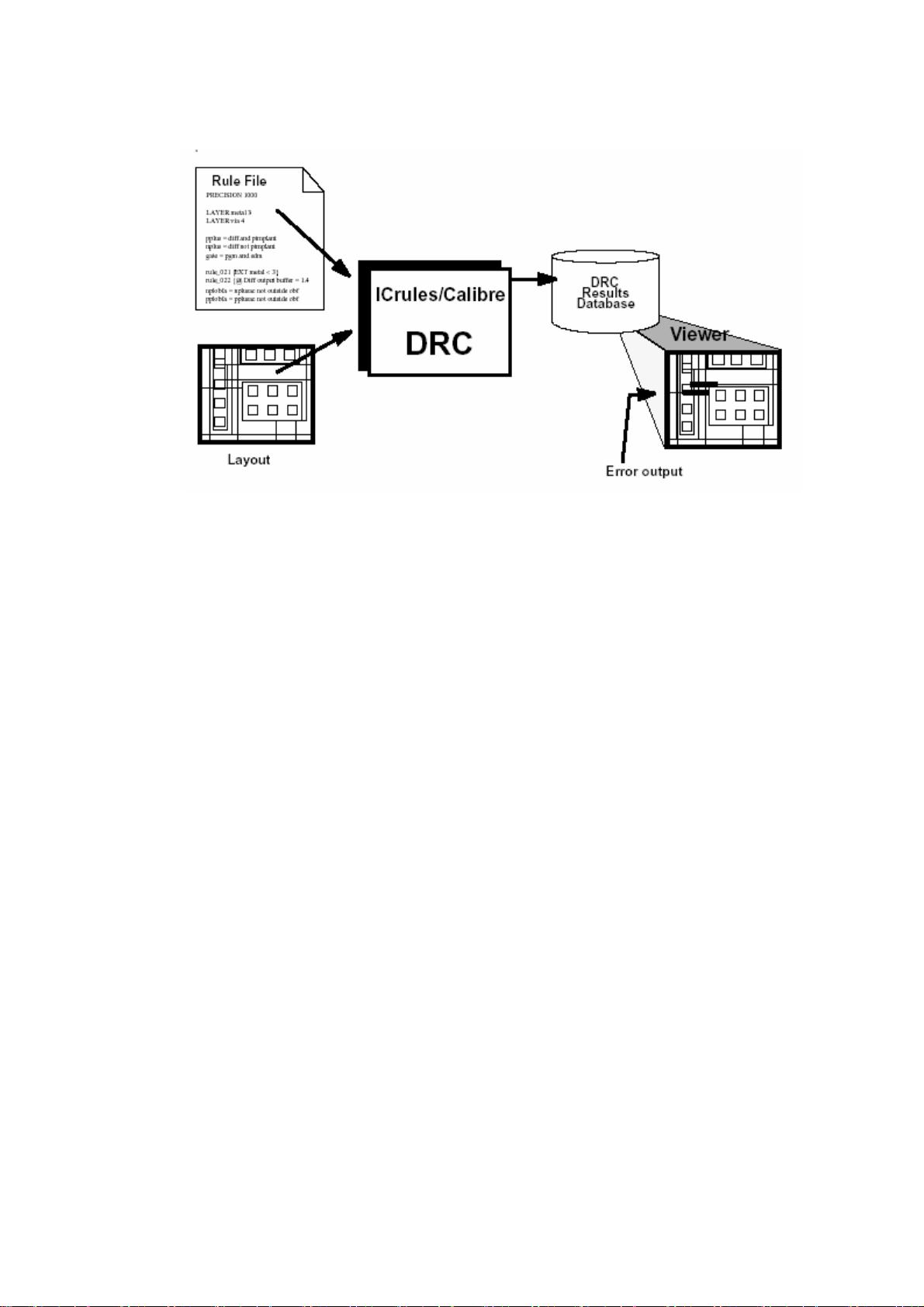

如图 4-1 所示,综合主要包括三个阶段:转换(translation)、优化

(optimization)与映射(mapping)。转换阶段综合工具将高层语言描述的电路用

图 4-1 综合示意图