第 30 卷 第 2 期

2007 年 4 月

电 子 器 件

Chinese J ournal Of Electron Devices

Vol. 30 No. 2

Apr. 2007

Design and Optimization of Large2Capacity NAND Flash Driver Based on WinCE System

Z HA N G Chao , Z HA N G Zhe , HU Chen

(

N ational A S IC S ystem Engineering Center , S outheast Universit y , N anjing 210096 , China

)

Abstract :As NAND Flash has the advantages of fast access time , small size and low cost , it’s the appro2

priate storage device for mass data. This paper designs a solution for large2capacity NAND Flash applica2

tion on WinCE. This paper uses the methods of dynamic sector allocation , bad block management and

buffer cache to improve the driver’s stability and performance. The driver’s throughput can reach 2

Mbyte/ s for reading and 3Mbyte/ s for writing. It has passed the test of CET K.

Key words :mass storage ;dynamic sector allocation ;bad block management ;buffer cache

EEACC :2570

WinCE 系统上大容量 NAND Flash 驱动设计与优化

张 超 ,张 哲 ,胡 晨

(

东南大学国家专用集成电路系统工程中心 ,南京 210096

)

收稿日期 :2006204210

作者简介 :张 超

(

19812

)

,男 ,硕士研究生. 研究方向为微电子与固体电子学、嵌入式系统设计 ,zcclark @hotmail. com;

张 哲

(

19762

)

,男 ,东南大学电子工程系博士研究生、讲师 ;

胡 晨

(

19672

)

,男 ,东南大学电子工程系教授

摘 要 :

NAND Flash 具有存取速度快、体积小、成本低的特点 ,适宜作为海量数据的存储设备. 本文设计了一种大容量

NAND FLASH 在 WinCE 系统上的实现方案. 通过动态扇区分配、坏块管理和数据缓存等技术 ,提高了 Flash 驱动的安全性、

稳定性和读写性能. 经过优化后 ,平均读取速度 2 Mbyte/ s ,写入速度 3 Mbyte1/ s. 整个驱动通过了微软测试工具 CETK

(

WinCE Test kit

)

的测试.

关键词 :大容量存储设备 ;嵌入式 WinCE ;动态扇区分配 ;坏块管理 ;数据缓存

中图分类号 :TP333 文献标识码 :A 文章编号 :100529490( 2007) 0220638205

随着嵌入式系统的发展 ,对大容量低功耗存储

器需求日益增强. 特别是在手持和车载导航领域 ,由

于导航地图往往体积庞大

(

大于 1 GB

)

,因此急需一

种与之相应的大容量存储设备. NAND Flash 以其

低廉的价格 ,快速的擦写速度和相对较小的体积 ,在

该领域显示了极强的竞争力. 同时大容量芯片与小

容量在结构上不尽相同 ,这也造成了两者驱动的差

别. 本文在 XScale 硬件平台和 WinCE 操作系统上

实现了一种高效、安全、稳定的大容量

(

2 GB

)

Nand

Flash 驱动.

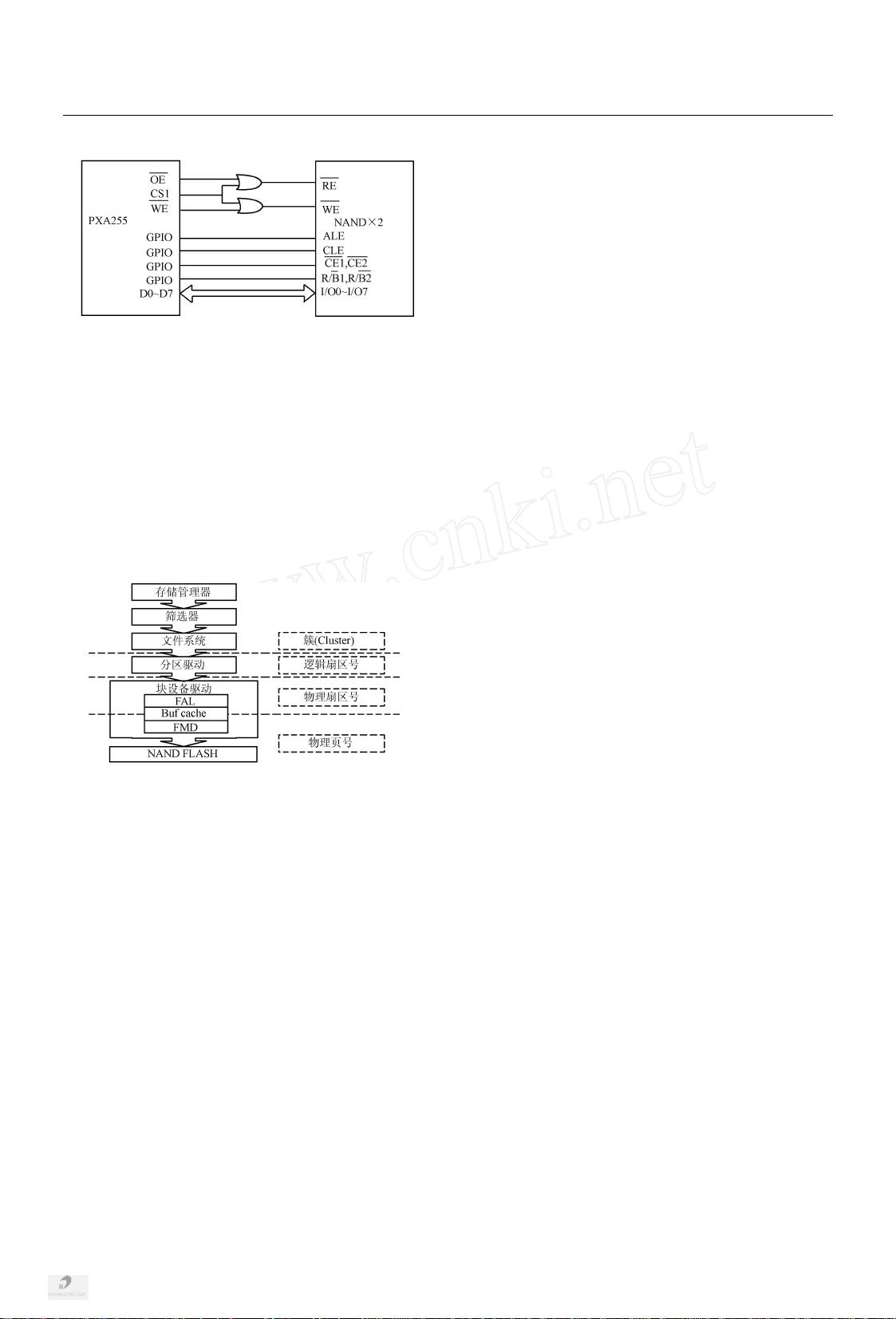

1 硬件方案设计

本文使用 PXA255 处理器

(

400 M Hz

)

、2 MB

NOR Flash

(

E28F128

)

和 64Mbyte SDRAM

(

W981216

)

, NAND Flash 由 两 片 三 星 公 司

K9W8G08U1M

(

1 GB

)

芯 片 级 联 而 成. 每 块

K9W8G08U1M 芯 片 其实 由 两 块 K9 K4 G08U0M

(

512 Mbyte

)

芯片封装而来 , 它们通过两根片选

(

/ CE1和/ CE2

)

分别选通

[1 ]

. 本文采用采用 GPIO 方

式控制读写和擦除时序 ,具体的操作由 FMD 层实

现. AL E

(

地址锁存

)

、CL E

(

命令锁存

)

、R/ B

(

空闲/

忙

)

和 CE 分别通过 PXA255 的 GPIO 口控制 ,同一

时刻最多只能选中一片. 经过软件控制 ,将四片分立

的 512 MB 存储区域组成一块地址连续的 2 GB 存

储块. NAND Flash 的读写控制信号/ RE 和/ WE 由

PXA255 内存控制器的片选

(

CS1

)

和读写信号

(

/ OE

© 1994-2007 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net