没有合适的资源?快使用搜索试试~ 我知道了~

TI-BQ24780s

需积分: 5 0 下载量 94 浏览量

2023-04-10

11:31:09

上传

评论

收藏 1.22MB PDF 举报

温馨提示

试读

56页

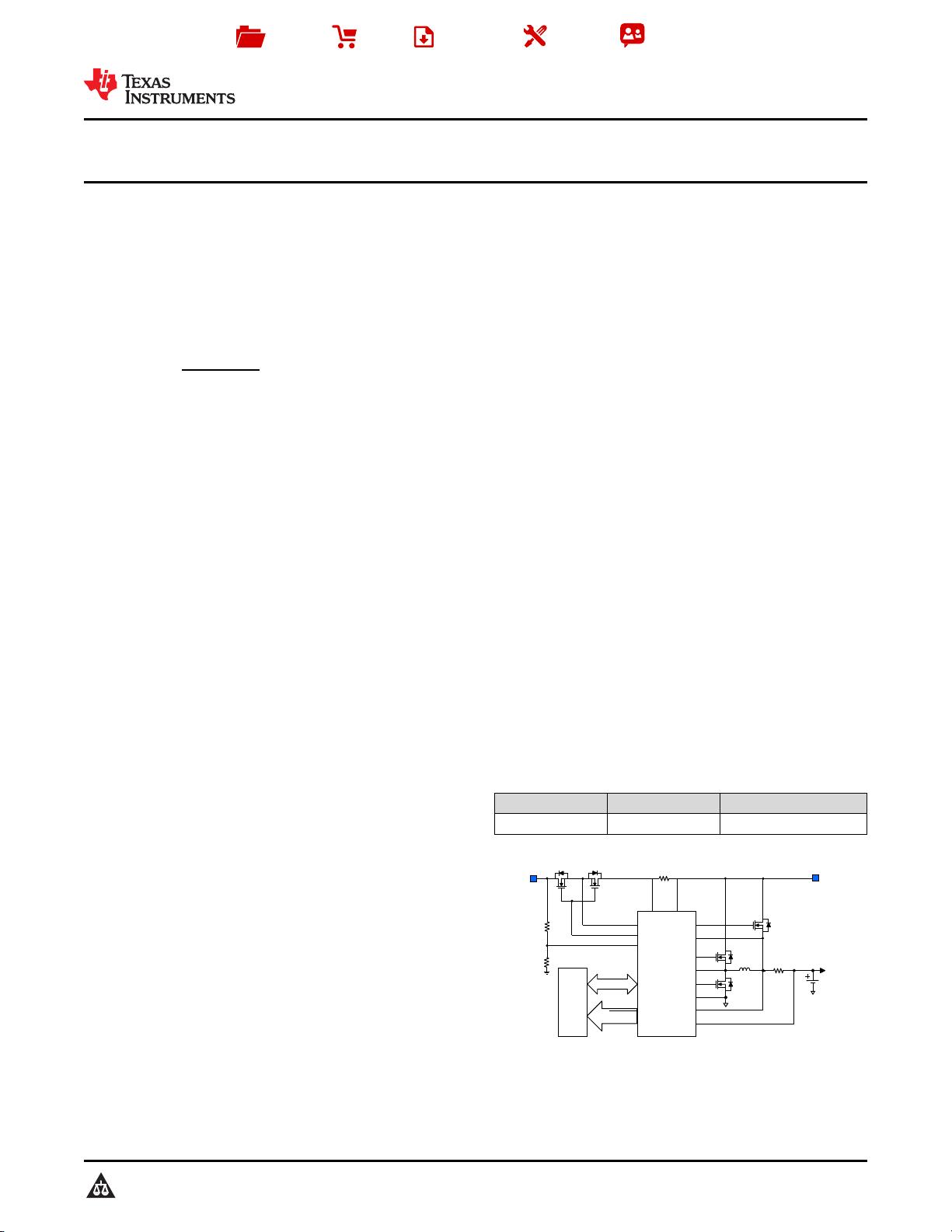

bq24780S 器件是一款高效同步电池充电器, 所含元件 数较少, 适用于空间受限的多化合物电池充电 应用。 bq24780S 器件支持混合动力升压模式(之前称之为 “涡轮升压模式”) 。 当系统电源需求突然超过适配器最 大电源水平时, 可利用此模式对系统放电。 这样适配器 就不会受损。 bq24780S 器件利用两个电荷泵分别驱动 N 通道 MOSFET(ACFET、 RBFET 和 BATFET) , 以便自 动选择系统电源。 笔记本、 超极本、 可拆卸平板电脑和常规平板电脑 • 手持式终端 • 工业用和医疗用设备 • 便携式设备

资源推荐

资源详情

资源评论

R

SR

Adapter

4.5-24V

HOST

bq24780S

Hybrid Power

Boost Charge

Controller

SYS

Battery

Pack

N-FET Driver

N-FET Driver

1S-4S

SMBus

IADP, ,PROCHOT

PMON, IDCHG

SMBus Controls V & I

with high accuracy

Adapter Detection

Enhanced Safety:

OCP, OVP, FET Short

Integration:

Loop Compensation; Soft-Start

Comparator, BTST Diode

R

AC

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLUSC27

bq24780S

ZHCSG48C –APRIL 2015–REVISED MARCH 2017

bq24780S 1 到到 4 节节混混合合动动力力升升压压模模式式电电池池充充电电控控制制器器

((支支持持电电源源监监视视和和处处理理器器热热量量监监视视))

1

1 特特性性

1

• 支持混合动力升压模式的工业创新型充电控制器

– 适配器和电池一同为系统供电,支持 Intel

®

CPU

Turbo 模式

– 进入升压模式的超快瞬态响应时间为 150µs

– 混合动力升压模式由 4.5 至 24V 系统供电

– 1 到 4 节电池由 4.5 至 24V 适配器充电

• 高精度电源和电流监视,实现 CPU 节能

– 全面的 PROCHOT 功能

– ± 2% 电流监视精度

– ± 5% 系统电源监视精度 (PMON)

• 可自动选择适配器或电池作为 NMOS 电源

– ACFET 在 100µs 内快速接通

• 可编程的输入电流、充电电压、充电和放电电流限

值

– ±0.4% 充电电压(16mV 步长)

– ±2% 输入电流(128mA/步长)

– ±2% 充电电流(64mA/步长)

– ±2% 放电电流(512mA/步长)

• 高集成

– 电池 LEARN(学习)功能

– 电池状态监视器

– 升压模式指示器

– 环路补偿

– BTST 二极管

• 针对 过压保护、 过流保护、电池、电感器和

MOSFET 短路保护的增强型安全特性

• 开关频率:600kHz、800kHz 和

1MHz

• 可对 ILIM 引脚进行实时系统控制以限制充电电流

和放电电流

• 适用于 Energy Star 的 0.65mA 适配器待机静态电

流

2 应应用用

• 笔记本、超极本、可拆卸平板电脑和常规平板电脑

• 手持式终端

• 工业用和医疗用设备

• 便携式设备

3 说说明明

bq24780S 器件是一款高效同步电池充电器,所含元件

数较少,适用于空间受限的多化合物电池充电 应用。

bq24780S 器件支持混合动力升压模式(之前称之为

“涡轮升压模式”)。当系统电源需求突然超过适配器最

大电源水平时,可利用此模式对系统放电。这样适配器

就不会受损。

bq24780S 器件利用两个电荷泵分别驱动 N 通道

MOSFET(ACFET、RBFET 和 BATFET),以便自

动选择系统电源。

系统电源管理微控制器可以通过 SMBus 对具有较高调

节精度的输入电流、充电电流、放电电流和充电电压

DAC 进行编程。

bq24780S 器件可监视适配器电流 (IADP)、电池放电

电流 (IDCHG) 和系统电源 (PMON),以便主机根据需

要控制 CPU 速度回落或减少系统电源。

bq24780S 器件可对 1、2、3 或 4 节串联锂离子电池

充电。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

bq24780S WQFN (28) 4.00 × 4.00mm

2

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

2

bq24780S

ZHCSG48C –APRIL 2015–REVISED MARCH 2017

www.ti.com.cn

Copyright © 2015–2017, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 5

6.1 Absolute Maximum Ratings ...................................... 5

6.2 ESD Ratings.............................................................. 5

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information.................................................. 6

6.5 Electrical Characteristics........................................... 6

6.6 Timing Requirements.............................................. 11

6.7 Typical Characteristics............................................ 13

7 Detailed Description............................................ 14

7.1 Overview ................................................................. 14

7.2 Functional Block Diagram ....................................... 15

7.3 Feature Description................................................. 16

7.4 Device Functional Modes........................................ 22

7.5 Programming........................................................... 23

7.6 Register Maps......................................................... 25

8 Application and Implementation ........................ 36

8.1 Application Information............................................ 36

8.2 Typical Applications ................................................ 36

9 Power Supply Recommendations...................... 44

10 Layout................................................................... 44

10.1 Layout Guidelines ................................................. 44

10.2 Layout Examples................................................... 45

11 器器件件和和文文档档支支持持 ..................................................... 48

11.1 接收文档更新通知 ................................................. 48

11.2 社区资源................................................................ 48

11.3 商标 ....................................................................... 48

11.4 静电放电警告......................................................... 48

11.5 Glossary................................................................ 48

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 48

4 修修订订历历史史记记录录

Changes from Revision B (April 2015) to Revision C Page

• 完整数据表到产品文件夹 ........................................................................................................................................................ 1

Changes from Revision A (April 2015) to Revision B Page

• Changed the Description for pin 22 (GND) in the Pin Functions table................................................................................... 4

• Changed the Thermal Pad to PowerPAD in the Pin Functions table..................................................................................... 4

• Changed 16X to 20X on the SRP and SRN pins of the Functional Block Diagram ............................................................ 15

• Changed C4 From: 0.01 μF To: 0.1 μF in 图 17 .................................................................................................................. 36

Changes from Original (April 2015) to Revision A Page

• Changed V

(ACOC)

in the Electrical Characteristics, MIN From: 190% To: 180%, MAX From: 215% To: 220% ..................... 9

• Changed "ChargeOption() bit [0] = 0" To: REG0x12[0] in Enable and Disable Charging.................................................... 17

• Changed " (REG0x12[1])" To: (REG0x12[0]=1) in Enable and Disable Charging ............................................................... 17

• Changed " REG0x12" To: "REG0x12[0]" in Battery Charging ............................................................................................ 22

• Changed Bit [10:9] in Table 9 From: 11: 8 ms To: 11: 800 µs ............................................................................................ 30

• Added sentence to Bit [7:6] in Table 9 " If REG0x15() is programmed..." ........................................................................... 30

• Changed text in Bit [5] of Table 9 From: "write 0x3C[2] = 1." To: "write 0x3C[2] = 0." ........................................................ 30

• Deleted text from Bit [5] of Table 9 "This function is not available in 1s battery."................................................................ 30

Thermal

Pad

28 VCC8IDCHG

1ACN 21 ILIM

27 PHASE9PMON

2ACP 20 SRP

26 HIDRV10PROCHOT

3CMSRC 19 SRN

25 BTST11SDA

4ACDRV 18 BATDRV

24 REGN12SCL

5ACOK 17 BATSRC

23 LODRV13CMPIN

6ACDET 16 TB_STAT

22 GND14CMPOUT

7IADP 15 BATPRES

3

bq24780S

www.ti.com.cn

ZHCSG48C –APRIL 2015–REVISED MARCH 2017

Copyright © 2015–2017, Texas Instruments Incorporated

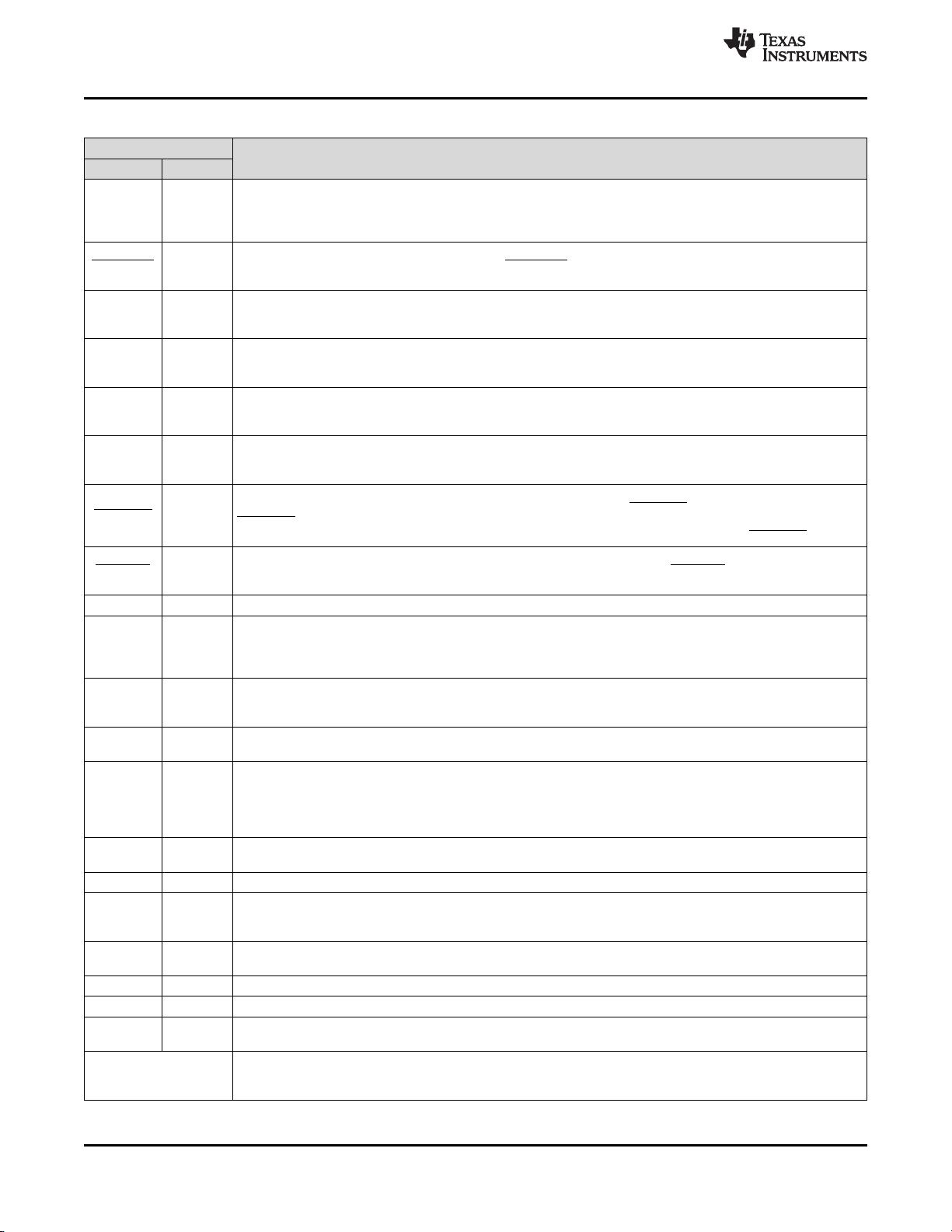

5 Pin Configuration and Functions

RUY Package

28-Pin WQFN

Top View

Pin Functions

PIN

DESCRIPTION

NAME NUMBER

ACN 1

Input current sense resistor negative input. Place an optional 0.01-µF ceramic capacitor from ACN to GND for

common-mode filtering. Place a 0.1-µF ceramic capacitor from ACN to ACP to provide differential mode filtering.

ACP 2

Input current sense resistor positive input. Place a 0.1-µF ceramic capacitor from ACP to GND for common-

mode filtering. Place a 0.1-µF ceramic capacitor from ACN to ACP to provide differential-mode filtering.

CMSRC 3

ACDRV charge pump source input. Place a 4-kΩ resistor from CMSRC to the common source of ACFET (Q1)

and RBFET (Q2) to limit the inrush current on CMSRC pin.

ACDRV 4

Charge pump output to drive both adapter input N-channel MOSFET (ACFET) and reverse blocking N-channel

MOSFET (RBFET). ACDRV voltage is 6 V above CMSRC when ACOK is HIGH. Place a 4-kΩ resistor from

ACDRV to the gate of ACFET and RBFET limits the inrush current on ACDRV pin.

ACOK 5

Active HIGH AC adapter detection open drain output. It is pulled HIGH to external pullup supply rail by external

pullup resistor when a valid adapter is present (ACDET above 2.4 V, VCC above UVLO but below ACOV and

VCC above BAT). If any of the above conditions is not valid, ACOK is pulled LOW by internal MOSFET. Connect

a 10-kΩ pullup resistor from ACOK to the pullup supply rail.

ACDET 6

Adapter detection input. Program adapter valid input threshold by connecting a resistor divider from adapter

input to ACDET pin to GND pin. When ACDET pin is above 0.6 V and VCC is above UVLO, REGN LDO is

present, ACOK comparator, input current buffer (IADP), discharge current buffer (IDCHG), independent

comparator, and power monitor buffer (PMON) can be enabled with SMBus. When ACDET is above 2.4V, and

VCC is above SRN but below ACOV, ACOK goes HIGH.

IADP 7

Buffered adapter current output. V

(IADP)

= 20 or 40 × (V

(ACP)

– V

(ACN)

)

The ratio of 20x and 40x is selectable with SMBus. Place 100-pF (or less) ceramic decoupling capacitor from

IADP pin to GND. This pin can be floating if this output is not in use.

IDCHG 8

Buffered discharge current. V

(IDCHG)

= 8 or 16 × (V

(SRN)

– V

(SRP)

)

The ratio of 8x or 16x is selectable with SMBus. Place 100-pF (or less) ceramic decoupling capacitor from

IDSCHG pin to GND. This pin can be floating if this output is not in use.

4

bq24780S

ZHCSG48C –APRIL 2015–REVISED MARCH 2017

www.ti.com.cn

Copyright © 2015–2017, Texas Instruments Incorporated

Pin Functions (continued)

PIN

DESCRIPTION

NAME NUMBER

PMON 9

Buffered total system power. The output current is proportional to the total power from the adapter and battery.

The ratio is selectable through SMBus. Place a resistor from PMON pin to GND to generate PMON voltage.

Place a 100-pF (or less) ceramic decoupling capacitor from PMON pin to GND. This pin can be floating if this

output is not in use.

PROCHOT 10

Active low, open-drain output of the processor hot indicator. The charger IC monitors events like adapter current,

battery discharge current. After any event in the PROCHOT profile is triggered, a minimum 10-ms pulse is

asserted.

SDA 11

SMBus open-drain data I/O. Connect to SMBus data line from the host controller or smart battery. SMBus

communication starts when VCC is above UVLO. Connect a 10-kΩ pullup resistor according to SMBus

specifications.

SCL 12

SMBus open-drain clock input. Connect to SMBus clock line from the host controller or smart battery. SMBus

communication starts when VCC is above UVLO. Connect a 10-kΩ pullup resistor according to SMBus

specifications.

CMPIN 13

Input of independent comparator. Internal reference, output polarity and deglitch time is selectable by SMBus.

Place a resistor between CMPIN and CMPOUT to program hysteresis when the polarity is HIGH. If comparator

is not in use, CMPIN is tied to ground, and CMPOUT is left floating.

CMPOUT 14

Open-drain output of independent comparator. Place 10-kΩ pullup resistor from CMPOUT to pullup supply rail.

Comparator reference, output polarity and deglitch time is selectable by SMBus. If comparator is not in use,

CMPIN is tied to ground, and CMPOUT is left floating.

BATPRES 15

Active low battery present input signal. Low indicates battery present, high indicates battery absent. The device

exits the LEARN function and turns on ACFET/RBFET within 100 µs if BATPRES pin is pulled high. Upon

BATPRES from LOW to HIGH, battery charging and hybrid power boost mode are disabled. The host can

enable charging and hybrid power boost mode by write to REG0x14() and REG0x15() when BATPRES is HIGH

TB_STAT 16

Active low, open-drain output for hybrid power boost mode indication. It is pulled low when the IC is operating in

boost mode. Otherwise, it is pulled high. Connect a 10-kΩ pullup resistor from TB_STAT pin to the pullup supply

rail.

BATSRC 17 Connect to the source of N-channel BATFET. BATDRV voltage is 6 V above BATSRC to turn on BATFET.

BATDRV 18

Charge pump output to drive N-channel MOSFET between battery and system (BATFET). BATDRV voltage is

6 V above BATSRC to turn on BATFET and power system from battery. BATDRV is shorted to BATSRC to turn

off BATFET. Place a 4-kΩ resistor from BATDRV to the gate of BATFET limits the inrush current on BATDRV

pin.

SRN 19

Charge current sense resistor negative input. SRN pin is for battery voltage sensing as well. Connect SRN pin

with a 0.1-µF ceramic capacitor to GND for common-mode filtering. Connect a 0.1-µF ceramic capacitor from

SRP to SRN to provide differential mode filtering.

SRP 20

Charge current sense resistor positive input. Connect a 0.1-µF ceramic capacitor from SRP to SRN to provide

differential mode filtering.

ILIM 21

Charge current and discharge current limit.V

ILIM

= 20 × (V

SRP

– V

SRN

) for charge current and V

ILIM

= 5 × (V

SRN

–

V

SRP

) for discharge current. Program ILIM voltage by connecting a resistor divider from system reference 3.3-V

rail to ILIM pin to GND pin. The lower of ILIM voltage and 0x14() (for charge) or 0x39 (for discharge) reference

sets actual regulation limit. The minimum voltage on ILIM to enable charge or discharge current regulation is 120

mV.

GND 22

IC ground. On PCB layout, connect to analog ground plane, and only connect to power ground plan through pad

underneath IC.

LODRV 23 Low-side power MOSFET driver output. Connect to low-side N-channel MOSFET gate.

REGN 24

6-V linear regulator output supplied from VCC. The LDO is active when ACDET above 0.6 V, VCC above UVLO.

Connect a ≥ 2.2-µF 0603 ceramic capacitor from REGN to GND. The diode between REGN and BTST is

integrated.

BTST 25

High-side power MOSFET driver power supply. Connect a 47-nF capacitor from BTST to PHASE. The diode

between REGN and BTST is integrated inside the IC.

HIDRV 26 High-side power MOSFET driver output. Connect to the high side N-channel MOSFET gate.

PHASE 27 High-side power MOSFET driver source. Connect to the source of the high-side N-channel MOSFET.

VCC 28

Input supply from adapter or battery. Use 10-Ω resistor and 1-µF capacitor to ground as a low pass filter to limit

inrush current. A diode OR is connected to VCC. It powers charger IC from input adapter and battery.

PowerPAD™

Exposed pad beneath the IC. Analog ground and power ground star-connected only at the PowerPAD plane.

Always solder the PowerPAD to the board and have vias on the PowerPAD plane connecting to analog ground

and power ground planes. It also serves as a thermal pad to dissipate the heat.

5

bq24780S

www.ti.com.cn

ZHCSG48C –APRIL 2015–REVISED MARCH 2017

Copyright © 2015–2017, Texas Instruments Incorporated

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified pin. Consult Packaging

Section of the data book for thermal limitations and considerations of packages.

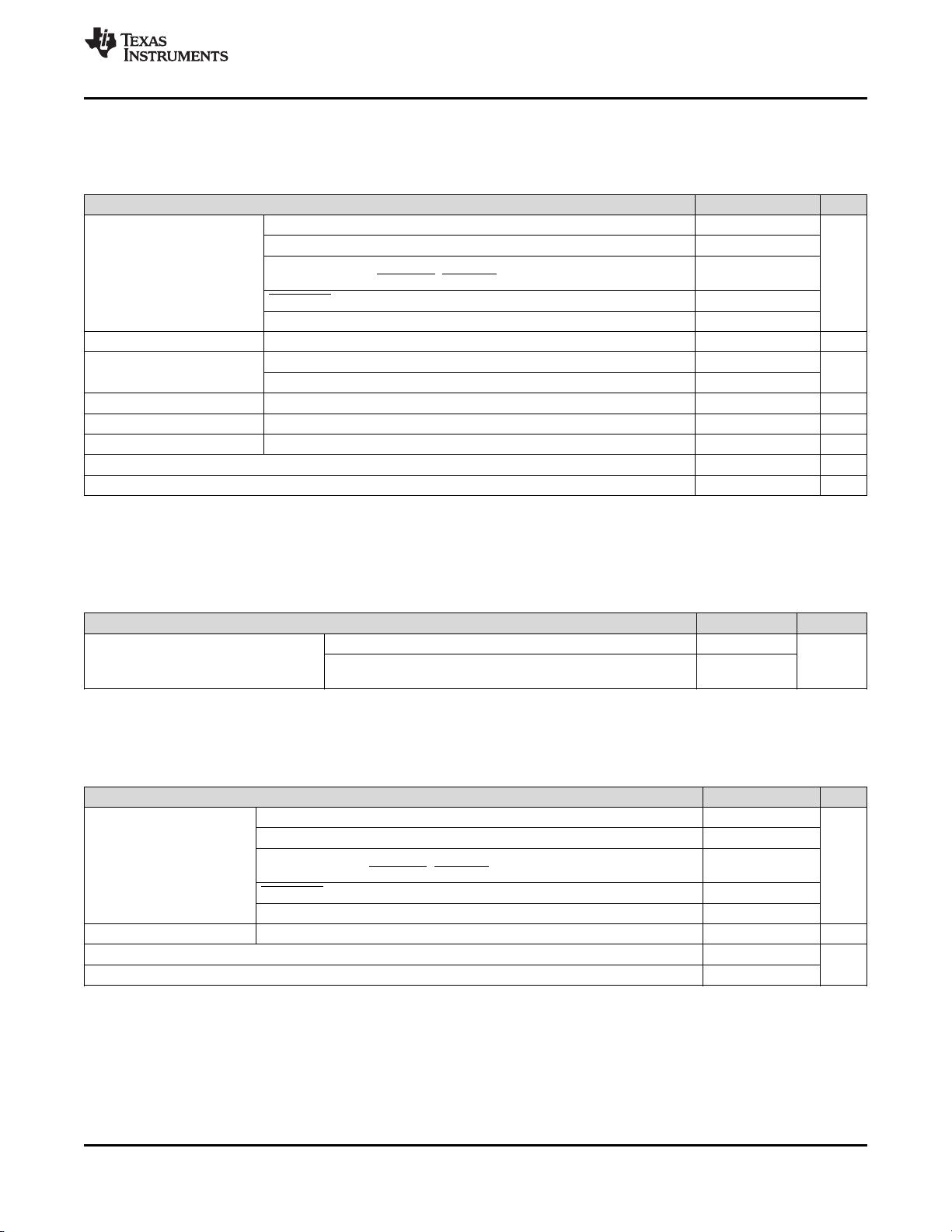

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)(2)

MIN MAX UNIT

Voltage

SRN, SRP, ACN, ACP, CMSRC, VCC, BATSRC –0.3 30

V

PHASE –2 30

ACDET, SDA, SCL, LODRV, REGN, IADP, IDCHG, PMON, ILIM, ACOK,

CMPIN, CMPOUT, BATPRES, TB_STAT

–0.3 7

PROCHOT –0.3 5.7

BTST, HIDRV, ACDRV, BATDRV –0.3 36

Differential voltage BTST-PHASE, HIDRV-PHASE ACDRV-CMSRC, BATDRV-BATSRC –0.3 7 V

Voltage

LODRV (2% duty cycle) –4 7

V

HIDRV (2% duty cycle) –4 36

Voltage PHASE (2% duty cycle) –4 30 V

Voltage REGN (5ms) –0.3 9 V

Maximum differential voltage SRP–SRN, ACP–ACN –0.5 +0.5 V

Junction temperature, T

J

–40 155 °C

Storage temperature, T

stg

–55 155 °C

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±2000

V

Charged device model (CDM), per JEDEC specification JESD22-

C101

(2)

±500

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

Voltage

SRN, SRP, ACN, ACP, CMSRC, VCC, BATSRC 0 24

V

PHASE –2 24

ACDET, SDA, SCL, LODRV, REGN, IADP, IDCHG, PMON, ILIM, ACOK,

CMPIN, CMPOUT, BATPRES, TB_STAT

0 6.5

PROCHOT –0.3 5

BTST, HIDRV, ACDRV, BATDRV 0 30

Maximum difference SRP–SRN, ACP–ACN –0.4 +0.4 V

Junction temperature, T

J

–20 125

°C

Operating free-air temperature, T

A

–40 85

剩余55页未读,继续阅读

资源评论

duni0810

- 粉丝: 10

- 资源: 48

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 蓝桥杯,作为全国软件和信息技术专业人才大赛的知名品牌,旨在促进软件和信息技术领域专业人才培养、推动产学研用有机结合、提高大学生的

- 智能车,作为现代汽车科技的重要发展方向,集合了环境感知、规划决策、多等级辅助驾驶等多种功能于一体,是计算机、现代传感、信息融合、

- 基于SylixOS人脸识别考勤系统用到Qt+OpenCV+ncnn源码+设计文档+算法文档.zip

- 模拟试题三.zip

- Ditto-粘贴板工具

- 毕设基于人脸识别的实验室智能考勤系统设计与开发MFC源码含模型onnx文件.zip

- 数字字母组合字典常用top7000

- 使用Python-OpenCV对多张图片进行全景图像拼接消除鬼影消除裂缝源码.zip

- 百度贴吧12.57.5.0.apk

- JavaScript,简称JS,是一种在Web开发中举足轻重的客户端脚本语言 它最初由Netscape公司的布兰登·艾奇在199

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功