没有合适的资源?快使用搜索试试~ 我知道了~

ug898-vivado-embedded-design

温馨提示

试读

109页

官网可下载,这里提供免费下载,共同学习~

资源推荐

资源详情

资源评论

Vivado Design Suite

User Guide

Embedded Processor

Hardware Design

UG898 (v2014.1) May 9, 2014

Embedded Processor Hardware Design www.xilinx.com 2

UG898 (v2014.1) May 9, 2014

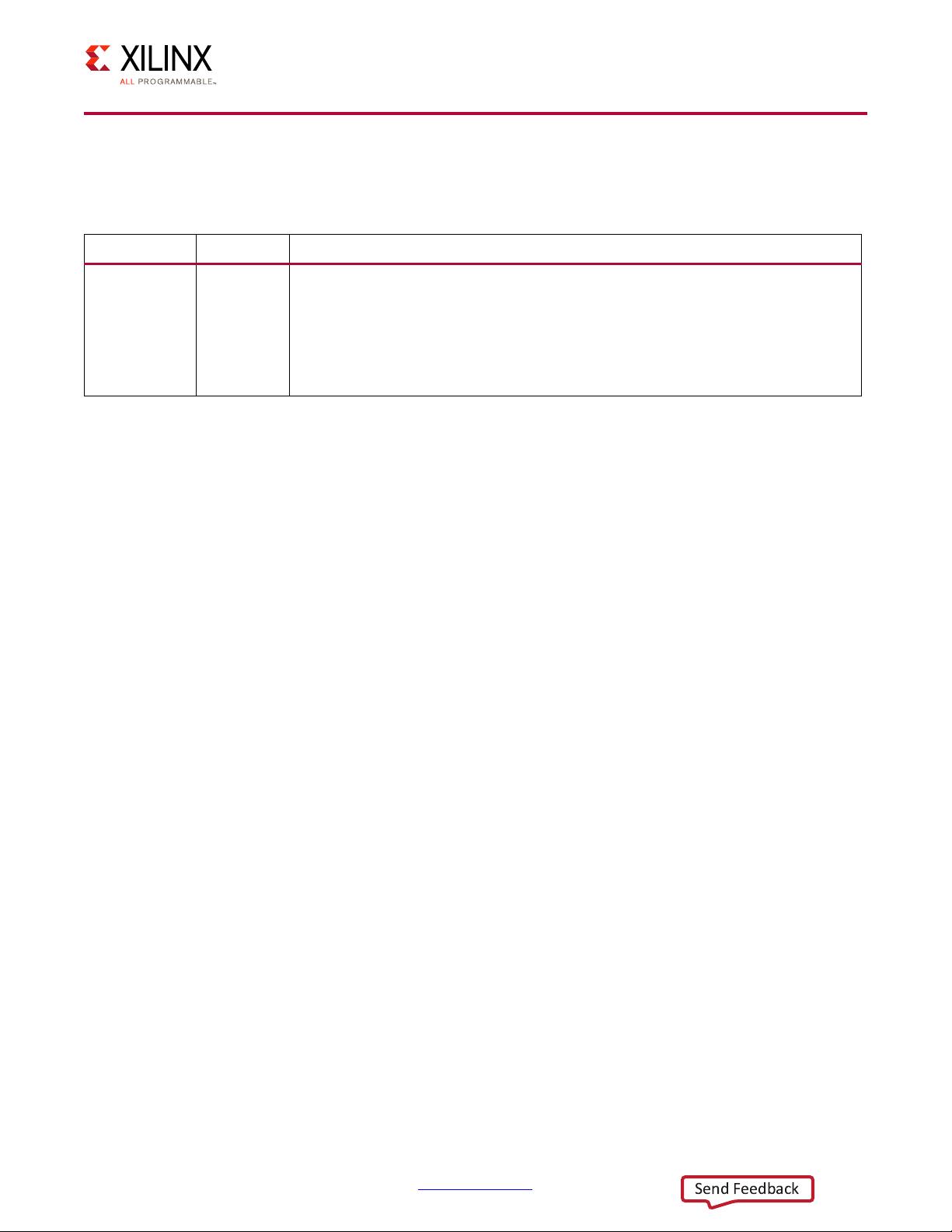

Revision History

The following table shows the revision history for this document.

Date Version Revision

05/09/2014 2014.1 Updated for Vivado Design Suite version 2014.1.

•Updated figures.

• Added PS-PL Cross Trigger Interface, page 30.

• Added Performance Monitoring, page 64

• Added Trace and Profiling, page 64

• Added Cross-Trigger Feature of MicroBlaze Processors, page 66

Send Feedback

Embedded Processor Hardware Design www.xilinx.com 3

UG898 (v2014.1) May 9, 2014

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Hardware and Software Tool Flow Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Starting a Zynq-7000 Based Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 2: Using a Zynq-7000 Processor in an Embedded Design

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Designing for Zynq-7000 Devices in the Vivado IDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Overview of the Zynq Block Design and Configuration Window . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Using the Programmable Logic (PL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Vivado Pin Planner View of PS I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Vivado IDE Generated Embedded Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Using the Software Development Kit (SDK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Chapter 3: Using a MicroBlaze Processor in an Embedded Design

Introduction to MicroBlaze Processor Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Creating an IP Integrator Design with the MicroBlaze Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . 47

MicroBlaze Configuration Window. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Cross-Trigger Feature of MicroBlaze Processors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Custom Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Embedded IP Catalog. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Completing Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Chapter 4: Designing with the MIG Core

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Project Creation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Designing in IP Integrator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Chapter 5: Reset and Clock Topologies in IP Integrator

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

MicroBlaze Design without a MIG Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Send Feedback

Embedded Processor Hardware Design www.xilinx.com 4

UG898 (v2014.1) May 9, 2014

MicroBlaze Design with a MIG Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Zynq Design without PL Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Zynq-7000 Design with PL Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Zynq Design with a MIG core in the PL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Designs with MIG and the Clocking Wizard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Appendix A: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Send Feedback

Embedded Processor Hardware Design www.xilinx.com 5

UG898 (v2014.1) May 9, 2014

Chapter 1

Introduction

Overview

This chapter provides an introduction to using the Xilinx® Vivado® Design Suite flow for

programming an embedded design using the Zynq®-7000 All Programmable (AP) SoC

device or the MicroBlaze™ processor.

Embedded systems are complex. Hardware and software portions of an embedded design

are projects in themselves. Merging the two design components so that they function as

one system creates additional challenges. Add an FPGA design project, and the situation

can become very complicated.

To simplify the design process, Xilinx offers several sets of tools. It is a good idea to know

the basic tool names, project file names, and acronyms for these tools.

The Vivado Integrated Design Environment (IDE) includes the IP integrator tool, which you

can use to stitch together a processor-based design. This tool, combined with the Xilinx

Software Development Kit (SDK), provides an integrated environment to design and debug

microprocessor-based systems and embedded software applications.

Hardware and Software Tool Flow Overview

The Vivado tools provide specific flows for programming, based on the processor. The

Vivado IDE uses the IP integrator with graphic connectivity screens to specify the device,

select peripherals, and configure hardware settings.

The Zynq-7000 AP SoC uses the Vivado IP integrator to capture hardware platform

information in XML format applications, along with other data files. These are used in

software design tools to create and configure Board Support Package (BSP) libraries, infer

compiler options, program the PL, define JTAG settings, and automate other operations

that require information about the hardware. The Zynq-7000 SoC solution reduces the

complexity of an embedded design by offering an ARM Cortex A9 dual core as an

embedded block, and programmable logic along with it, on a single SoC.

Send Feedback

剩余108页未读,继续阅读

资源评论

wyw09032015-09-11现在官网又有新版本了,能看,但是不能下载

wyw09032015-09-11现在官网又有新版本了,能看,但是不能下载 景彡2019-12-17不错,省了跑到官网上下载了,谢谢

景彡2019-12-17不错,省了跑到官网上下载了,谢谢 sccpdiy2017-02-17不错,省了跑到官网上下载了

sccpdiy2017-02-17不错,省了跑到官网上下载了 qq_379741522018-11-30还可以的哈

qq_379741522018-11-30还可以的哈 lingzhi02022016-08-16正在找该方面的资料,谢谢分享

lingzhi02022016-08-16正在找该方面的资料,谢谢分享

DuinoDu

- 粉丝: 150

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功