DE1-SoC Control Panel

www.terasic.com

14-Apr-23

2

CONTENTS

CHAPTER 1

OVERVIEW

........................................................................................................................................ 4

1.1 SYSTEM BLOCK DIAGRAM ........................................................................................................................................ 4

1.2 LEARNING TOPICS ..................................................................................................................................................... 5

1.3 SYSTEM REQUIREMENTS ........................................................................................................................................... 6

1.4 DEVELOPMENT FLOW ............................................................................................................................................... 6

1.5 SET UP THE CONTROL PANEL DEMO .......................................................................................................................... 6

CHAPTER 2

LINUX INSTALLATION

................................................................................................................... 13

2.1 SYSTEM REQUIREMENTS ......................................................................................................................................... 13

2.2 INSTALL VMWARE PLAYER ..................................................................................................................................... 14

2.3 LAUNCH VMWARE .................................................................................................................................................. 19

2.4 INSTALL LINUX UBUNTU DESKTOP ......................................................................................................................... 20

2.5 UPGRADE LINUX SOFTWARE PACKAGE ................................................................................................................... 29

CHAPTER 3

QT CREATOR INSTALLATION

.................................................................................................... 34

3.1 INSTALL TOOL-CHAIN FOR LINUX X86 .................................................................................................................... 34

3.2 DOWNLOAD AND INSTALL QT INSTALLER ............................................................................................................... 36

3.3 LAUNCH QT CREATOR AND CHECK CONFIGURE ..................................................................................................... 45

3.4 HELLO PROGRAM .................................................................................................................................................... 49

CHAPTER 4

ALTERA SOC TOOL-CHAIN INSTALLATION

.......................................................................... 55

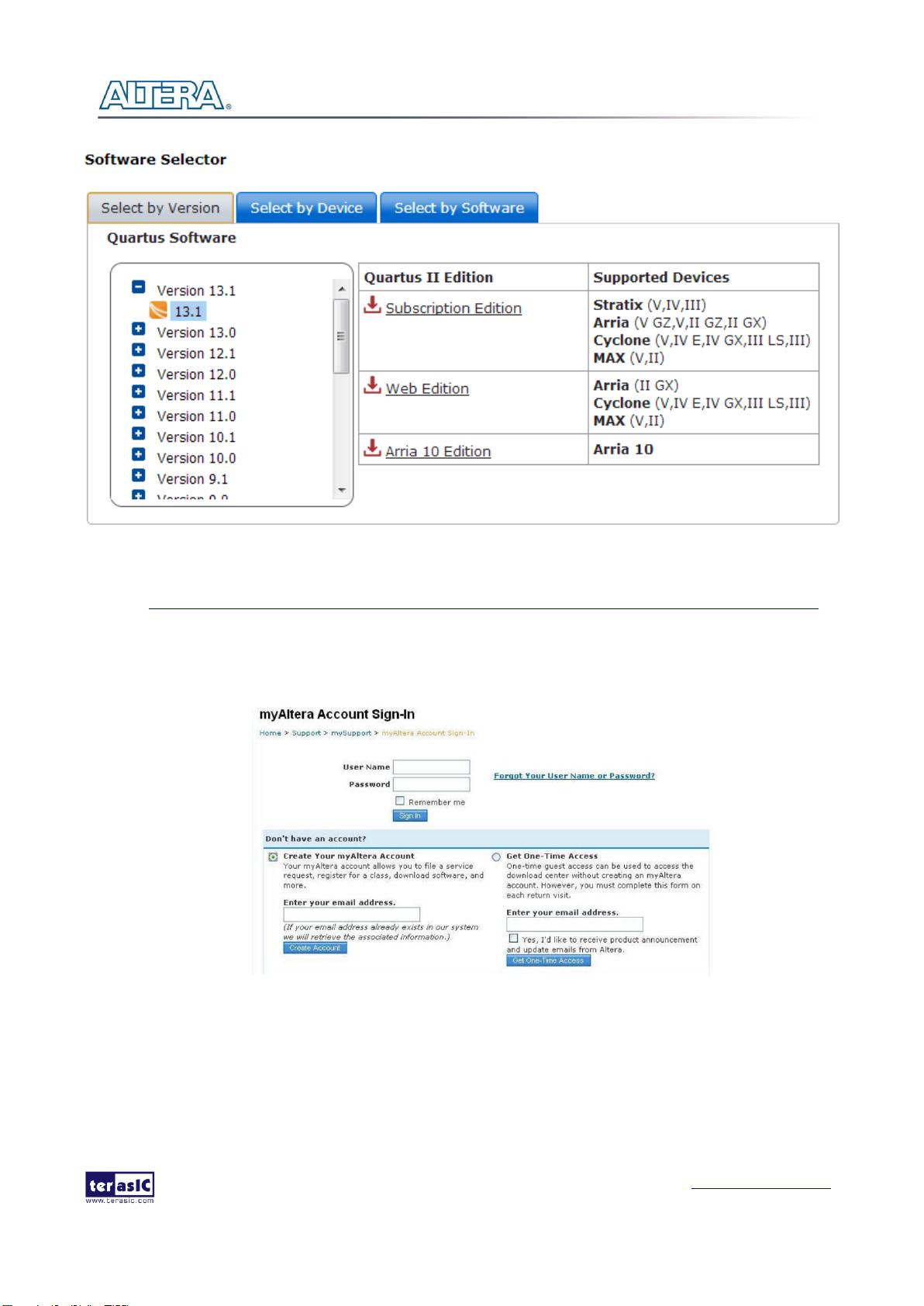

4.1 DOWNLOAD AND INSTALL TOOL-CHAIN ................................................................................................................. 55

4.2 SET UP TOOL-CHAIN PATH....................................................................................................................................... 56

CHAPTER 5

BUILD QT LIBRARY FOR ALTERA SOC

................................................................................... 58

5.1 DOWNLOAD THE QT SOURCE CODE ......................................................................................................................... 58

5.2 CREATE A NEW ‘MKSPECS’ FOR ALTERA SOC ........................................................................................................... 60

5.3 CONFIGURE, BUILD, AND INSTALL QT LIBRARY ....................................................................................................... 62

CHAPTER 6

QT APP FOR ALTERA SOC

......................................................................................................... 68

6.1 SET UP “BUILD & RUN” IN QT CREATOR................................................................................................................. 68

6.2 CROSS-COMPILE THE HELLO PROJECT .................................................................................................................... 72

6.3 EXECUTE HELLO PROGRAM .................................................................................................................................... 76

DE1-SoC Control Panel

www.terasic.com

14-Apr-23

3

CHAPTER 7

CONTROL PANEL QUARTUS PROJECT

.................................................................................. 85

7.1 BUILD QUARTUS PROJECT OF CONTROL PANEL....................................................................................................... 86

7.2 TEST FPGA CONFIGURATION FILE .......................................................................................................................... 86

7.3 MORE ON THE QUARTUS PROJECT OF CONTROL PANEL........................................................................................... 87

CHAPTER 8

CONTROL PANEL QT PROJECT

................................................................................................ 91

8.1 COPY CONTROL PANEL QT PROJECT ....................................................................................................................... 97

8.2 BUILD CONTROL PANEL QT PROJECT.................................................................................................................... 102

8.3 EXECUTE CONTROL PANEL PROGRAM................................................................................................................... 107

8.4 MORE ON THE CONTROL MODULE OF CONTROL PANEL ........................................................................................ 108

DE1-SoC Control Panel

www.terasic.com

14-Apr-23

4

Chapter 1

Overview

The Altera Cyclone V SoC Development Kit (DE1-SoC), a robust platform that is built around

Altera System-on-Chip (SoC) FPGA which combines the dual-core Cortex-A9 embedded cores

with industry leading programmable logic for ultimate design flexibility. Altera’s SoC FPGA

integrates Hard Processor System (HPS) consisting of processor, peripherals and memory interfaces

tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. Other than

having the Altera SoC FPGA, DE1-SoC FPGA development board is equipped with hardware, such

as DDR3 memory, video and audio capabilities, Ethernet networking, and much more that promise

many exciting applications.

To demonstrate the power of the SoC FPGA on the DE1-SoC FPGA development board, we have

created a “Control Panel” program, a board utility software that uses ARM to access various

peripherals that belong both to the Hard Processor System (HPS) and the FPGA. This demo is

particularly useful for anyone who is interested in the SoC FPGA structure and development of

future SoC applications.

This scope of this tutorial is to help users understand and learn how to build the board utility

“Control Panel” on the DE1-SoC FPGA development board in a step-by-step fashion. To boost user

confidence while following the instructions, we provide screenshots of steps needed to be followed.

This helps users debug if they encounter any problems during the learning process. Users should

have basic concepts toward building their own applications once they have finished working with

the whole tutorial. Also, users should find this tutorial self-explanatory and self-contained as we

hope that lots of creative projects can be inspired as a result of this.

1

1

.

.

1

1

S

S

y

y

s

s

t

t

e

e

m

m

B

B

l

l

o

o

c

c

k

k

D

D

i

i

a

a

g

g

r

r

a

a

m

m

Figure 1-1 shows the block diagram of the Control Panel where user can see the Control Panel

program is running on Linux on the left-hand side. The program GUI is built based on QT library

and it can access the FPGA resources through the AXI bus. The Linux Frame Buffer Display

DE1-SoC Control Panel

www.terasic.com

14-Apr-23

5

hardware is implemented based on Altera VIP suite and HPS DDR3 SDRAM memory is used as

frame buffer.

Figure 1-1 Block Diagram of the Control Panel

1

1

.

.

2

2

L

L

e

e

a

a

r

r

n

n

i

i

n

n

g

g

T

T

o

o

p

p

i

i

c

c

s

s

To give users an outline what they will learn in this manual, here we provide a list of topics that will

be covered and explained:

Install a virtual machine on Windows Host

Install a Linux x86 under virtual machine

Install QT Designer on Linux x86

Create and build a QT hello program for Linux x86

Cross-compile to build QT library for Altera SoC ARM

Cross-compile to build QT Application for Altera SoC ARM

Create and build a Quartus Project for Altera SoC FPGA

Launch QT application on Altera SoC FPGA board