I2C-verilog-(非常详细的i2c学习心得)

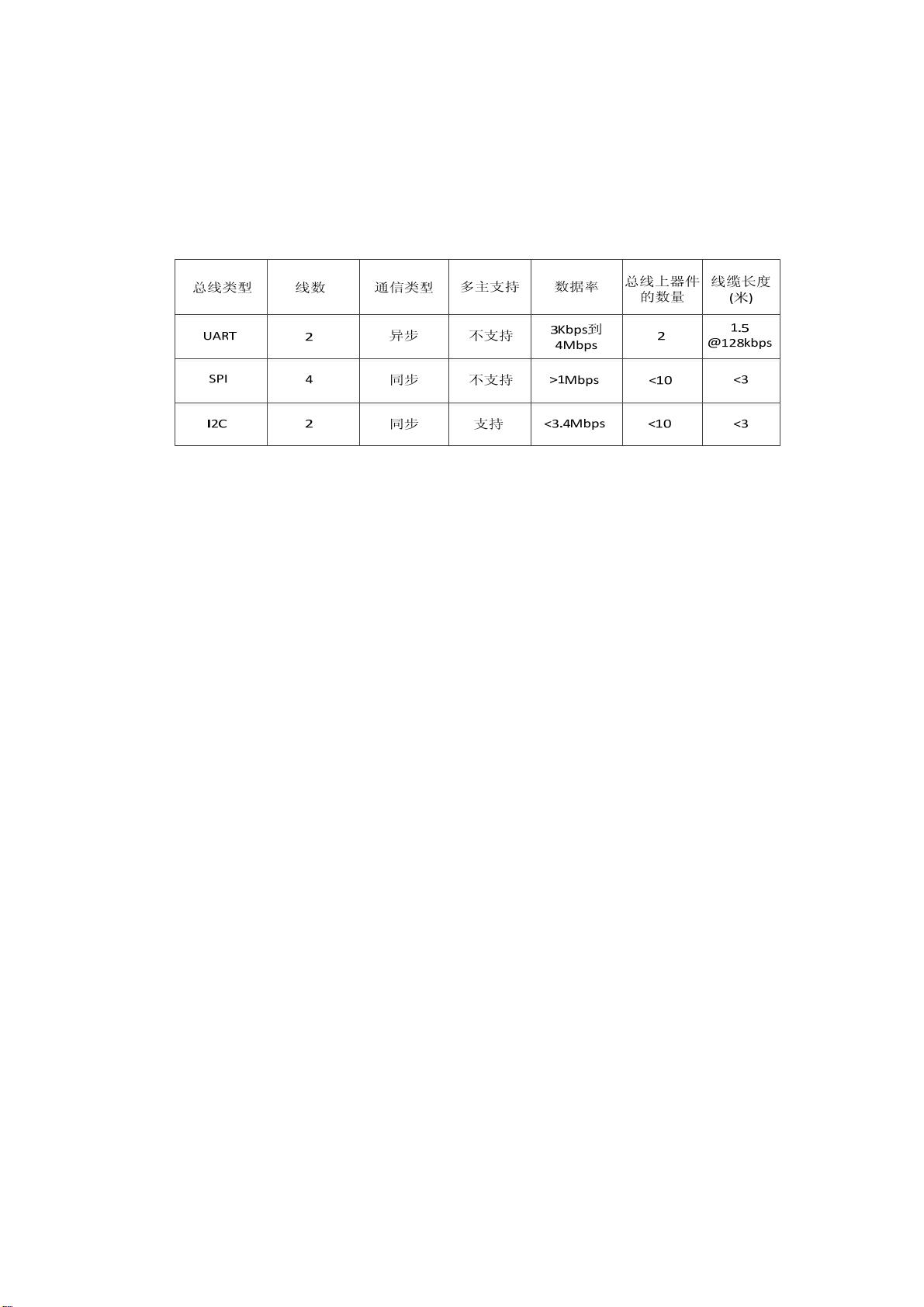

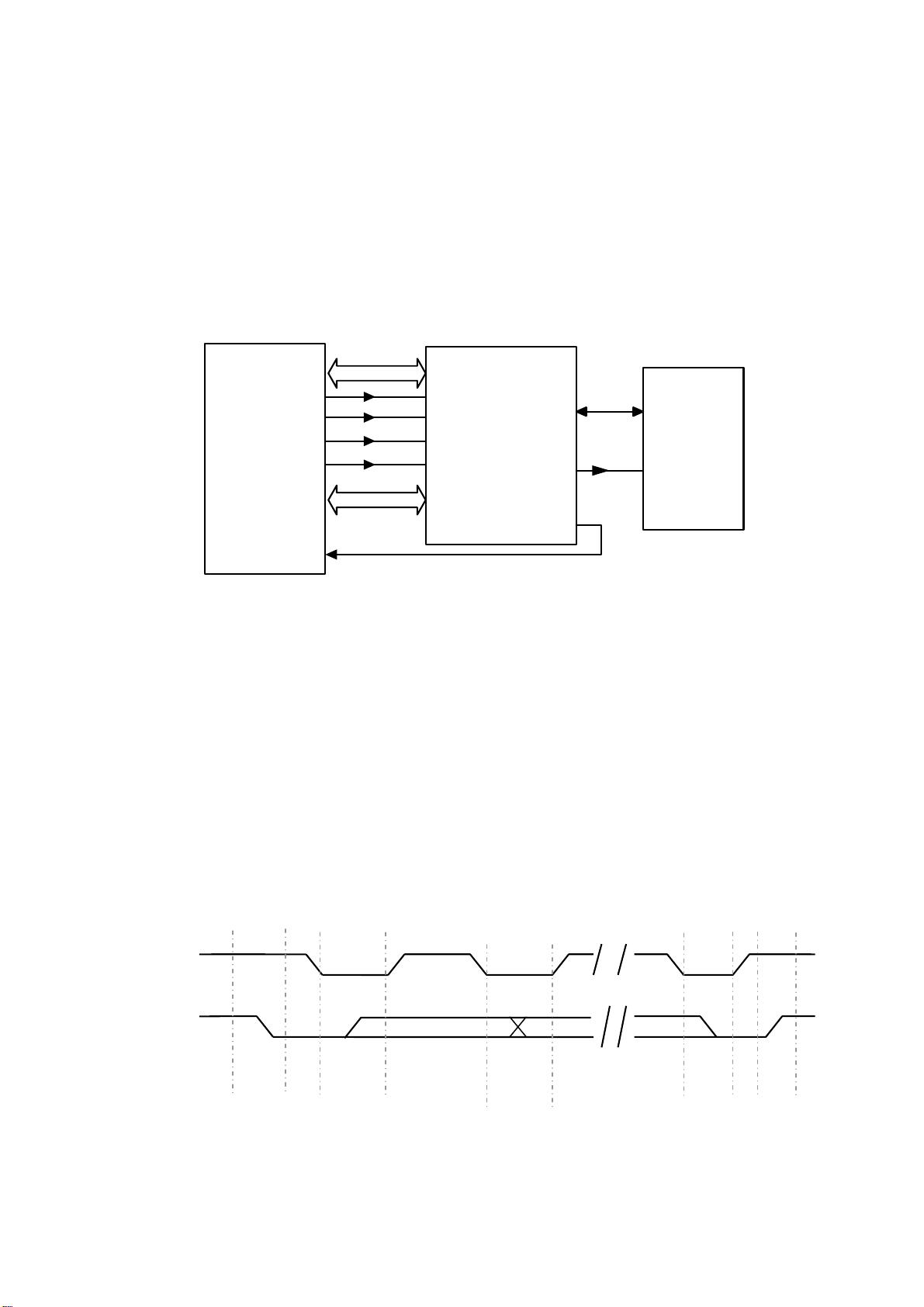

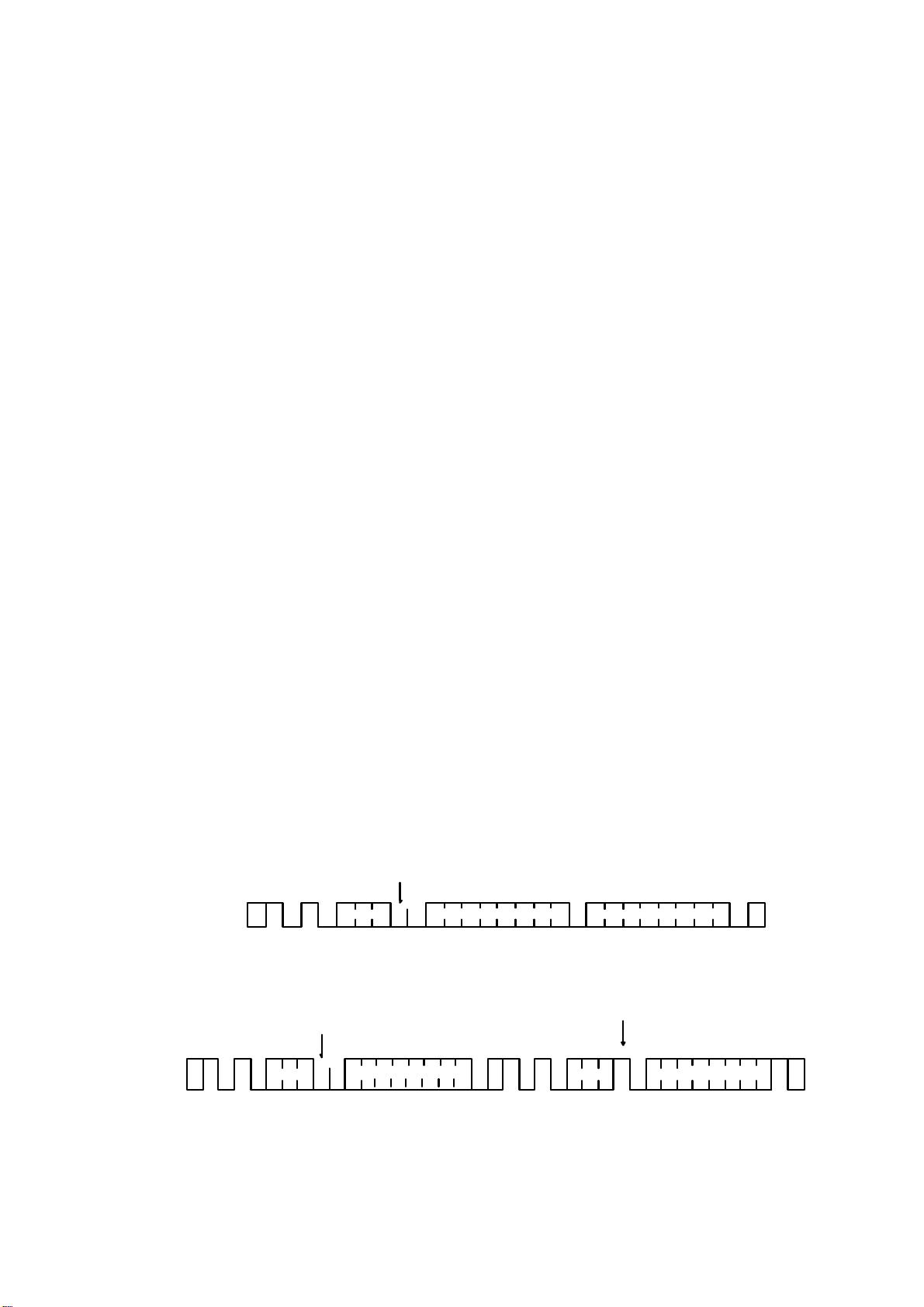

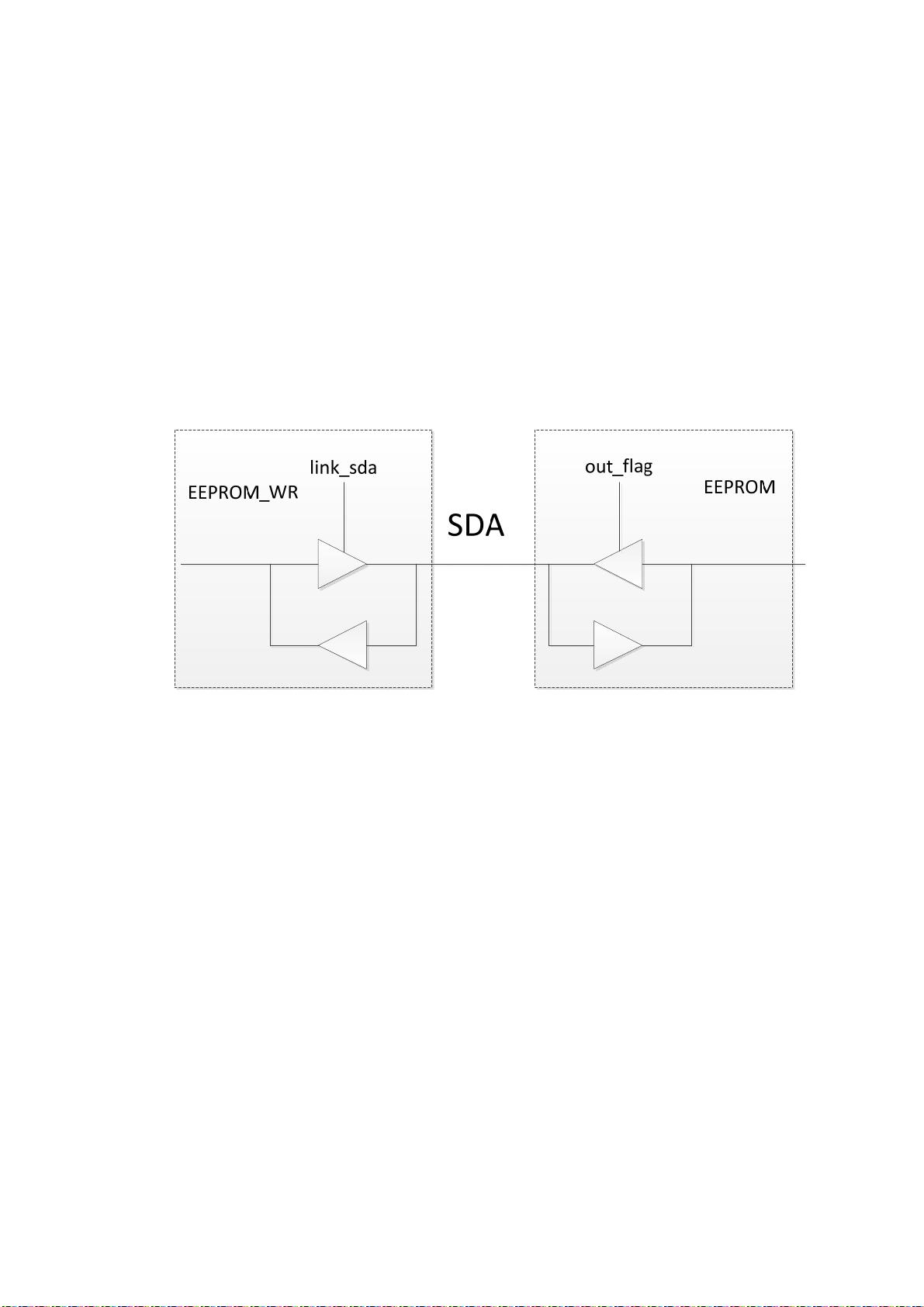

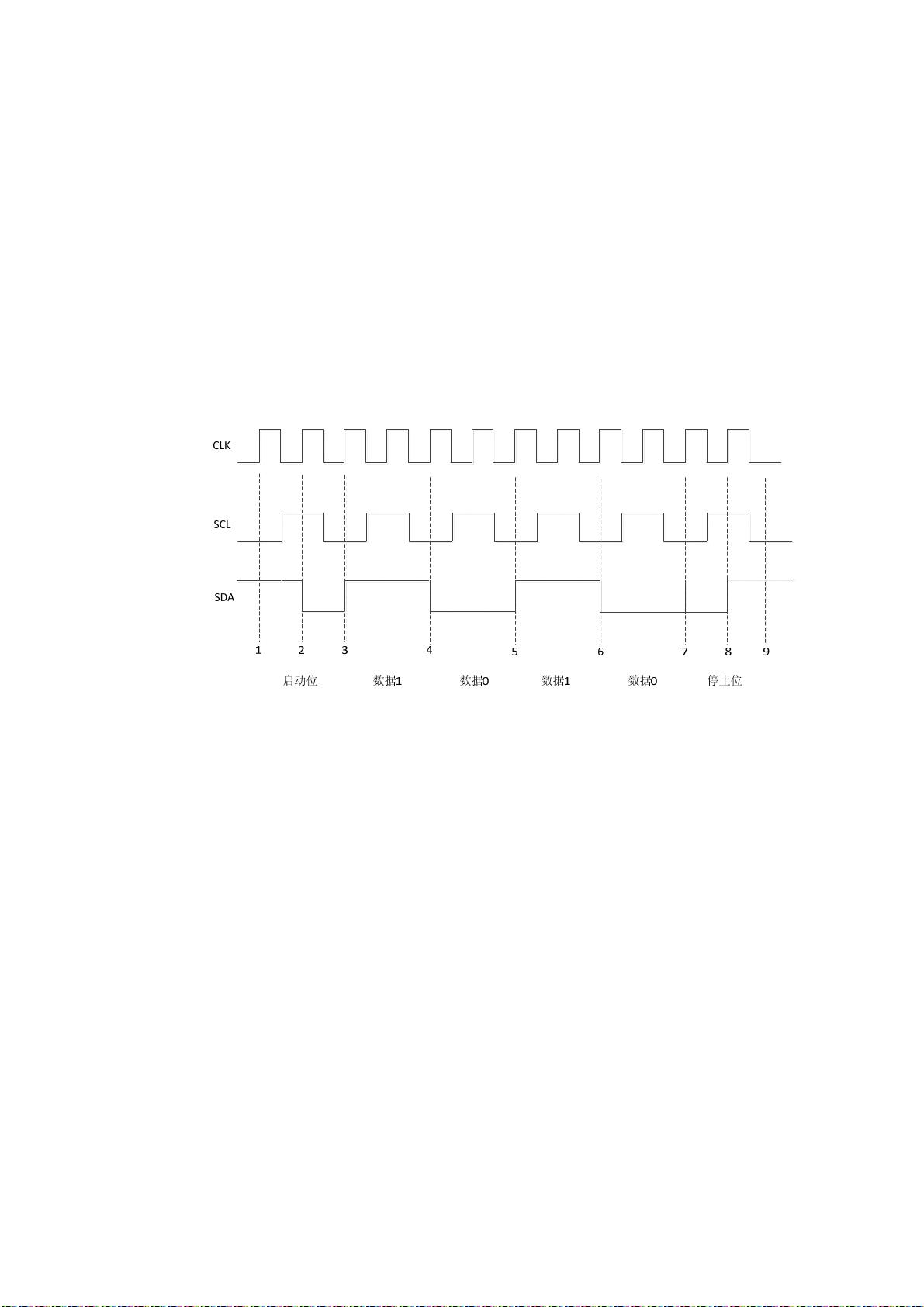

在开始详细介绍I2C通信协议在Verilog中的应用和理解之前,需要了解一些基础概念,比如常见的串行总线UART、SPI和I2C的基本特性和区别。UART(通用异步收发传输器)是两线制(TX和RX)通信总线,它传输数据是基于固定的波特率的,即发送和接收双方的时钟必须保持同步。SPI(串行外设接口)则是一种同步通信总线,具有四条线,包括SCLK(时钟线)、MISO(主输入从输出数据线)、MOSI(主输出从输入数据线)和SS(从设备使能线),它支持全双工通信。而I2C(Inter-Integrated Circuit)总线是一种双线制通信总线,包含SCL(时钟线)和SDA(数据线),这两条线均支持双向通信且需要上拉电阻。 I2C总线是以上三种串行总线中相对复杂的协议,它支持多主多从设备的通信,具有七位地址模式和十位地址模式。I2C的一个重要特性是它在数据传输期间,时钟信号为高电平时,数据线必须保持稳定,否则会被识别为启动或停止信号。这种通信协议被广泛应用于板内芯片之间的通信,而且通常因为没有上拉电阻,抗干扰能力相对较弱,不适合长距离通信。 I2C协议在FPGA设计中主要通过Verilog语言实现,第一步就是分析源代码,理解I2C协议的工作原理。在FPGA设计中,I2C协议的实现通常包括三个主要模块:主机模块(Master)、从机模块(Slave)和EEPROM模块。在上述学习心得中,EEPROM模块是指一种可以电擦除和重写的只读存储器,掉电后数据不会丢失,非常适合用于需要多次读写的场合。 在I2C通信协议的设计实例中,可以分成几个主要部分:信号模块(signal module)、EEPROM写入模块(EEPROM_WR module)和EEPROM模块。信号模块和EEPROM模块多用于仿真,而EEPROM_WR模块则需要综合到实际电路中。在编写这些模块时,为了使代码能够综合,EEPROM_WR模块必须遵循特定的编程规范,例如避免使用非综合代码(如initial和延时#语句)。这样可以确保代码在FPGA上能够被正确实现。 了解了I2C总线的基本特征后,接下来是掌握I2C协议的时序,这对于I2C通信的成功至关重要。I2C协议需要严格按照标准的时序规范发送启动信号、地址信号、读写控制信号、数据信号以及停止信号。在时钟信号SCL为高电平时,数据信号SDA必须保持稳定,这和UART、SPI的某些工作方式类似,但I2C更注重在时钟高电平时数据线的稳定状态。 在上述学习心得中,还提到了EEPROM WR模块如何实现数据的写入和读取。数据的写入过程是通过主模块将数据传送到EEPROM器件上,而读取过程则是从EEPROM中获取数据,并与写入时的数据进行比对,以验证数据的正确性。在至芯科技的EP2C8-2010开发板上,已经预置了EEPROM器件,而RAM IP核则用来模拟信号模块的功能。 总结以上内容,I2C-verilog的学习心得需要围绕I2C协议的特性、模块功能分析、时序要求、以及FPGA设计中特定的编程规范等多个方面展开。学习者在掌握这些知识点后,需要在实际的设计和调试过程中不断实践和验证,以达到熟练运用I2C协议和Verilog语言进行复杂电路设计的目标。

剩余81页未读,继续阅读

阿彬的骑行日记6402018-08-15对于初学者来说,真的很合适

阿彬的骑行日记6402018-08-15对于初学者来说,真的很合适 黄小鹿2020-04-21质量不错!

黄小鹿2020-04-21质量不错!

- 粉丝: 2

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Keil C51 插件 检测所有if语句

- 各种排序算法java实现的源代码.zip

- 金山PDF教育版编辑器

- 基于springboot+element的校园服务平台源代码项目包含全套技术资料.zip

- 自动化应用驱动的容器弹性管理平台解决方案

- 各种排序算法 Python 实现的源代码

- BlurAdmin 是一款使用 AngularJs + Bootstrap实现的单页管理端模版,视觉冲击极强的管理后台,各种动画效果

- 基于JSP+Servlet的网上书店系统源代码项目包含全套技术资料.zip

- GGJGJGJGGDGGDGG

- 基于SpringBoot的毕业设计选题系统源代码项目包含全套技术资料.zip

信息提交成功

信息提交成功