没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

A40i User Manual

Revision 1.1

Jun. 15, 2018

Copyright © 2018 Allwinner Technology Co., Ltd. All Rights Reserved.

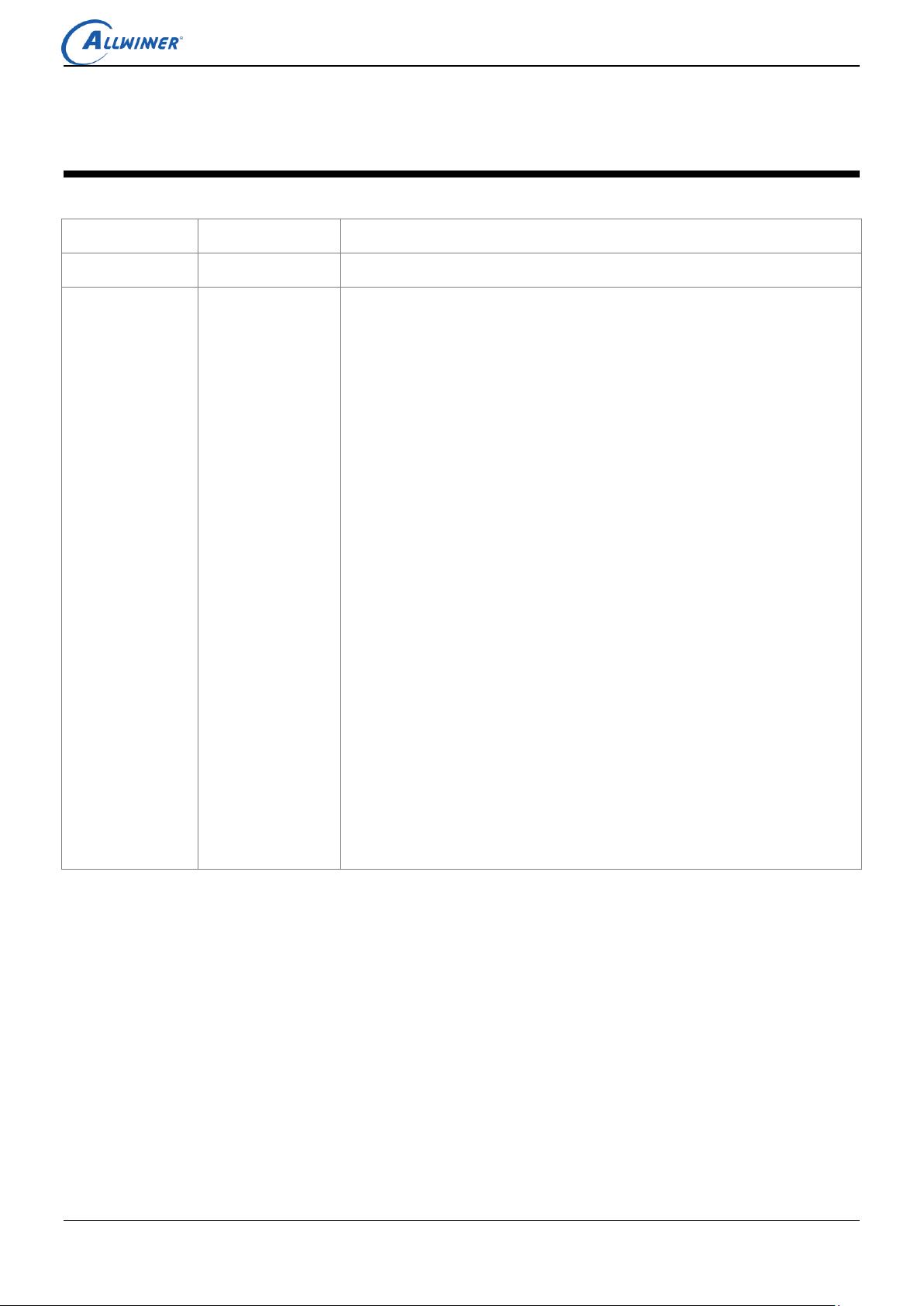

Revision History

A40i User Manual(Revision 1.1) Copyright© 2018 Allwinner Technology Co.,Ltd. All Rights Reserved. Page 3

Revision History

Revision Date Description

1.0 May.22,2018 Initial release version

1.1 Jun.15,2018

Chapter 3 System

1. Add notes about clock tree in Section 3.3.2.1.

2. Add guide about spread spectrum function in Section 3.3.2.7.

3. Add operations and functional descriptions, programming guidelines for

Timer module in Section 3.7.

4. Add operations and functional descriptions, programming guidelines for

High Speed Timer module in Section 3.8.

5. Add operations and functional descriptions, programming guidelines for

RTC module in Section 3.11.

6. Add programming guidelines for KEYADC module in Section 3.13.

7. Add programming guidelines for Thermal Sensor module in Section 3.15.

8. Add block diagram, operations and functional descriptions for RTC

module in Section 3.18.

Chapter 4 Memory

1. Add programming guidelines about NDFC in Section 4.2.4.

2. Add programming guidelines about SMHC in Section 4.3.4.

Chapter 7 Display

1. Add BT656 using guides in Section 7.2.4.

Chapter 8 Interfaces

1. Add SPI data transfer/receive process in CPU and DMA mode in Section

8.2.4.2.

2. Add programming guidelines about I2S/PCM in Section 8.8.4.

Contents

A40i User Manual(Revision 1.1) Copyright© 2018 Allwinner Technology Co.,Ltd. All Rights Reserved. Page 4

Contents

Declaration ............................................................................................................................................................................ 2

Revision History..................................................................................................................................................................... 3

Contents ................................................................................................................................................................................ 4

Figures ................................................................................................................................................................................. 32

Tables .................................................................................................................................................................................. 35

Chapter 1. About This Documentation ............................................................................................................................... 37

1.1. Purpose ................................................................................................................................................................ 37

1.2. Intended Audience ............................................................................................................................................... 37

1.3. Symbol Conventions ............................................................................................................................................. 37

1.4. Notes .................................................................................................................................................................... 37

1.4.1. Register Attributes .................................................................................................................................... 37

1.4.2. Reset Value Conventions ........................................................................................................................... 38

1.4.3. Numerical System...................................................................................................................................... 38

1.5. Acronyms and Abbreviations ............................................................................................................................... 38

Chapter 2. Overview............................................................................................................................................................ 41

2.1. Processor Overview ............................................................................................................................................. 42

2.2. Features ............................................................................................................................................................... 43

2.2.1. CPU Architecture ....................................................................................................................................... 43

2.2.2. GPU Architecture....................................................................................................................................... 43

2.2.3. Memory ..................................................................................................................................................... 43

2.2.3.1. Boot ROM ....................................................................................................................................... 43

2.2.3.2. SDRAM ........................................................................................................................................... 43

2.2.3.3. NAND Flash..................................................................................................................................... 43

2.2.3.4. SMHC .............................................................................................................................................. 44

2.2.4. System Peripherals .................................................................................................................................... 44

2.2.4.1. Timer .............................................................................................................................................. 44

2.2.4.2. High Speed Timer ........................................................................................................................... 44

2.2.4.3. GIC .................................................................................................................................................. 44

2.2.4.4. DMA ............................................................................................................................................... 44

2.2.4.5. CCU ................................................................................................................................................. 44

2.2.4.6. RTC ................................................................................................................................................. 45

2.2.4.7. PWM ............................................................................................................................................... 45

2.2.4.8. Thermal Sensor .............................................................................................................................. 45

2.2.4.9. Crypto Engine ................................................................................................................................. 45

2.2.4.10. Security ID .................................................................................................................................... 45

2.2.5. Video Engine ............................................................................................................................................. 45

2.2.5.1. Video Decoder ................................................................................................................................ 45

2.2.5.2. Video Encoder ................................................................................................................................ 46

2.2.6. Display Subsystem ..................................................................................................................................... 46

2.2.6.1. DE2.0 .............................................................................................................................................. 46

2.2.6.2. Video Output .................................................................................................................................. 46

2.2.7. Image Subsystem....................................................................................................................................... 46

2.2.8. Analog Subsystem ..................................................................................................................................... 47

2.2.8.1. Analog Codec ................................................................................................................................. 47

2.2.8.2. I2S/PCM .......................................................................................................................................... 47

2.2.8.3. OWA ............................................................................................................................................... 47

2.2.8.4. AC97 ............................................................................................................................................... 48

2.2.9. External Peripherals .................................................................................................................................. 48

2.2.9.1. USB ................................................................................................................................................. 48

2.2.9.2. EMAC .............................................................................................................................................. 48

2.2.9.3. GMAC ............................................................................................................................................. 48

Contents

A40i User Manual(Revision 1.1) Copyright© 2018 Allwinner Technology Co.,Ltd. All Rights Reserved. Page 5

2.2.9.4. Transport Stream Controller .......................................................................................................... 48

2.2.9.5. TWI ................................................................................................................................................. 48

2.2.9.6. Smart Card Reader ......................................................................................................................... 49

2.2.9.7. SPI ................................................................................................................................................... 49

2.2.9.8. UART ............................................................................................................................................... 49

2.2.9.9. PS2 .................................................................................................................................................. 49

2.2.9.10. CIR ................................................................................................................................................ 49

2.2.9.11. SATA ............................................................................................................................................. 50

2.2.9.12. Keypad .......................................................................................................................................... 50

2.2.9.13. KEYADC ......................................................................................................................................... 50

2.2.9.14. RTP ............................................................................................................................................... 50

2.2.10. Package ................................................................................................................................................... 50

2.3. Block Diagram ...................................................................................................................................................... 51

Chapter 3. System ............................................................................................................................................................... 53

3.1. Memory Mapping ................................................................................................................................................ 54

3.2. CPU Configuration ................................................................................................................................................ 57

3.2.1. Overview ................................................................................................................................................... 57

3.2.2. Register List ............................................................................................................................................... 57

3.2.3. Register Description .................................................................................................................................. 58

3.2.3.1. CPU0 Reset Control(Default Value: 0x0000_0003) ........................................................................ 58

3.2.3.2. CPU0 Control Register(Default Value: 0x0000_0000) .................................................................... 58

3.2.3.3. CPU0 Status Register(Default Value: 0x0000_0000) ...................................................................... 58

3.2.3.4. CPU1 Reset Control(Default Value: 0x0000_0001) ........................................................................ 59

3.2.3.5. CPU1 Control Register(Default Value: 0x0000_0000) .................................................................... 59

3.2.3.6. CPU1 Status Register(Default Value: 0x0000_0000) ...................................................................... 60

3.2.3.7. CPU2 Reset Control(Default Value: 0x0000_0001) ........................................................................ 60

3.2.3.8. CPU2 Control Register(Default Value: 0x0000_0000) .................................................................... 60

3.2.3.9. CPU2 Status Register(Default Value: 0x0000_0000) ...................................................................... 61

3.2.3.10. CPU3 Reset Control(Default Value: 0x0000_0001) ...................................................................... 61

3.2.3.11. CPU3 Control Register(Default Value: 0x0000_0000) .................................................................. 61

3.2.3.12. CPU3 Status Register(Default Value: 0x0000_0000) .................................................................... 62

3.2.3.13. CPUX Power Off Gating Register(Default Value: 0x0000_0000) ................................................... 62

3.2.3.14. CPU0 Power Switch Control Register(Default Value: 0x0000_0000) ............................................ 62

3.2.3.15. CPU1 Power Switch Control Register(Default Value: 0x0000_0000) ............................................ 62

3.2.3.16. CPUIDLE Enable Control Register(Default Value: 0x0000_0000) ................................................. 63

3.2.3.17. Close Core Flag Register(Default Value: 0x0000_0000) ............................................................... 63

3.2.3.18. IRQ_FIQ Status and Control Register(Default Value: 0x0000_0000) ............................................ 63

3.2.3.19. Power Switch Delay Register(Default Value: 0x0000_000A) ........................................................ 64

3.2.3.20. Configuration Delay Register(Default Value: 0x0000_0001) ........................................................ 64

3.2.3.21. Power Down Configuration Register(Default Value: 0x0000_00FF) ............................................. 64

3.2.3.22. Power Up Configuration Register0(Default Value: 0x0000_00FE)................................................ 64

3.2.3.23. Power Up Configuration Register1(Default Value: 0x0000_00FC) ............................................... 64

3.2.3.24. Power Up Configuration Register2(Default Value: 0x0000_00F8) ............................................... 65

3.2.3.25. Power Up Configuration Register3(Default Value: 0x0000_00F0) ............................................... 65

3.2.3.26. Power Up Configuration Register4(Default Value: 0x0000_00C0) ............................................... 65

3.2.3.27. Power Up Configuration Register5(Default Value: 0x0000_0000) ............................................... 65

3.2.3.28. General Control Register(Default Value: 0x1000_0020) .............................................................. 65

3.2.3.29. Event Input Register(Default Value: 0x0000_0000) ..................................................................... 66

3.2.3.30. 64-bit Counter Control Register(Default Value: 0x0000_0000) ................................................... 66

3.2.3.31. 64-bit Counter Low Register(Default Value: 0x0000_0000) ......................................................... 67

3.2.3.32. 64-bit Counter High Register(Default Value: 0x0000_0000) ........................................................ 67

3.3. CCU ....................................................................................................................................................................... 68

3.3.1. Overview ................................................................................................................................................... 68

3.3.2. Operations and Functional Descriptions ................................................................................................... 69

3.3.2.1. Block Diagram ................................................................................................................................ 69

3.3.2.2. Typical Applications........................................................................................................................ 73

Contents

A40i User Manual(Revision 1.1) Copyright© 2018 Allwinner Technology Co.,Ltd. All Rights Reserved. Page 6

3.3.2.3. PLL .................................................................................................................................................. 73

3.3.2.4. Bus .................................................................................................................................................. 74

3.3.2.5. Clock Switch ................................................................................................................................... 74

3.3.2.6. Reset and Gating ............................................................................................................................ 74

3.3.2.7. Spread Spectrum Function ............................................................................................................. 74

3.3.3. Register List ............................................................................................................................................... 74

3.3.4. Register Description .................................................................................................................................. 77

3.3.4.1. PLL_CPUX Control Register (Default Value: 0x0000_1000) ............................................................ 77

3.3.4.2. PLL_AUDIO Control Register (Default Value: 0x000_35514) .......................................................... 78

3.3.4.3. PLL_VIDEO0 Control Register (Default Value: 0x0300_6207) ......................................................... 79

3.3.4.4. PLL_VE Control Register (Default Value: 0x0300_6207) ................................................................. 80

3.3.4.5. PLL_DDR0 Control Register (Default Value: 0x0000_1000) ............................................................ 81

3.3.4.6. PLL_PERIPH0 Control Register (Default Value: 0x0004_1811) ....................................................... 81

3.3.4.7. PLL_PERIPH1 Control Register (Default Value: 0x0004_1811) ....................................................... 83

3.3.4.8. PLL_VIDEO1 Control Register (Default Value: 0x0300_6207) ......................................................... 84

3.3.4.9. PLL_SATA Control Register (Default Value: 0x0000_1811) ............................................................. 85

3.3.4.10. PLL_GPU Control Register (Default Value: 0x0300_6207) ............................................................ 86

3.3.4.11. PLL_MIPI Control Register (Default Value: 0x0000_0515) ........................................................... 87

3.3.4.12. PLL_DE Control Register (Default Value: 0x0300_6207) .............................................................. 88

3.3.4.13. PLL_DDR1 Control Register (Default Value: 0x0000_1800) .......................................................... 89

3.3.4.14. CPUX/AXI Configuration Register (Default Value: 0x0001_0300) ................................................ 90

3.3.4.15. AHB1/APB1 Configuration Register (Default Value: 0x0000_1010) .............................................. 90

3.3.4.16. APB2 Configuration Register (Default Value: 0x0100_0000) ....................................................... 91

3.3.4.17. Bus Clock Gating Register 0 (Default Value: 0x0000_0000) ......................................................... 91

3.3.4.18. Bus Clock Gating Register 1 (Default Value: 0x0000_0000) ......................................................... 94

3.3.4.19. Bus Clock Gating Register 2 (Default Value: 0x0000_0000) ......................................................... 96

3.3.4.20. Bus Clock Gating Register 3 (Default Value: 0x0000_0000) ......................................................... 97

3.3.4.21. Bus Clock Gating Register 4 (Default Value: 0x0000_0000) ......................................................... 99

3.3.4.22. THS Clock Register (Default Value: 0x0000_0000) ....................................................................... 99

3.3.4.23. NAND Clock Register (Default Value: 0x0000_0000) ................................................................. 100

3.3.4.24. SMHC0 Clock Register (Default Value: 0x0000_0000)................................................................ 100

3.3.4.25. SMHC1 Clock Register (Default Value: 0x0000_0000) ................................................................ 101

3.3.4.26. SMHC2 Clock Register (Default Value: 0x0000_0000) ................................................................ 101

3.3.4.27. SMHC3 Clock Register (Default Value: 0x0000_0000) ................................................................ 102

3.3.4.28. TS Clock Register (Default Value: 0x0000_0000) ........................................................................ 103

3.3.4.29. CE Clock Register (Default Value: 0x0000_0000) ....................................................................... 103

3.3.4.30. SPI0 Clock Register (Default Value: 0x0000_0000) .................................................................... 104

3.3.4.31. SPI1 Clock Register (Default Value: 0x0000_0000) .................................................................... 104

3.3.4.32. SPI2 Clock Register (Default Value: 0x0000_0000) .................................................................... 105

3.3.4.33. SPI3 Clock Register (Default Value: 0x0000_0000) .................................................................... 106

3.3.4.34. I2S/PCM0 Clock Register (Default Value: 0x0000_0000) ........................................................... 106

3.3.4.35. I2S/PCM1 Clock Register (Default Value: 0x0000_0000) ........................................................... 107

3.3.4.36. I2S/PCM2 Clock Register (Default Value: 0x0000_0000) ........................................................... 107

3.3.4.37. AC97 Clock Register(Default Value: 0x0003_0000) .................................................................... 107

3.3.4.38. OWA Clock Register (Default Value: 0x0001_0000) ................................................................... 108

3.3.4.39. KEYPAD Clock Register (Default Value: 0x0000_001F) ............................................................... 108

3.3.4.40. SATA Clock Register (Default Value: 0x0000_0000) .................................................................... 109

3.3.4.41. USBPHY Configuration Register (Default Value: 0x0000_0000) ................................................. 109

3.3.4.42. CIR0 Clock Register (Default Value: 0x0000_0000) .................................................................... 110

3.3.4.43. CIR1 Clock Register (Default Value: 0x0000_0000) .................................................................... 111

3.3.4.44. PLL_DDR Auxiliary Register (Default Value: 0x0000_0001)........................................................ 112

3.3.4.45. DRAM Configuration Register (Default Value: 0x0000_0000) .................................................... 112

3.3.4.46. PLL_DDR1 Configuration Register (Default Value: 0x0CCC_A000) ............................................. 112

3.3.4.47. MBUS Reset Register (Default Value: 0x8000_0000) ................................................................. 113

3.3.4.48. DRAM Clock Gating Register (Default Value: 0x0000_0000) ...................................................... 113

3.3.4.49. DE Clock Register (Default Value: 0x0000_0000) ....................................................................... 114

剩余785页未读,继续阅读

资源评论

dslove615

- 粉丝: 3

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功