没有合适的资源?快使用搜索试试~ 我知道了~

看到有朋友分享了合众达的6000实验箱的原理图,搜索了一下,似乎没有瑞泰DM642的,也不知道有没有朋友需要,传上来,供大家参考参考. 朋友 , 瑞泰 , 实验箱 ICETEK-DM642-PCI 原理图 v1.pdf ICETEK-DM642-PCI 原理图 v1

资源推荐

资源详情

资源评论

1

1

2

2

3

3

4

4

5

5

A A

B B

C C

D D

4. ALL 0.1 uF AND 0.01uF CAPACITORS ARE DECOUPLING CAPS UNLESS

OTHERWISE NOTED. THEY ARE SHOWN ON THE PAGE WITH THE INTEGRATED

CIRCUITS THEY SHOULD BE PLACED NEAR.

NOTES, UNLESS OTHERWISE SPECIFIED:

1. RESISTANCE VALUES IN OHMS.

2. CAPACTITANCE VALUES IN MICROFARADS.

3. REFERENCE DESIGNATORS USED:

5. OBSERVE THE FOLLOWING LAYOUT NOTES:

1. TOP - SIGNAL ROUTING

2. GROUND PLANE

3. INNER1 - SIGNAL ROUTING

4. VCC3 PLANE (3.3V BOARD)

5. INNER2 - SIGNAL ROUTING

6. INNER3 - SIGNAL ROUTING

7. VCC PLANE 2

8. INNER4 - SIGNAL ROUTING

9. GROUND PLANE

10. BOTTOM - SIGNAL ROUTING

6. BOARD PROPERTIES

B. 50 +/- 5 OHM MATCHED IMPEDANCE

C. OUTER LAYERS 0.5 OZ CU /W 0.5 OZ AU PLATING

D. INNER LAYERS 1.0 OZ CU

E. FR4 BOARD MATERIAL

F. MINIMUM TRACE WIDTH/SPACING 4 MILS

G. MINIMUM VIA SIZE 10/19 MIL

H. LAYER STACKUP:

A. ROUTE TO WITHIN 10% OF MANHATTAN DISTANCE

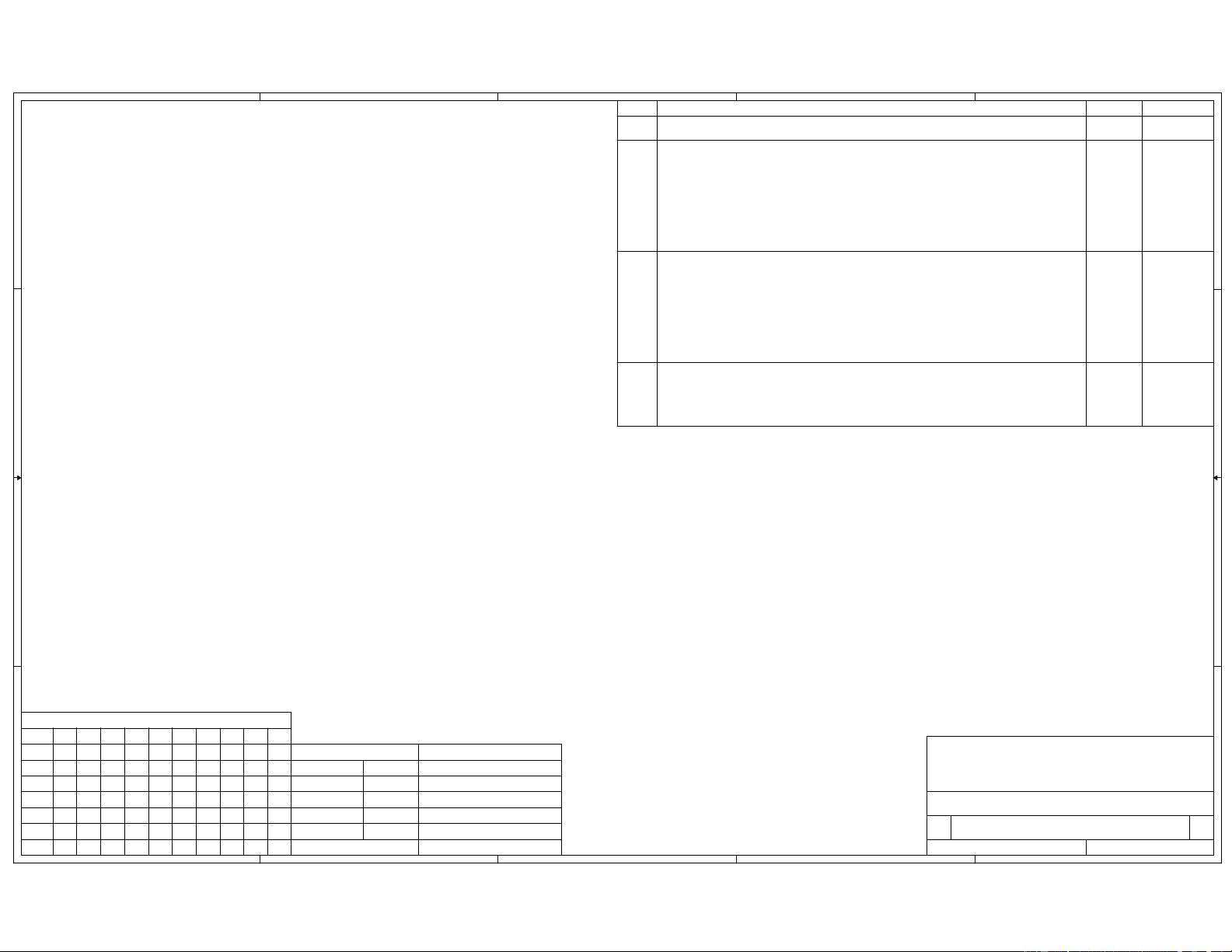

SCHEMATIC INDEX

1 DM642 EVM Notes and Contents

2 User Options/Config

3 DM642 Clocks, Reset, Interrupts, Timers, and IIC

4 DM642 EMIF

5 Emulation Headers

6 DM642 Video Ports

7 DM642 PCI/HPI/EMAC

8 DM642 Power Pins

9 SDRAM

10 Expansion EMIF Buffers

11 Flash and Dual UART

12 RS232 Buffers

13 Video Port Expansion Switches

14 Video Port Daugher Card Connector

15 EMIF Daughter Card Connector

16 OSD FPGA

17 OSD FPGA Power

18 Video Decoder 1

19 Video Decoder 2

20 Video Encoder

21 Ethernet

22 PCI

23 AIC23 Audio Interface

24 Power

25 FPGA Power/Reset Circuitry

REV

ENGR

2

REVISION STATUS OF SHEETS

1

11

SH

DATE

1412 13

DATE

ENGR-MGR

MFG

7

DWN

DATE

8

DATE

10

SH

DATE

CHK

RLSE

APPLICATION

REV

35

NEXT ASSY

DATE

6

DATE

9

QA

USED ON

4

15

DCCAAACBAD

BABAC

R.R.P.

T.W.K.

R.R.P.

R.R.P.

C.M.D.

R.R.P.

R.R.P.

03/30/2003

03/30/2003

16 17 18 19 20

21 22 23 24 25 03/30/2003

03/30/2003

03/30/2003

03/30/2003

03/30/2003

REV

SH

A Initial schematic ready for layout.

DESCRIPTIONREV APPROVEDDATE

01/07/03 RRP

Sheet 2: Changed LENDIAN_MODE signal so R221 is a pull-up and S2 provides

a pull-down.

Sheet 3: Swapped DSP_SCL0 and DSP_SDA0 signals going to U16.

Sheet 7: Added series terminations RN28, R246, R247, & R248.

Sheet 11: Routed DC_A[8:6], UART_CSA#, & UART_CSB# to U15.

Sheet 13: Changed bus routed to U53 to VP0D[9:2] and U52 to VP1D[9:2].

Sheet 15: Added pull-up (R241) to DC_ARDY.

Sheet 17: Pin 177 is Ground not VCC

Sheet 20: Changed U36 & U37 to SN74LVC1G125DCKR.

B 04/01/03 RRP

Sheet 2: Changed EMAC_ENABLE to autodect S2 is now 2 position switch.

Sheet 3: Routed FPGALOCK to pullup R101 to lock FPGA programming

Sheet 7: Implemented EMAC_ENABLE Autodetect on U41-1A, added R249

Sheet 11: Added TCE2# ,TCE3#, SOE3# to U15 Decoder.

Sheet 16: Swapped pins 141 and 149 on FPGA for HDTV speed paths, changed

fpga to -7 part

Sheet 17: Added AND Gate U55 to Lock FPGA programming, changed FPGA to -7

Sheet 20: Swapped Red and Blue on VGA Connector. Removed R102,R129,R183

Sheet 22: Added R250 for HPI option

RRP05/15/03

C

ACAAB

CCDDD

D

Sheet 10: Changed Buffers U2,U3,U4,U5 to non-holder type SN74LVT16245B

Sheet 18: Changed crystal capacitors C168 and C169 from 18pF to 33 pF

Sheet 19: Changed crystal capacitors C288 and C289 from 18pF to 33 pF

Sheet 20: Changed Value on output termination R82,R130,R184 from 75 ohms

to 82 ohms.

08/01/03 RRP

506842

D

DM642 Evaluation Module

B

125

Monday, August 11, 2003

SPECTRUM DIGITAL INCORPORATED

Title

Size Document Number Rev

Date: Sheet

of

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

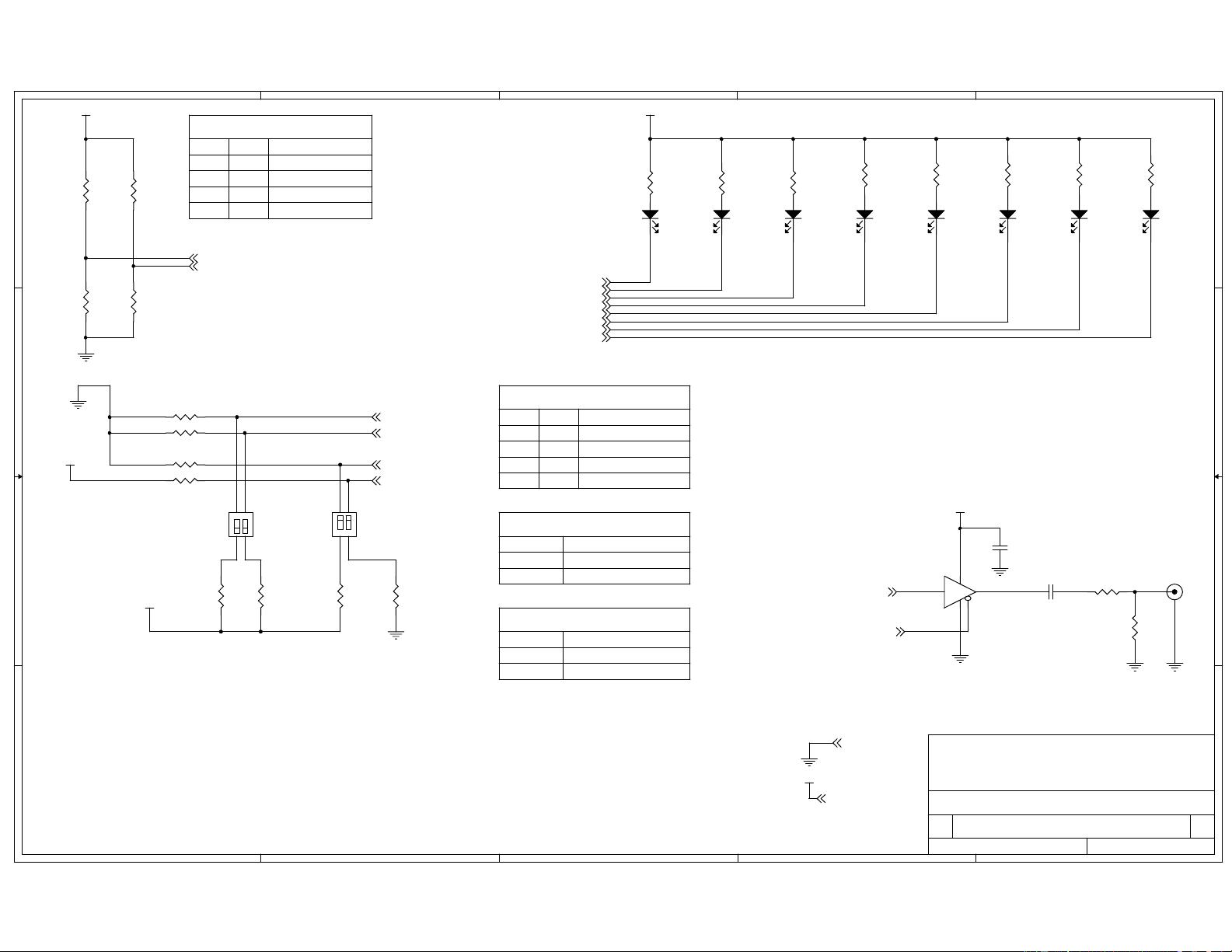

USER LEDS

LEDS/SWITCHES/CONFIGURATION INPUTS

SPDIF BLOCK

ON ON

EMIF_ECLKINSEL[1:0]

NO POP

1K OHM

ECLKIN( DEFAULT)

CPU CLOCK /4 EMIF CLOCK

MODE SELECTEDR42 R40

NO POP

1K OHM1K OHM

1K OHMNO POP

NO POP CPU CLOCK /6 EMIF CLOCK

ECLKIN

OFF NO BOOT (DEFAULT)

BOOT_MODE[1:0]

MODE SELECTED

HPI/PCI BOOT MODE

S1-2 S1-1

OFF

OFF ON

RESERVED

EMIF 8 BIT ROM BOOT

ON

ON ON

OFF

LITTLE ENDIAN MODE (DEFAULT)

BIG ENDIAN MODE

S2-2(ENDIAN)

OFF

ON

ENDIAN MODE CONFIGURATION

MODE SELECTED

S2-1(PCI ROM)

OFF

ON

PCI MODE CONFIGURATION

MODE SELECTED

PCI EEPROM DISABLED(DEFAULT)

PCI ROM ENABLED

506842

C

DM642 EVALUATION MODULE

SPECTRUM DIGITAL. INCORPORATED

B

225

Monday, August 11, 2003

Title

Size Document Number Rev

Date: Sheet

of

GND

USER_LED0(16)

USER_LED1(16)

USER_LED2(16)

USER_LED3(16)

USER_LED4(16)

USER_LED5(16)

USER_LED6(16)

USER_LED7(16)

BOOT_MODE1 (4,10)

BOOT_MODE0 (4,10)

LENDIAN_MODE (3,14)

PCI_EEAI (3,14)

EMIF_ECLKINSEL0 (4,10)

EMIF_ECLKINSEL1 (4,10)

SPDIF_OUT(6)

EXP_AUDIO_EN#(6,14)

VCC3.3

GND

VCC3.3VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

R114 NO POP

R44

NO POP

R41

NO POP

R40

NO POP

R42

NO POP

R22

150

C237 0.1uF

C238

0.1uF

J9 RCA JACK

1

2

R190 220

R191

100

DS5

GREEN

DS6

GREEN

R17

150

R18

150

DS7

GREEN

R15

150

R223 NO POP

R16

150

DS8

GREEN

R220

1K

1

2

S2

DIP_SWITCH

101184-0002

1

2

4

3

1

2

S1

DIP_SWITCH

101184-0002

1

2

4

3

R221 NO POP

R219

1K

R115 NO POP

R89

1K

R90

1K

R21

150

R20

150

DS1

GREEN

DS2

GREEN

DS3

GREEN

R19

150

DS4

GREEN

U34

SN74LVC1G125

3

4

5

2

1

1

1

2

2

3

3

4

4

5

5

A A

B B

C C

D D

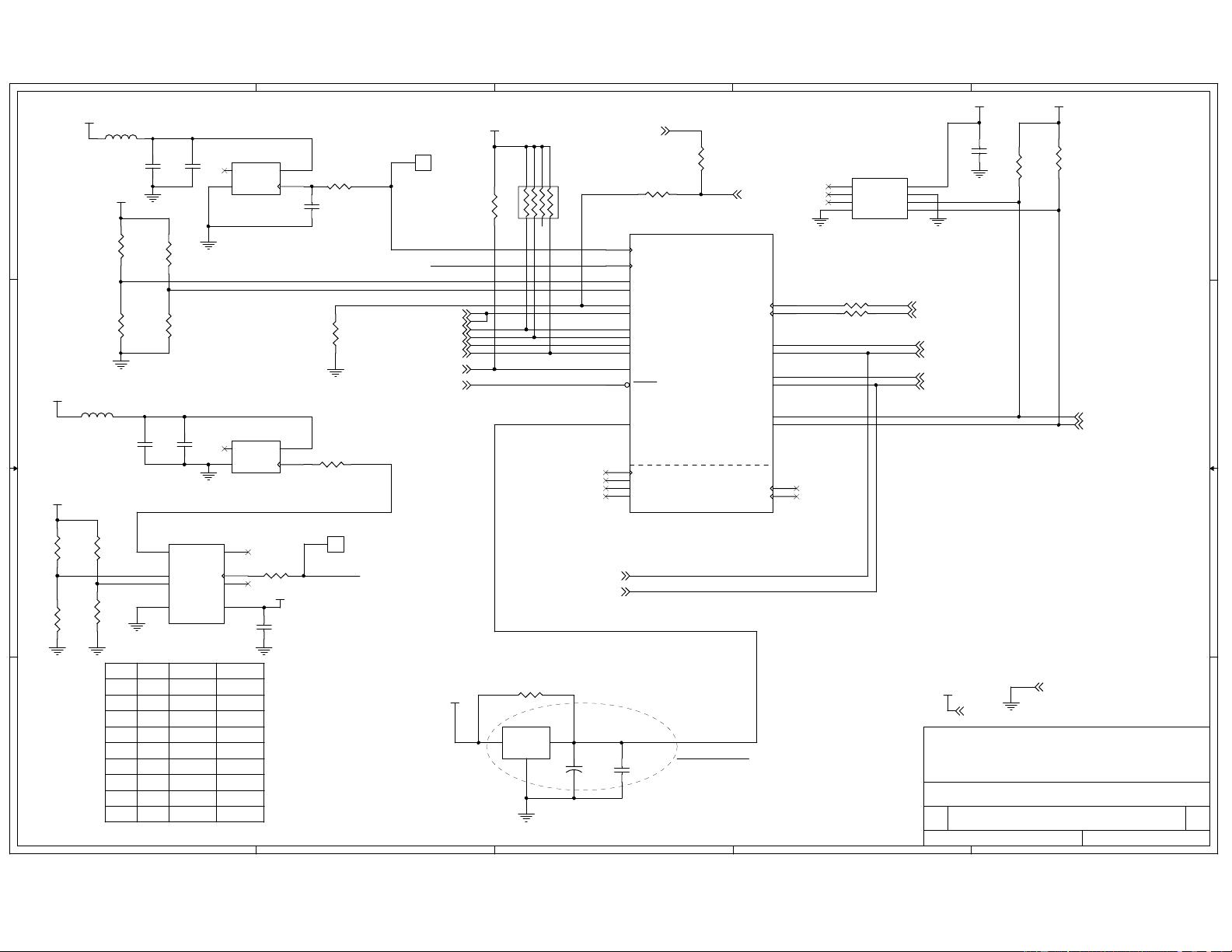

DM642 CLOCKS,RESET

CIRCUITRY,I2C

INTERFACE

3X

5.33X

8X

2.5X

3.33X

6X

2X

4X

5X

S1 S0

00

0

0

0

0

1

1

1

1

1

OPEN

OPEN

OPEN OPEN

OPEN

OPEN

1

100 MHz

125 MHz

133.25 MHz

62.5 MHz

50 MHz

83.25 MHz

150 MHz

75 MHz

200 MHz

MULTIPLY

Place all PLL external components as close

to the DSP. All PLL external components

must be on a single side of the board.

I2C ROM

THIS DESELECTS 641 OPTION,

0 AT POWER ON RESET

OUTPUT

506842

C

DM642 EVALUATION MODULE

SPECTRUM DIGITAL INCORPORATED

B

325

Monday, August 11, 2003

Title

Size Document Number Rev

Date: Sheet

of

DSP_ECLKIN

DSP_CLKIN

DSP_ECLKIN

DSP_PLL_VDD

DSP_PLL_VDD

GND

PCI_EEAI(2,14)

DSP_EXTINT4(14)

DSP_GPIO_3(2,14)

EMAC_ENABLE(7,14)

DSP_EXTINT5(14)

LENDIAN_MODE(2,14)

DSP_NMI(14)

DSP_EXTINT7(16)

SYSTEM_RESET#(11,14,16,17,18,19,20,21,25)

FPGA_PROG# (17)

DSP_SCL0 (14,18,19,20,23)

DSP_SDA0 (14,18,19,20,23)

DSP_TOUT1 (2,14)

DSP_TINP1 (14)

FPGA_CCLK (17)

DSP_TINP0 (14)

FPGA_DIN (16)

DSP_TOUT0 (7,14)

FPGA_INIT_EINT6(16)

VCC3.3

GND

FPGA_LOCK(17)

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3 VCC3.3

VCC3.3

VCC3.3

VCC3.3

C39

0.1uF

+

C40

10uF

E1

EXCCET103U

EMI FILTER

1 3

2

IO

GND

TP21

TP

1

TP20

TP

1

R66

2K

R67

2K

R174

NO POP

R205

NO POP

R203

10K

R173 360

R217

10K

R171

NO POP

C119

0.1uF

RN27

RPACK4-10K

1

2

3

4 5

6

7

8

R101

2K

C190

0.1uF

R172

1K

C188

0.1uF

R120

33

C186

.001uF

C189

NO POP

L16

BLM21P221SN

R122

10K

R119

NO POP

R123

NO POP

R121

NO POP

U26

50.00 MHz

4

32

1

VCC

OUTGND

EN

U21

25 MHz

4

32

1

VCC

OUTGND

EN

C184

.001uF

L17

BLM21P221SN

C187

0.1uF

R118

33

R5 NO POP

Clocks / Interrupts /

Timers / IIC

RESERVED

U25E

DM642

AC2

AB3

AA2

AE4

AD3

AC4

D6

C6

F4

F3

F2

E1

M5

L5

B4

P4

AA3

AF3

V6

E14

A4

C5

A5

B5

E4

D3

H25

CLKIN

CLKINF

CLKMODE0

CLKMODE1

CLKOUTT

CLKOUTF

GP01 / CLKOUT4

GP02 / CLKOUT6

EXTINT4 / GP04

EXTINT5 / GP05

EXTINT6 / GP06

EXTINT7 / GP07

GP00 / DM641SEL

GP03 / PCIEEAI

NMI

RESET

AMUX1

PLL_LD

PLL_VDD

TSTSTRB

TINP0

EMACEN / TOUT0

TINP1

LENDIAN / TOUT1

SCL0

SDA0

ECLKIN

R91 33

U16

24WC256

1 8

4

3 6

5

2 7

A0 VCC

VSS

NC SCL

SDA

A1 WP

U20 ICS512

2

8

46

7 5

1

3

VDD

X2

REFS0

S1 CLK

X1/ICLK

GND

R218 360

R176 360

1

1

2

2

3

3

4

4

5

5

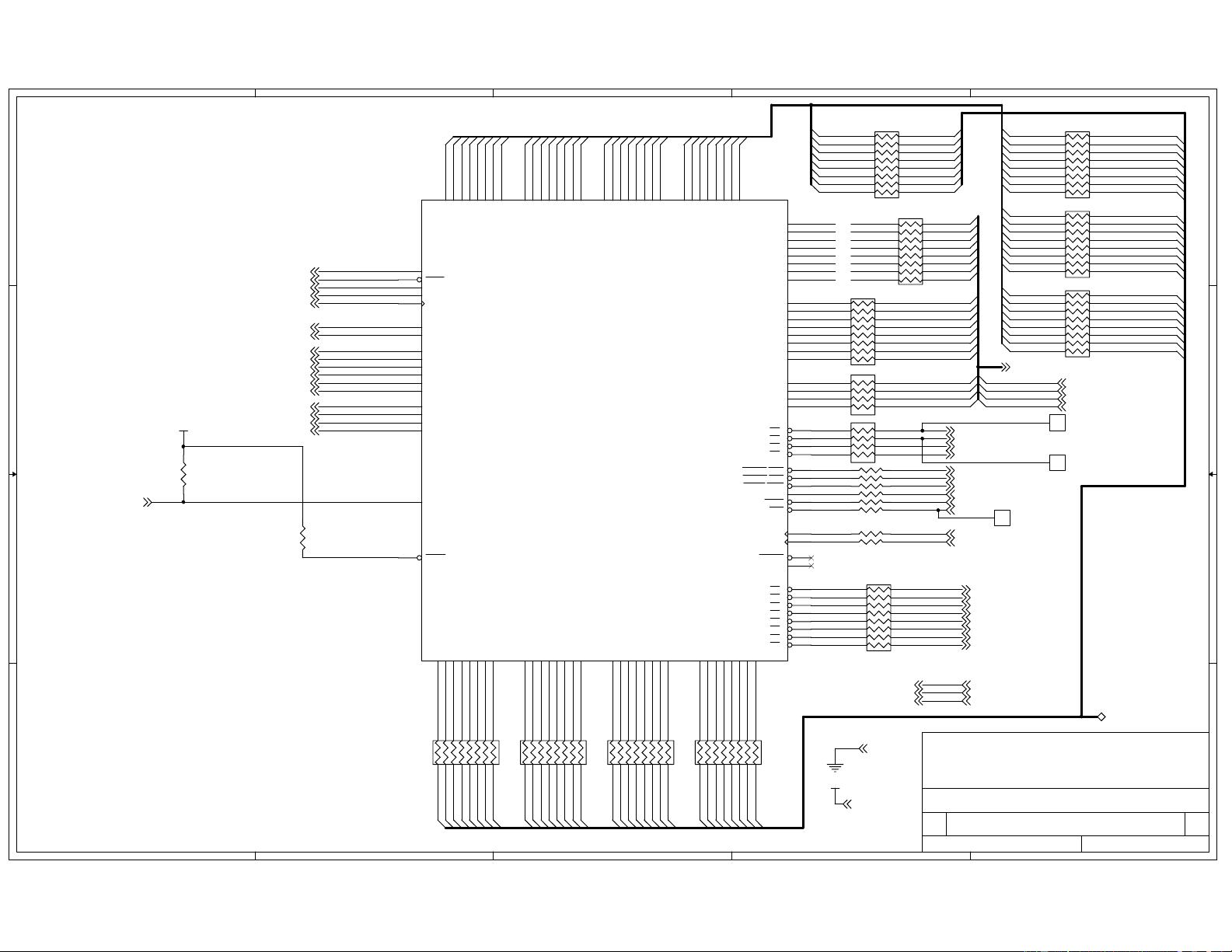

A A

B B

C C

D D

NOTE 4.1: PLACE ALL

33-OHM RESISTORS AND

RESISTOR NETWORKS AS

CLOSE A SPOSSIBLE TO

THE CORRESPONDING U25

PINS.

NOTE: ALTERNATE PIN

NAMES

DM642 EMIF AND

TERMINATORS

506842

A

DM642 EVALUATION MODULE

B

425

Monday, August 11, 2003

SPECTRUM DIGITAL INCORPORATED

Title

Size Document Number Rev

Date: Sheet

of

TBE5#

TBE3#

TBE6#

TBE7#

TBE2#

TBE4#

TBE0#

TBE1#

DSP_EMU1

DSP_EMU4

ED17

ED2

ED8

ED30

EA12

EA13

ED38

ED48

DSP_EMU0

ED2

ED10

ED25

EA19

ED39

ED13

ED15

ED[0:31]

ED4

ED22

EA11

BEz4

DSP_EMU6

ED23

ED7

ED18

BEz7

ECLKO2

ED37

ED49

DSP_TMS

ED14

ED12

ED23

BEz5

SDCASz

ED33

ED53

ED12

ED1

ED20

ED16

ED17

ED29

DSP_EMU9

ED22

ED30

ED7

BEz0

BEz6

ECLKO1

ED50

DSP_EMU5

DSP_EMU11

ED6

ED19

ED8

ED6

ED20

EA18

SDRASz

SDWEz

ED35

ED54

ED11

ED31

ED0

ED25

ED21

ED11

ED14

ED21

EA16

EA22

DSP_TDO

DSP_EMU3

DSP_EMU8

ED29

ED1

ED15

BEz3

PDTz

ED51

ED4

ED26

ED19

EA17

ED55

ED28

ED10

ED5

ED0

ED5

ED13

EA15

ED32

DSP_EMU7

DSP_EMU10

ED24

ED9

ED24

EA21

BEz2

SOE3z

ED52

DSP_TCLK

DSP_TDI

ED3

ED27

ED3

ED31

EA14

ED36

DSP_EMU2

ED9

ED18

ED16

ED26

ED27

ED28

EA20

BEz1

SDCKE

ED34

DSP_TRST#

TEA17

TEA15

TEA14

TEA3

TEA13

TEA12

TEA11

TEA21

TEA5

TEA19

TEA20

TEA4

TEA18

TEA22

TEA16

TEA21

TEA19

TEA20

TEA22

GND

EA3 EA3

EA4

EA5

TEA7

TEA6

TEA10

TEA9

TEA8

EA4

EA9

EA10

EA6

EA5

EA7

EA6

EA8

EA7

EA10

EA9

EA8

CE0z

CE1z

CE3z

CE2z

ED57

ED62

ED59

ED63

ED56

ED61

ED60

ED58

TED5

TED30

TED31

TED49

TED34

TED56

TED6

TED10

TED27

ED41

TED19

TED16

TED9

TED11

ED45

TED52

TED4

TED22

TED60

TED32

TED7

TED17

ED43

TED12

ED47

TED61

TED35

TED57

TED1

TED47

TED46

TED45

TED44

TED29

TED24

TED15

TED51

TED13

TED53

TED63

TED54

TED62

TED8

TED55

TED50

ED44

TED25

TED48

TED58

TED33

TED43

TED40

TED3

TED59

TED0

ED46

TED26

TED21

TED18

TED36

TED39

ED42

TED41

TED2

TED28

TED37

TED20

TED38

TED14

TED23

ED40

TED42

TBE2# (9,10)

TBE3# (9,10)

TBE1# (9,10)

TBE0# (9,10)

TBE6# (9)

TBE7# (9)

TBE4# (9)

TBE5# (9)

TEA[3..22] (2,9,10)

TED[0..63] (9,10)

TSDRAS# (9,10)

TECLKOUT2 (10)

TECLKOUT1 (9)

TSDCKE (9)

TPDT#

TSOE3# (11,16)

TSDWE# (9,10)

TSDCAS# (9,10)

TCE0# (9)

TCE1# (11,16)

TCE2# (10,11)

TCE3# (10,11)

TEARDY(10)

DSP_EMU1(5)

DSP_EMU0(5)

DSP_EMU2(5)

DSP_EMU3(5)

DSP_TCLK(5)

DSP_TDI(5)

DSP_TRST#(5)

DSP_TDO(5)

DSP_TMS(5)

DSP_EMU5(5)

DSP_EMU8(5)

DSP_EMU4(5)

DSP_EMU9(5)

DSP_EMU6(5)

DSP_EMU7(5)

DSP_EMU11(5)

DSP_EMU10(5)

BOOT_MODE1 (2,10)

BOOT_MODE0 (2,10)

EMIF_ECLKINSEL0 (2,10)

EMIF_ECLKINSEL1 (2,10)

VCC3.3

GND

TSDWE#(9,10)

TAOE# (9,10)

TSDCAS#(9,10)

TAWE# (9,10)

TSDRAS#(9,10)

TARE# (9,10)

VCC3.3

VCC3.3

RN5

RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

R9733

RN17 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

RN1 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R9433

RN6

RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

R9833R37

4.7K

R92

10K

RN8 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

RN7 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R9633

EMIF and Emulation

U25A

DM642

B24

A24

B23

B22

C22

A23

C21

B21

D21

A21

C20

B20

D20

A20

D19

C19

H24

H23

G26

G23

G25

G24

F26

F23

F25

F24

E25

E24

D25

D26

C25

C26

M24

M23

N26

N24

N23

P26

P24

P23

R24

R23

T25

T24

U26

U25

U24

V23

V26

V25

V24

U23

L24

L23

M26

M25

R26

R25

T23

T22

K25

K24

K23

L26

J24

J25

K26

L25

R22

M22

J26

J23

N22

P22

AD26

AD25

AC25

AC26

AB24

AB25

AB23

AA24

AA25

AA23

AA26

Y24

Y25

Y23

Y26

W23

AD19

AC19

AF20

AC20

AE20

AD20

AF21

AC21

AE21

AD21

AE22

AD22

AD23

AE23

AF23

AF24

W24

L22

E15

A18

A16

D14

B18

A15

C14

B15

C15

D15

B16

C16

A17

D16

B17

C17

D17

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

ED16

ED17

ED18

ED19

ED20

ED21

ED22

ED23

ED24

ED25

ED26

ED27

ED28

ED29

ED30

ED31

EA03

EA04

EA05

EA06

EA07

EA08

EA09

EA10

EA11

EA12

EA13

EA14

EA15

EA16

EA17

EA18

ECLKINSEL0 / EA19

ECLKINSEL1 / EA20

BOOTMODE0 / EA21

BOOTMODE1 / EA22

BE0

BE1

BE2

BE3

BE4

BE5

BE6

BE7

CE0

CE1

CE2

CE3

SDRAS/AOE

SDCAS/ARE

SDWE/AWE

SDCKE

SOE3

PDT

ECLKOUT1

ECLKOUT2

HOLDA

BUSREQ

ED32

ED33

ED34

ED35

ED36

ED37

ED38

ED39

ED40

ED41

ED42

ED43

ED44

ED45

ED46

ED47

ED48

ED49

ED50

ED51

ED52

ED53

ED54

ED55

ED56

ED57

ED58

ED59

ED60

ED61

ED62

ED63

HOLD

ARDY

TMS

TDI

TCLK

TRST

TDO

EMU0

EMU1

EMU2

EMU3

EMU4

EMU5

EMU6

EMU7

EMU8

EMU9

EMU10

EMU11

TP22

TP

1

TP23

TP

1

R12733

RN2 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

RN16 RPACK4-33

1

2

3

4 5

6

7

8

RN11

RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

R9533

RN12

RPACK8-33

1

2

3

4

5

6

7

89

10

11

12

13

14

15

16

RN15 RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R9333

RN13 RPACK4-33

1

2

3

4 5

6

7

8

RN14

RPACK8-33

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

R12633

TP7

TP

1

剩余24页未读,继续阅读

资源评论

drjiachen

- 粉丝: 172

- 资源: 2138

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- transformer-6layer.hbm

- 中小型制造企业质量管理系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 高校危化试剂仓储系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 驾校预约学习系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于下垂控制,引入电感,两台单相逆变器非同步并机 默认发2018b 控制方式为下垂控制且引入电感(图2),使用二阶广义积分器(SOGI)实现有功和无功解耦 引入电感前后有功无功对比如图4和图5 功能

- 西南交通大学车辆工程专业大四上车辆综合实训ame仿真模型

- 同城上门喂遛宠物系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于javaweb的在线远程考试系统.zip

- 招生宣传管理系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- comsol相控阵检测 16阵元放在有机玻璃斜楔上检测工件内部缺陷,都是固体力学,图1红圈?位置的波为横孔缺陷的反射接收波 工件里的波看起来好像没怎么折射,其实那是斜楔纵波声速接近工件横波声速造成的

- 高校疫情防控web系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 高校汉服租赁网站--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 高校物品捐赠管理系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 小米音箱 MiGPT源码包

- 高校竞赛管理系统--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 智慧社区居家养老健康管理系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功