消抖动电路(一)

消除抖动电路

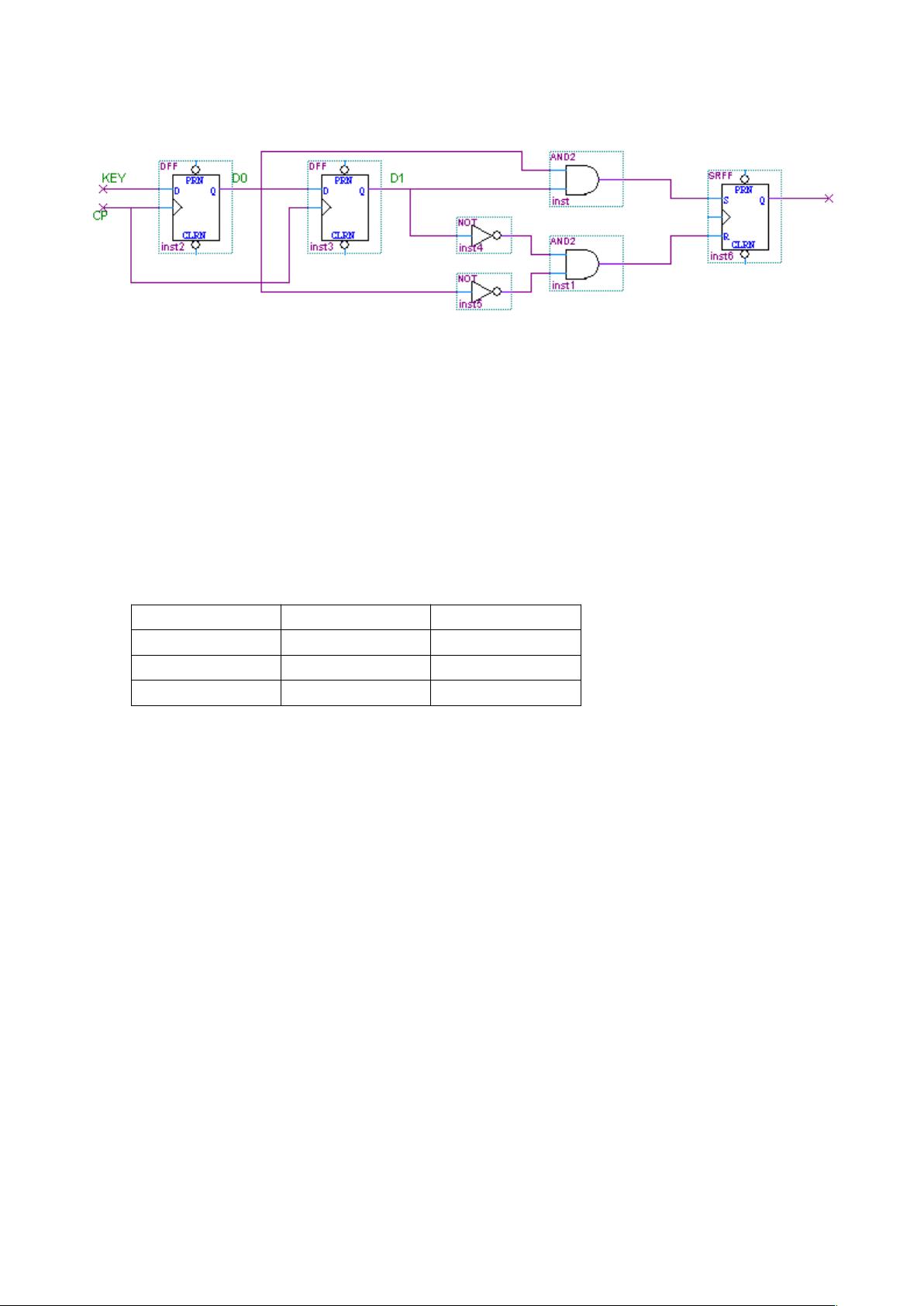

图中的做法是,先将按键的信号,引致 Key 脚,其中 CP 是电路的时钟脉冲信号(应视为

取样信号,约为 8ms 左右)。Key 信号经过两级的 D 触发器延迟后,然后用 RS 触发器处

理。

此处 RS 触发器前端连接与非门的处理原则是:

1、因为一般人的按键速度至多是 10 次/秒,即一次按键时间是 100ms,所以按下的时间可

估算为 50ms。以取样信号 CP 频率为 8ms,则可取样到 6 次。

2、对于不稳定的噪声在 4ms 以下,则之多之抽样一次。

3、上述 RS 触发器之前接上 AND-NOT 之后,则 SR 的组态仅有:

S R DLY_OUT

0 0 不变

1 0 1

0 1 0

即 D0 为 1,且 D0 也为 1 时,结果 S=1,R=0,DLY_OUT 才会输出 1.这代表被取样的

Key 信号,能被连续取样两次 1,所以认定他已是稳定的按下按钮。

同理 D0 为 0,且 D0 也为 0 时,结果 S=0,R=1,DLY_OUT 才会输出 0.这代表被取样的

Key 信号,能被连续取样两次 0,所以认定他已是稳定的放掉按钮。

同理若是 D0 为 1,且 D1 为 0,结果 S=0,R=0;DLY_OUT 将维持先前的输出不变。

D0=0,D1=1 也是如此。

总之,必须取样到两次 1 才会输出 1,两次 0 才会输出 0.

不过由于电子时钟的消除抖动,是为了作时间计数,所以纵使消除之后的图中的

DLY_OUT 信号输出可能时间宽度过长,而导致计数 1 次以上的错误发生,所以加一级微

分电路。

注意:

1

、抖动消除电路所使用的脉冲信号的频率必须比其它电路使用的脉冲信号的频率高;

通常将扫描电路或

LED

显示电路的工作频率定在

24Hz

左右,将抖动消除电路的工作频率

定在

128Hz

左右,两者的工作频率是通常的

4

倍或更高。

2

、要求信号的稳定时间可以由

D

触发器的个数和

CLK

时钟来决定。

消抖动电路(二)

其实和上面的原理是一样的,都是通过每个脉冲上升沿取样,连续几次取到‘1’才输出‘1’,