没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

106页

此文档对于JESD标准DDR3做中文解读,轻松理解DDR3标准。 问题举例: ** 你真的理解SDRAM的S吗? ** 为什么Write一般是Center Aligned, Read是Edge Aligned? ** BC4有啥用? ** 为什么会有Dynamic ODT? ** BIOS是如何识别DIMM是DDR3或者DDR4的? ** XMP是什么? ** 为什么有Write Leveling? ** 有人会问,有Read Leveling吗? ** Prefetch的作用 ** Dram Size和Page Size如何计算? ** 为什么有MRS,没有MRR? ...... ** 行业标准: 作者有数年spec经验, 熟悉JEDEC标准建立的过程. ** 专业: 数年dram问题debug,spec解读专业到位。 ** 咨询: 承诺文档解读有疑问,可以免费每天3个问题的解答。 ** 退款: 作者承诺如果对于文档解读不满意,可线下联系作者申请退款,作者就有这样的自信敢承诺! 如对内容质量有疑问,可提前私信咨询。

资源详情

资源评论

资源推荐

JESD79-3F DDR3精解

2021

Reference

• JEDEC Spec/Documents

• DRAM Patents

• DRAM Datasheet

• DRAM Internet Matierals

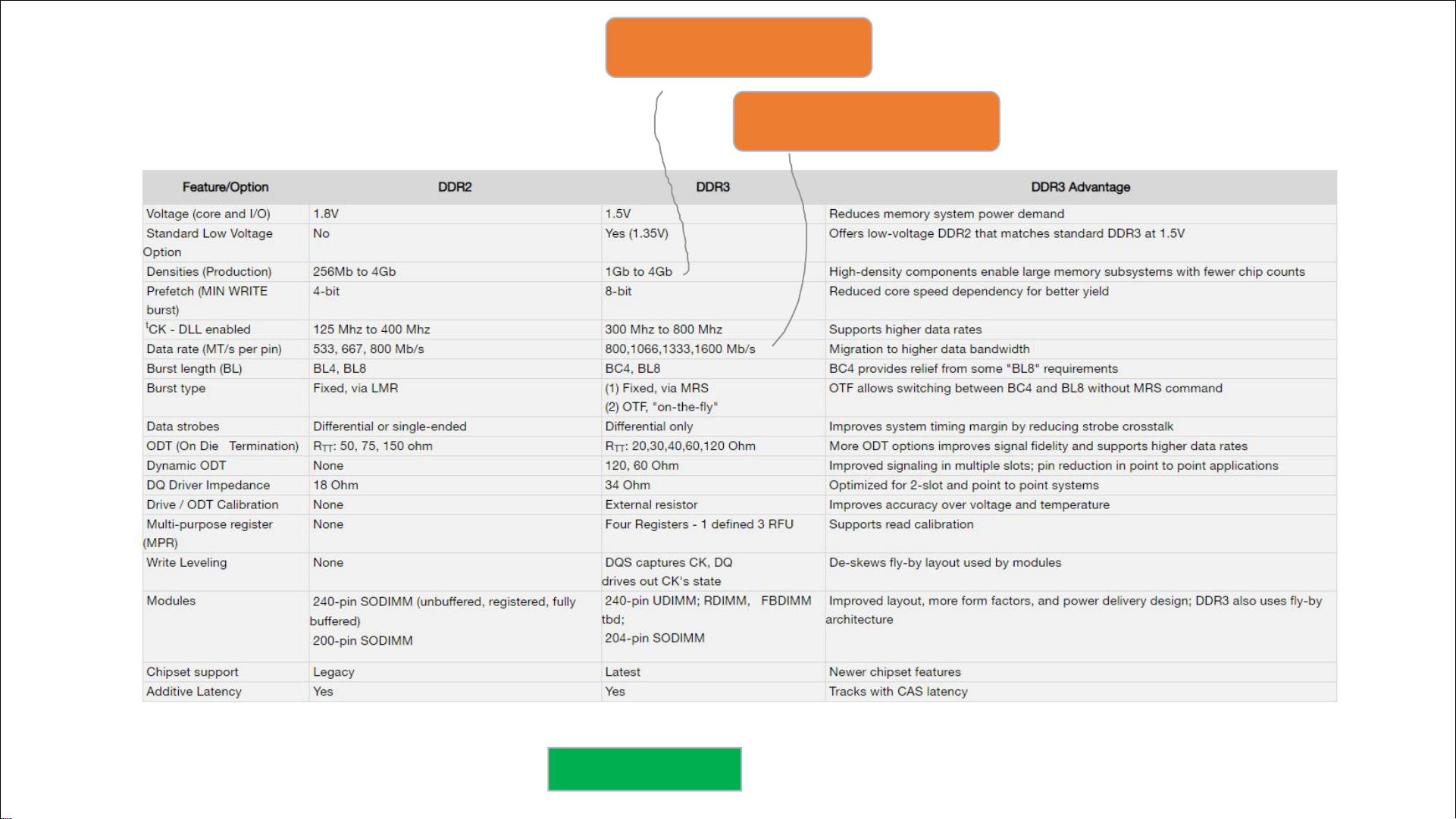

DDR2 vs DDR3

From: Micron

Also Support:

1866 2133

Spec: 512Mb~8Gb

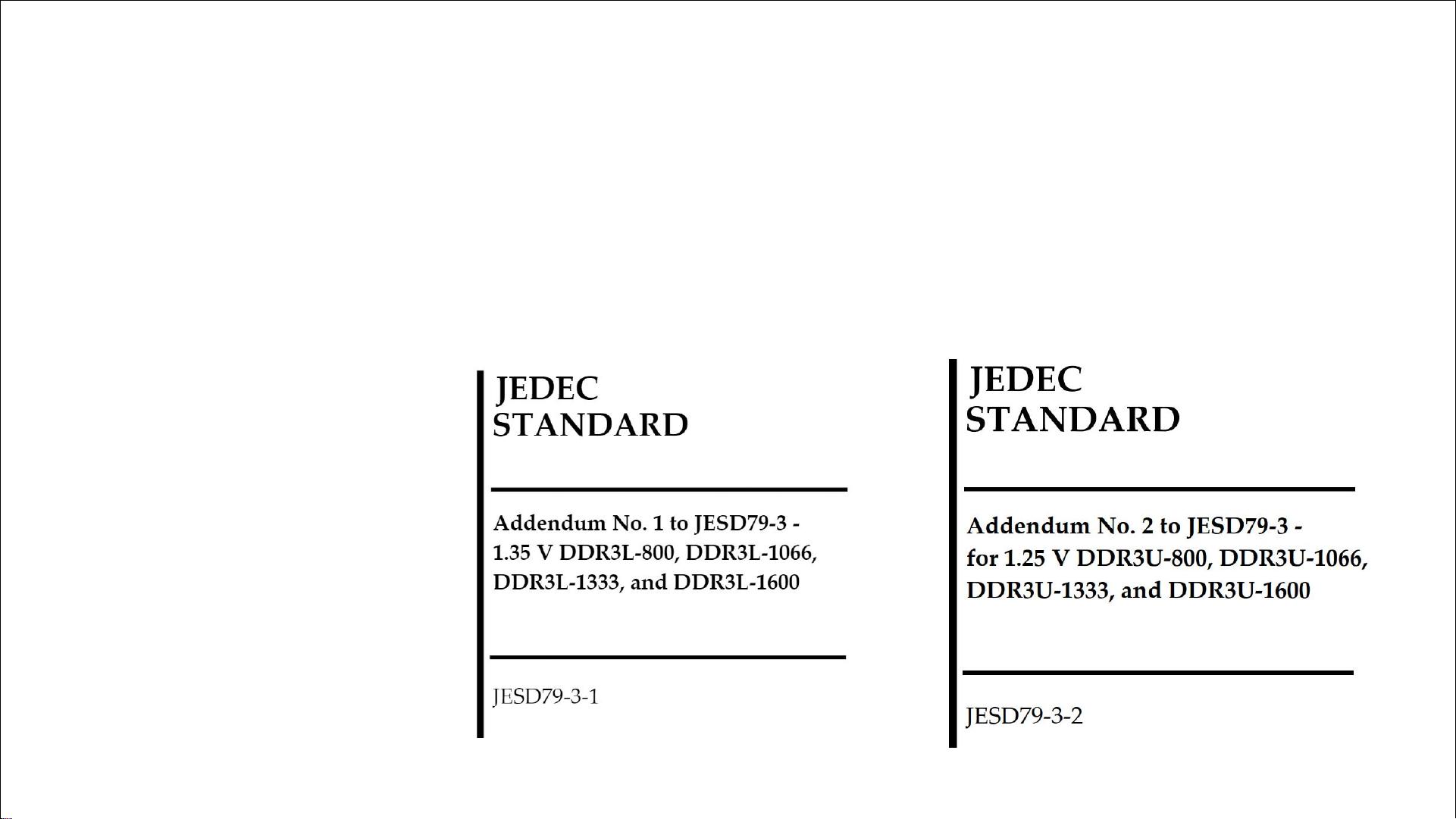

DDR3L/DDR3U和DDR3的关系是什么?

• DDR3 Low Power版本.

• DDR3L: VDDQ 1.35V.

• DDR3U: VDDQ 1.25V --> 超级低压版.

你真的理解SDRAM的S吗?

• Synchronous(同步) DRAM.

• 单纯理解什么是"同步"和"异步"

• 一个函数A调用另一个函数B,等待B完成后A才继续执行,这是同步。

• A调用B, 不用阻塞地等待B完成,

当B完成后,B通知A完成,这是

异步。

• 编程世界里告诉我们,异步效率

更高,可是在DRAM世界里是这样

吗?

• mov eax, [esp+4]

• ESP+4通过MMU转换成物理地址A

• 从DRAM地址A获取数据D, 放到寄存器

eax中.

• 如果上面的过程还不是同步,而是需

要DRAM异步处理完再通知CPU, CPU该是

多不着急!

剩余105页未读,继续阅读

程序员小迷

- 粉丝: 711

- 资源: 16

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论24