jtag中文介绍.pdf

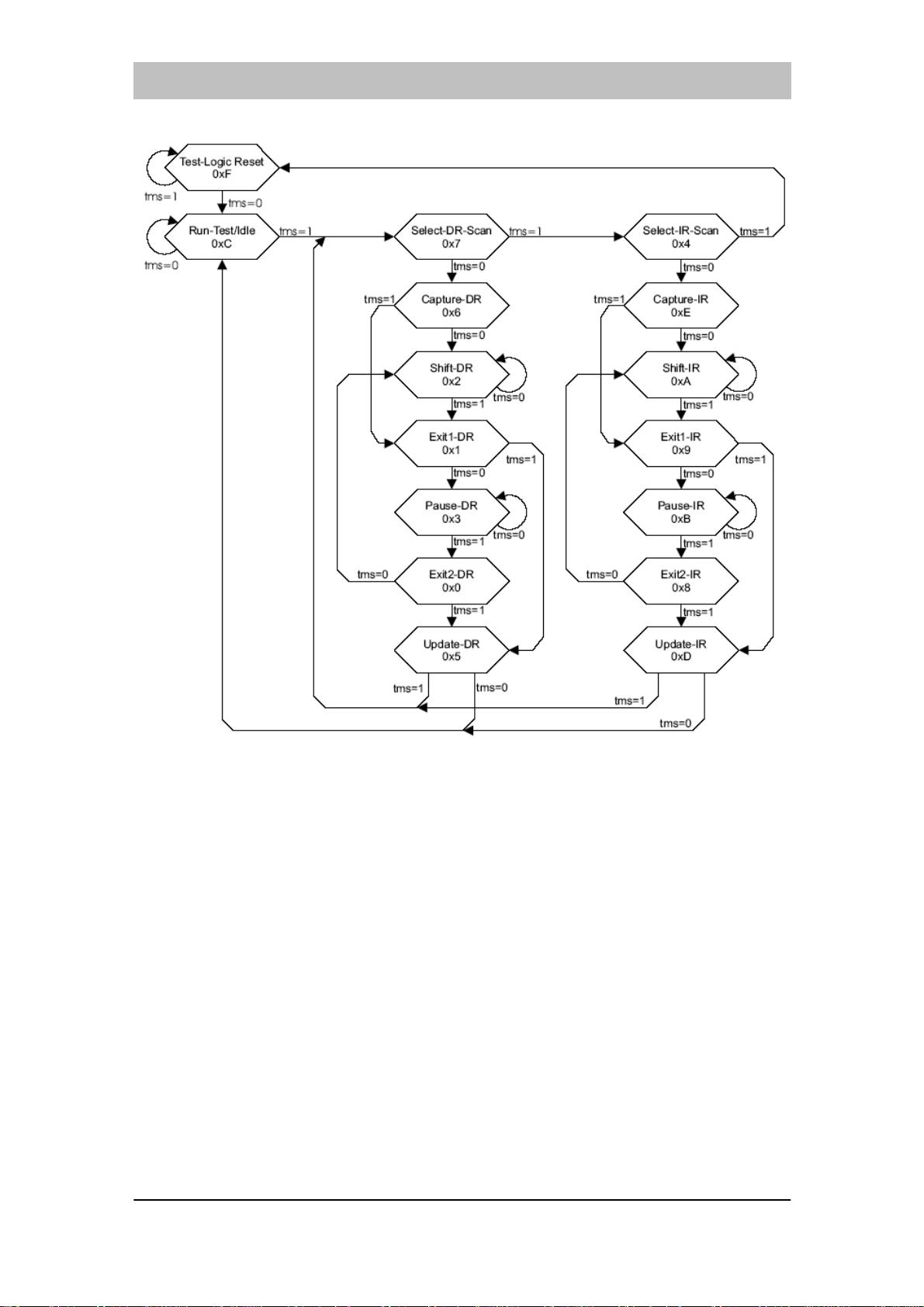

### JTAG调试原理详解 #### 一、引言 本文旨在详细介绍ARM JTAG调试的基本原理。主要内容涵盖了TAP (Test Access Port) 和 BOUNDARY-SCAN ARCHITECTURE 的概念介绍,随后结合 ARM7TDMI 架构深入解析 JTAG 调试的具体机制。 #### 二、IEEE Standard 1149.1 - Test Access Port and Boundary-Scan Architecture ##### 2.1 边界扫描(Boundary-Scan) 边界扫描技术是 JTAG 调试中的核心概念之一。它基于在接近芯片输入输出管脚的位置增设移位寄存器单元的想法。这些移位寄存器单元分布在芯片边缘,因此被称为边界扫描寄存器(Boundary-Scan Register Cell)。当芯片进入调试模式时,边界扫描寄存器能够将芯片与其外部的输入输出信号隔离。通过边界扫描寄存器单元,可以实现对芯片输入输出信号的观察与控制。 - **输入管脚**:可以通过与其相连的边界扫描寄存器将信号加载到该管脚。 - **输出管脚**:可以通过与其相连的边界扫描寄存器“捕获”该管脚上的输出信号。 在正常运行状态下,边界扫描寄存器对芯片而言是透明的,即不会影响其正常运行。边界扫描寄存器提供了一种简便的方法来观察和控制需要调试的芯片。此外,芯片输入输出管脚上的边界扫描寄存器单元可以串联起来形成边界扫描链(Boundary-Scan Chain),用于实现完整测试功能。 ##### 2.2 TAP (Test Access Port) TAP 是一个通用端口,通过它可访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。TAP 的控制是由 TAP Controller 完成的。TAP 包括以下五个信号接口: - **TCK (Test Clock Input)**:测试时钟输入信号,用于同步所有 JTAG 操作。 - **TMS (Test Mode Select)**:测试模式选择信号,用于控制 TAP 控制器的状态机切换。 - **TDI (Test Data Input)**:测试数据输入信号,用于向指令寄存器和数据寄存器输入数据。 - **TDO (Test Data Output)**:测试数据输出信号,用于从数据寄存器输出数据。 - **TRST (Test Reset)**:测试复位信号,用于复位 TAP 控制器和边界扫描链。 #### 三、ARM JTAG 调试原理 ARM JTAG 调试机制主要包括两个方面:TAP 控制器和边界扫描架构。 ##### 3.1 TAP Controller 工作原理 TAP 控制器是 JTAG 调试的核心组件,它负责管理 JTAG 接口的所有操作。TAP 控制器具有一个状态机,该状态机定义了四种不同的状态: 1. **测试逻辑重置 (Test-Logic-Reset)**:在此状态下,所有寄存器都被复位。 2. **运行测试/空闲 (Run-Test/Idle)**:在此状态下,可以执行数据寄存器的数据移位操作。 3. **选择 DR 扫描 (Select-DR-Scan)**:在此状态下,可以选择数据寄存器进行操作。 4. **捕获 DR (Capture-DR)**:在此状态下,可以从数据寄存器捕获数据。 通过 TMS 信号线,可以在这些状态之间切换。 ##### 3.2 数据寄存器 (Data Register, DR) 数据寄存器是 JTAG 架构中用于存储输入输出信号的关键组件。在 ARM7TDMI 等处理器中,边界扫描链属于数据寄存器的一种。边界扫描链可以实现对芯片输入输出信号的控制和观察。 ##### 3.3 指令寄存器 (Instruction Register, IR) 指令寄存器用于存储指令,从而控制数据寄存器的操作。例如,在多条边界扫描链中选择特定的一条进行操作。 #### 四、总结 JTAG 调试是一种广泛应用于嵌入式系统的调试方法。通过 TAP 控制器和边界扫描架构,可以实现对芯片内部状态的监控和修改。本文详细介绍了 JTAG 调试的基础知识,包括 TAP 控制器的工作原理、边界扫描链的作用以及 ARM JTAG 调试的具体实现。理解这些概念有助于深入掌握 ARM 处理器及其他嵌入式系统的调试技巧。

剩余21页未读,继续阅读

zwp2212014-02-17介绍的不详细

zwp2212014-02-17介绍的不详细

- 粉丝: 208

- 资源: 102

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功