SPRA999

2

Creating a Second-Level Bootloader for FLASH Bootloading on TMS320C6000 Platform With Code Composer Studio 2.2

2.3 Writing the Secondary Bootloader 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 The Section Copy Table 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Programming Flash 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 Hex Conversion Utility 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.2 Flash Burn Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3 Tips for Debugging 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 References 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix A 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 C620x/C670x Bootloader 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Bootloading a Non-BIOS Application 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.1 Defining Memory Segments 19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.2 Memory (COFF) Section Placement 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.3 Creating the Section Copy Table 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Figures

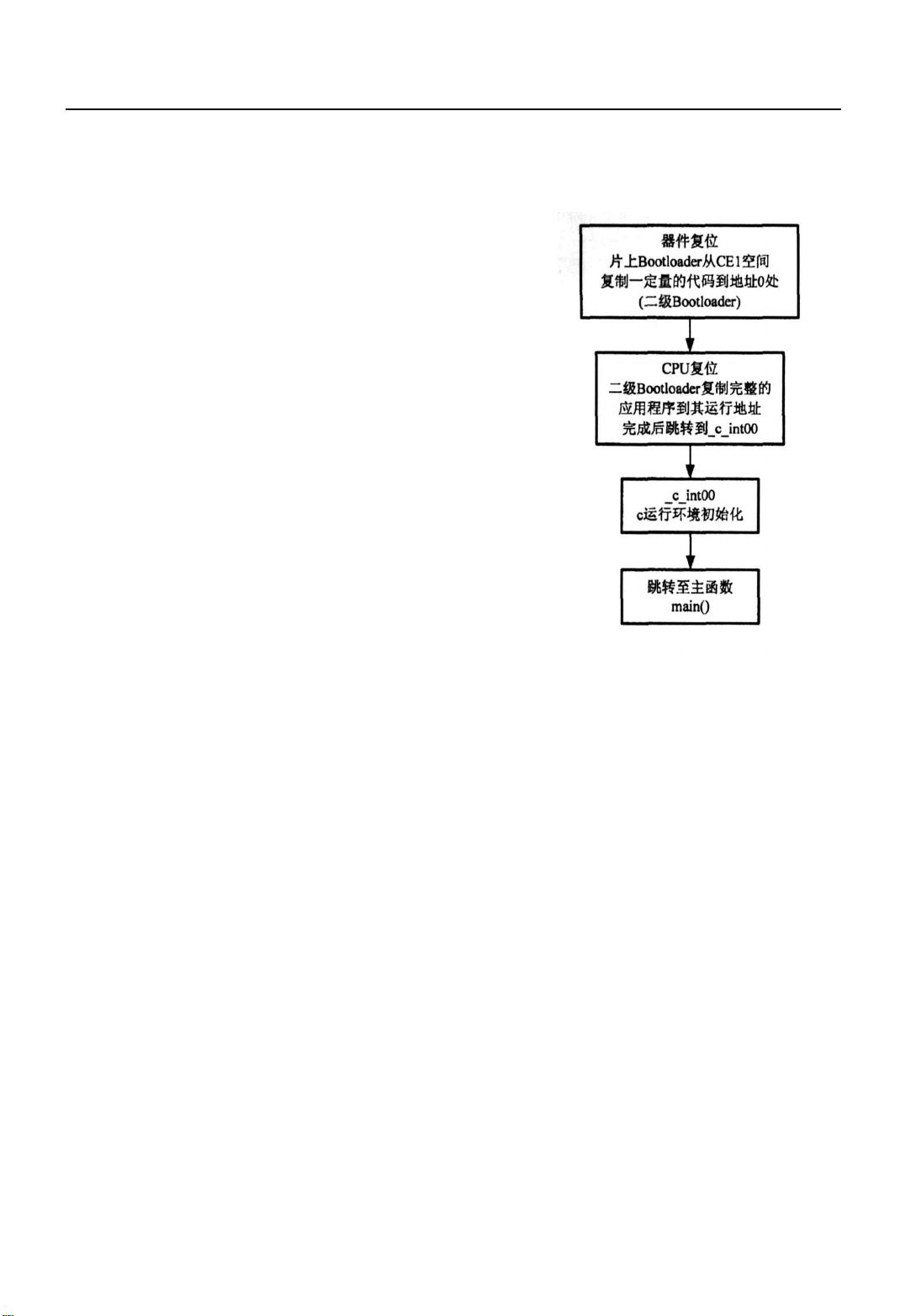

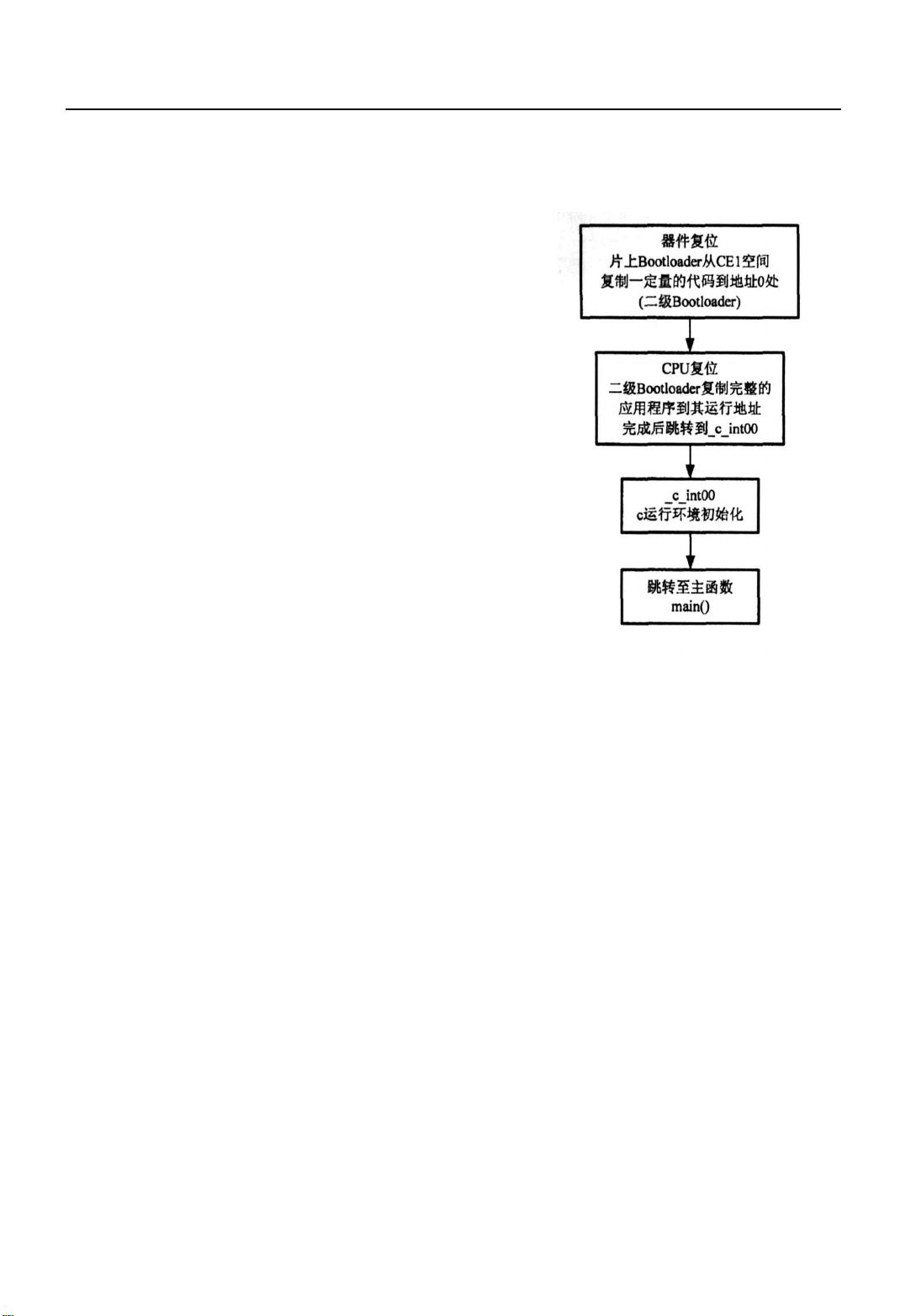

Figure 1 Start-Up Sequence of Application which Uses Secondary Bootloader 3. . . . . . . . . . . . . . . .

Figure 2 Load/Run Address Specification Using DSP/BIOS GCONF Interface 8. . . . . . . . . . . . . . . .

Figure 3 Boot Code 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4 Flash Programming Sequence 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5 Hex Command File 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 6 Hex Command File using the –boot Option 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure A−1 Non-BIOS Memory Segment Definition 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure A−2 Non-BIOS Memory Section Placement 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Tables

Table 1 Memory Section Definitions 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2 DSP/BIOS Sections and Suggested Memory Placement 7. . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 3 Copy Table Format 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 4 Hex Utility Boot Options 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 Introduction

In many DSP applications there is a need to copy code and/or data from one location to another

at boot. C6000 DSPs offer three types of boot configurations: no boot process, ROM boot

process, and host boot process. The boot process that is selected is determined by the

configuration of the BOOTMODE pins. Refer to the device specific data sheet to learn about the

boot modes supported by a particular device and configuring the device for a particular boot

mode.

The most commonly selected boot configuration is the ROM boot process (also referred to as

the on-chip bootloader in this document). When selected, the ROM boot process copies a fixed

amount of memory located at the beginning of the external ROM to address 0 using the

DMA/EDMA controller. The transfer is automatically completed as a single frame block transfer

from ROM to address 0. This transfer occurs when the device is released from external reset

while the CPU is internally stalled. Upon completion of the block transfer the CPU is released

from the stalled state and starts executing from address 0.

DSP boot.rar (3个子文件)

DSP boot.rar (3个子文件)  DSP boot

DSP boot  boot.asm 2KB

boot.asm 2KB DSP二级引导程序的设计与实现.pdf 240KB

DSP二级引导程序的设计与实现.pdf 240KB 2004JUN16_DSP_MEM_AN01.pdf 260KB

2004JUN16_DSP_MEM_AN01.pdf 260KB

flounding0012012-11-30很有用的资料,可以帮助理解底层

flounding0012012-11-30很有用的资料,可以帮助理解底层 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功