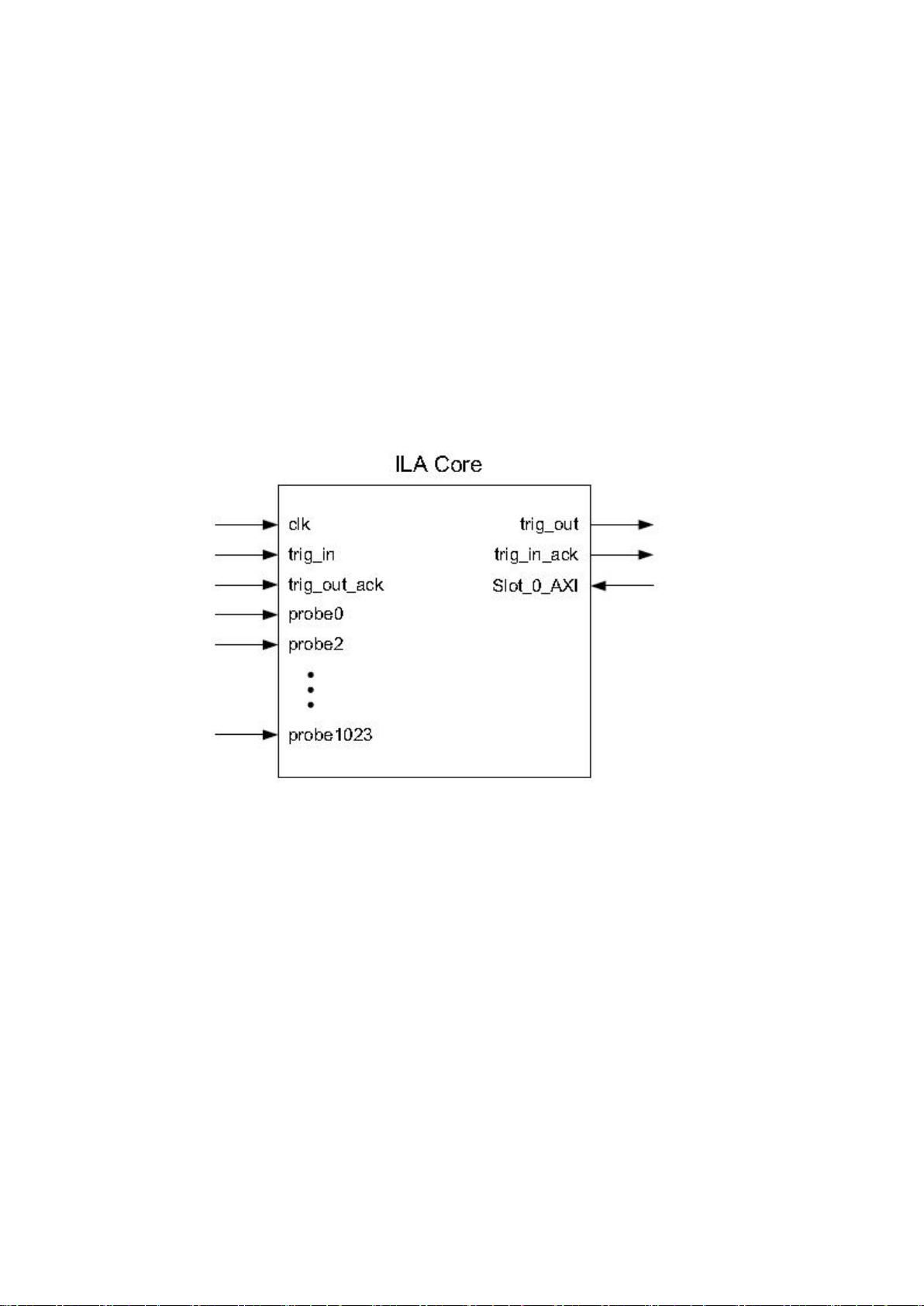

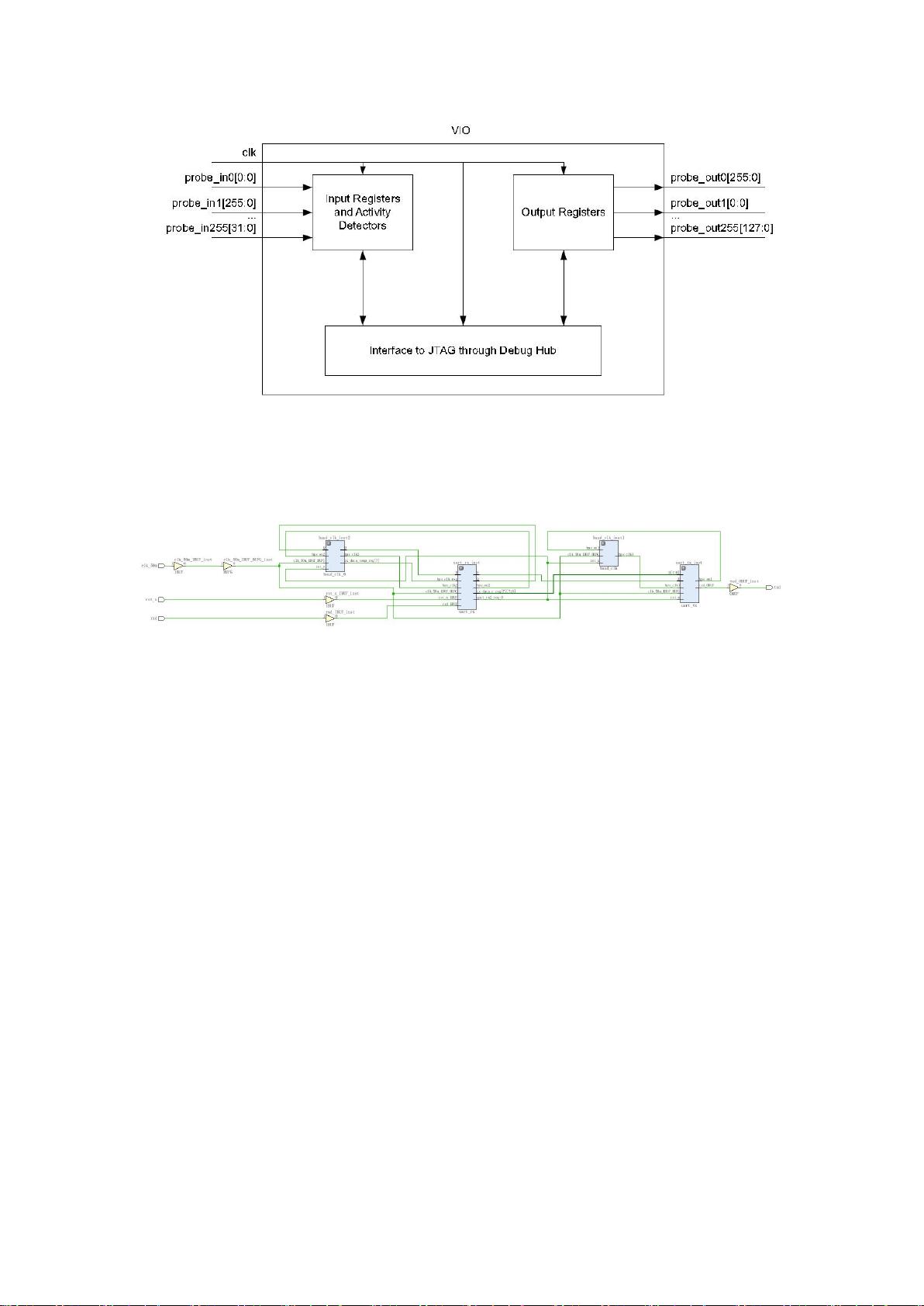

### Xilinx Vivado 硬件诊断:ILA与VIO的使用详解 #### 一、背景知识 在FPGA的设计过程中,硬件诊断和验证是非常重要的环节。据统计,在一个典型的FPGA开发项目中,硬件诊断和验证工作可能占据整体开发周期的30%-40%。因此,熟练掌握FPGA设计工具的调试功能对于提高开发效率至关重要。 #### 二、ILA与VIO介绍 ##### 1. ILA (Integrated Logic Analyzer) ILA是Xilinx提供的一种用于FPGA内部信号监测的逻辑分析仪工具。它可以捕获和存储FPGA内部的信号波形,从而帮助开发者进行调试。ILA的核心结构如图1所示: **图1 ILA Core** ILA的主要组成部分包括时钟输入、探针输入以及用于存储采样数据的BRAM(Block RAM)。设计者可以通过配置ILA核来指定探针数量、采样深度以及每个探针的位宽。此外,ILA还支持通过JTAG接口与外部调试器通信。 - **探针输入**:用于连接FPGA内部信号。 - **采样深度**:定义了能够存储的样本数量。 - **探针位宽**:指定了每个探针可以监控的信号位数。 - **通信机制**:通过JTAG接口与调试核心集线器进行交互。 ##### 2. VIO (Virtual Input/Output core) VIO是一种可以实时监控和驱动FPGA内部信号的内核。它与ILA不同之处在于不需要额外的片上或片外RAM来存储数据。 - **信号类型**: - **Input Probes**:用于监控FPGA内部信号。 - **Output Probes**:允许向FPGA内部信号注入数据。 **图2 VIO Block Diagram** VIO的配置包括探针数量、探针位宽及初始化值等。通过VIO可以实现对FPGA内部信号的实时观察和控制。 #### 三、ILA与VIO的实际应用 以UART通信为例,本文将详细介绍如何利用ILA和VIO进行FPGA内部信号的调试。 ##### 1. UART模块概述 UART模块通常包含波特率时钟产生模块、串口接收模块以及串口发送模块。为了便于说明,我们以一个简单的UART工程作为示例。 **图3 UART 示例模块图** - **波特率时钟产生模块**:负责生成符合通信标准的时钟信号。 - **串口接收模块**:处理接收到的串行数据。 - **串口发送模块**:负责将数据转换成串行格式并发送出去。 ##### 2. IP创建与配置 ###### (1)ILA IP的创建与配置 - **步骤**: 1. 打开IP Catalog,搜索“ILA”并选择。 2. 双击打开ILA IP,并根据需求设置相关参数。 3. 设置探针位宽。 - **参数设置**: - **探针数量**:根据需要监控的信号数量进行设置。 - **采样深度**:定义了ILA可以保存的样本数量。 - **探针位宽**:根据被监控信号的位宽进行配置。 **图4 IPCatalog** **图5 ILA IP** **图6 ILA IP 参数设置** **图7 Ila IP位宽的设置** ###### (2)VIO IP的创建与配置 - **步骤**: 1. 在IP Catalog中搜索“VIO”并选择。 2. 配置VIO IP的相关参数。 3. 设置探针位宽和初始化值。 - **参数设置**: - **探针数量**:根据需要监控或驱动的信号数量进行设置。 - **探针位宽**:根据被监控或驱动信号的位宽进行配置。 - **初始化值**:设定探针的初始状态。 **图8 探头个数的设置** **图9 探头数据位宽和初始化值的设置** ##### 3. IP的例化与使用 完成IP配置后,需要在RTL代码中对其进行例化。之后,通过编程FPGA加载相应的设计文件。 **图10 Programming FPGA** ##### 4. 实时数据采集与调试 - **ILA的调试**: - **触发条件设置**:选择合适的触发信号(如rx_done),并设置触发条件。 - **数据观测**:当触发条件满足时,使用ILA观察FPGA内部信号的变化情况。 **图11 触发条件的设置** **图12 Ila IP观测到FPGA内部信号的变化** - **VIO的调试**: - **端口配置**:根据需要监控的信号配置相应的端口。 - **数据发送**:当特定条件满足时(如tx_en为1),通过VIO将数据从FPGA内部发送到外部设备。 **图13 VIO观测端口的设置** **图14 通过VIO将数据从FPGA内部发送到串口工具** #### 四、总结 ILA和VIO是Xilinx Vivado提供的强大调试工具,它们可以帮助开发者有效地监控和调试FPGA内部信号。相比于之前的工具(如ISE),Vivado的调试功能更为直观和便捷。通过本文的介绍,相信读者已经掌握了ILA和VIO的基本使用方法,这对于提高FPGA设计的效率有着重要意义。

剩余9页未读,继续阅读

- 粉丝: 4684

- 资源: 100

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Spring Cloud商城项目专栏 049 支付

- sensors-18-03721.pdf

- Facebook.apk

- 推荐一款JTools的call-this-method插件

- json的合法基色来自红包东i请各位

- 项目采用YOLO V4算法模型进行目标检测,使用Deep SORT目标跟踪算法 .zip

- 针对实时视频流和静态图像实现的对象检测和跟踪算法 .zip

- 部署 yolox 算法使用 deepstream.zip

- 基于webmagic、springboot和mybatis的MagicToe Java爬虫设计源码

- 通过实时流协议 (RTSP) 使用 Yolo、OpenCV 和 Python 进行深度学习的对象检测.zip

信息提交成功

信息提交成功