Booth乘法器实验报告.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

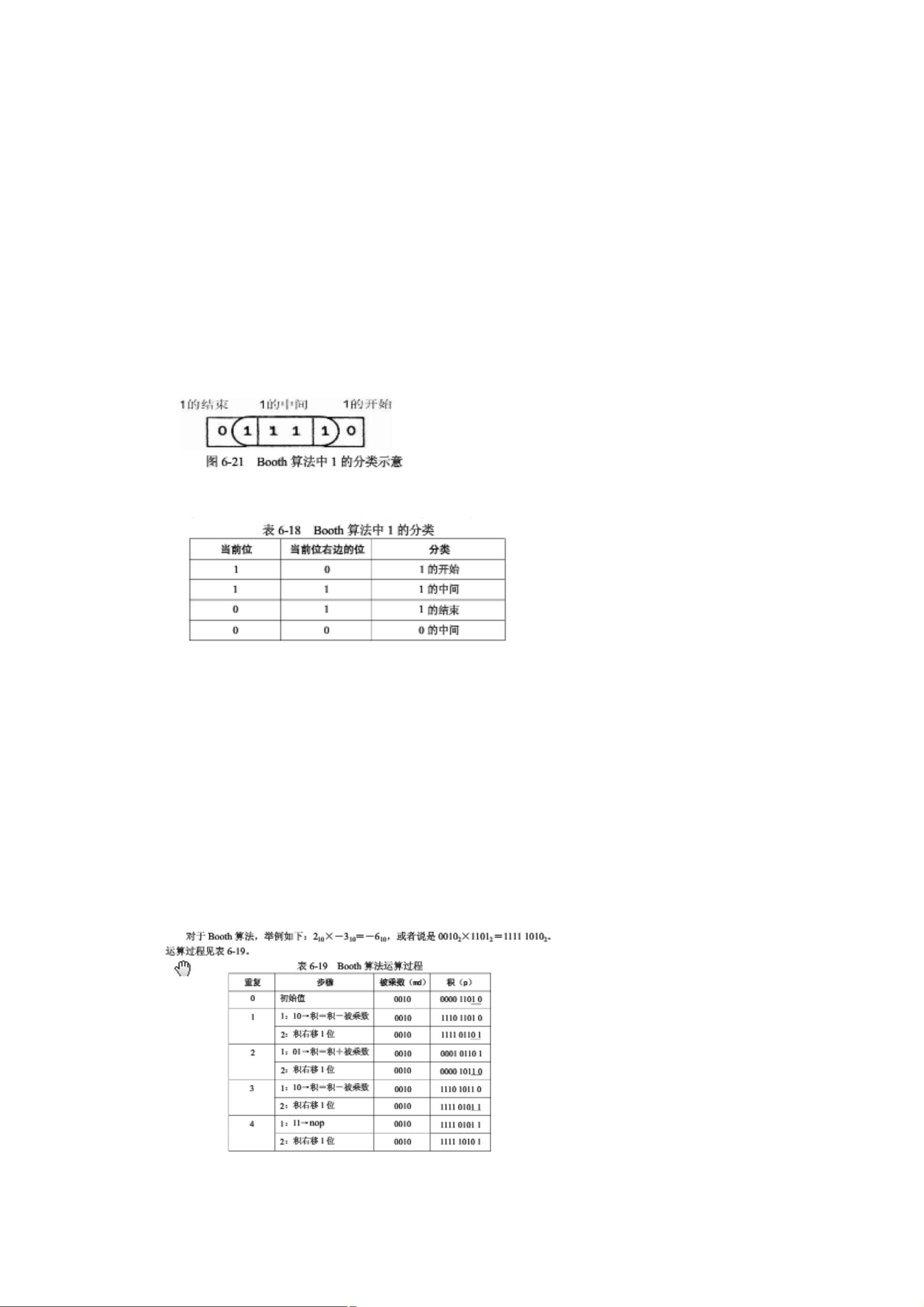

Booth乘法器是一种高效的计算有符号数乘法的算法,尤其在处理长整数时,相比传统的乘法算法能显著减少运算次数。该算法由Alan Booth于1950年提出,其核心思想是利用减法来替代部分加法,以减少移位操作的次数。在当时的计算机硬件中,移位速度远快于加法,所以Booth算法在效率上有很大优势。 Booth算法的工作流程如下: 1. 将乘数分解为“开始”、“中间”和“结束”的1,对于连续的0则不做操作。 2. 根据乘数的相邻两位进行判断,共有四种情况: - 00: 代表0的中间,不做任何操作。 - 01: 代表1的结束,将被乘数加到积的左半部分。 - 10: 代表1的开始,积的左半部分减去被乘数。 - 11: 代表1的中间,不做任何操作。 3. 积寄存器右移一位,对于有符号数乘法,使用算术右移以保留符号位。 4. 如果乘数或被乘数为负数,使用它们的补码表示,最终积也为负数时,输出结果同样为补码形式。 在实验步骤中,使用QuartusII作为FPGA设计工具,通过JTAG端口与PC机的并行口连接,下载编译好的booth_multiplier.sof文件到FPGA中。实验台上通过模式开关设置工作模式,并调整时钟源。实验结果显示了不同输入情况下Booth乘法器的运算过程,包括积的变化和每一步的操作。 具体到代码实现,使用VHDL语言编写FPGA逻辑。声明输入时钟clk、被乘数md、乘数mr,输出积p和最终结果标志final。在进程中,根据时钟边沿触发操作,计数器counter用于控制移位和加减操作。当counter为偶数时进行移位,为奇数时根据乘数的相邻两位执行加减操作。加减操作依赖于p_s的低两位,如果为"10",则执行减法;如果为"01",则执行加法。 Booth乘法器实验报告详细介绍了Booth算法的原理、实验步骤以及具体代码实现,通过实验验证了算法的正确性和效率,展示了如何在硬件层面实现高效有符号数乘法。

陪跑2023-05-09资源内容详实,描述详尽,解决了我的问题,受益匪浅,学到了。

陪跑2023-05-09资源内容详实,描述详尽,解决了我的问题,受益匪浅,学到了。 2301_762770782024-06-07这个资源内容超赞,对我来说很有价值,很实用,感谢大佬分享~

2301_762770782024-06-07这个资源内容超赞,对我来说很有价值,很实用,感谢大佬分享~

- 粉丝: 9814

- 资源: 9653

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功