没有合适的资源?快使用搜索试试~ 我知道了~

资源详情

资源评论

资源推荐

1.同步复位和异步复位

复位电路是每个数字逻辑电路中最重要的组成部分之-。复位电路的工作日的有两个方

面:第一一是仿真的时候使电路进入初始状态或者其他预知状态:第二是对于综合实现的真实

电路,通过复位使电路进入初始状态或者其他预知状态。-般来说,逻辑电路的任何一个寄

存器、存储器结构和其他逻辑单元都必须要附加复位逻辑电路,以保证电路能够从错误状态

中恢复,可靠地工作。

复位方式大致分为两类,即同步复位和异步复位。这两种复位方式各有优缺点,其应用

场合也各不相同。

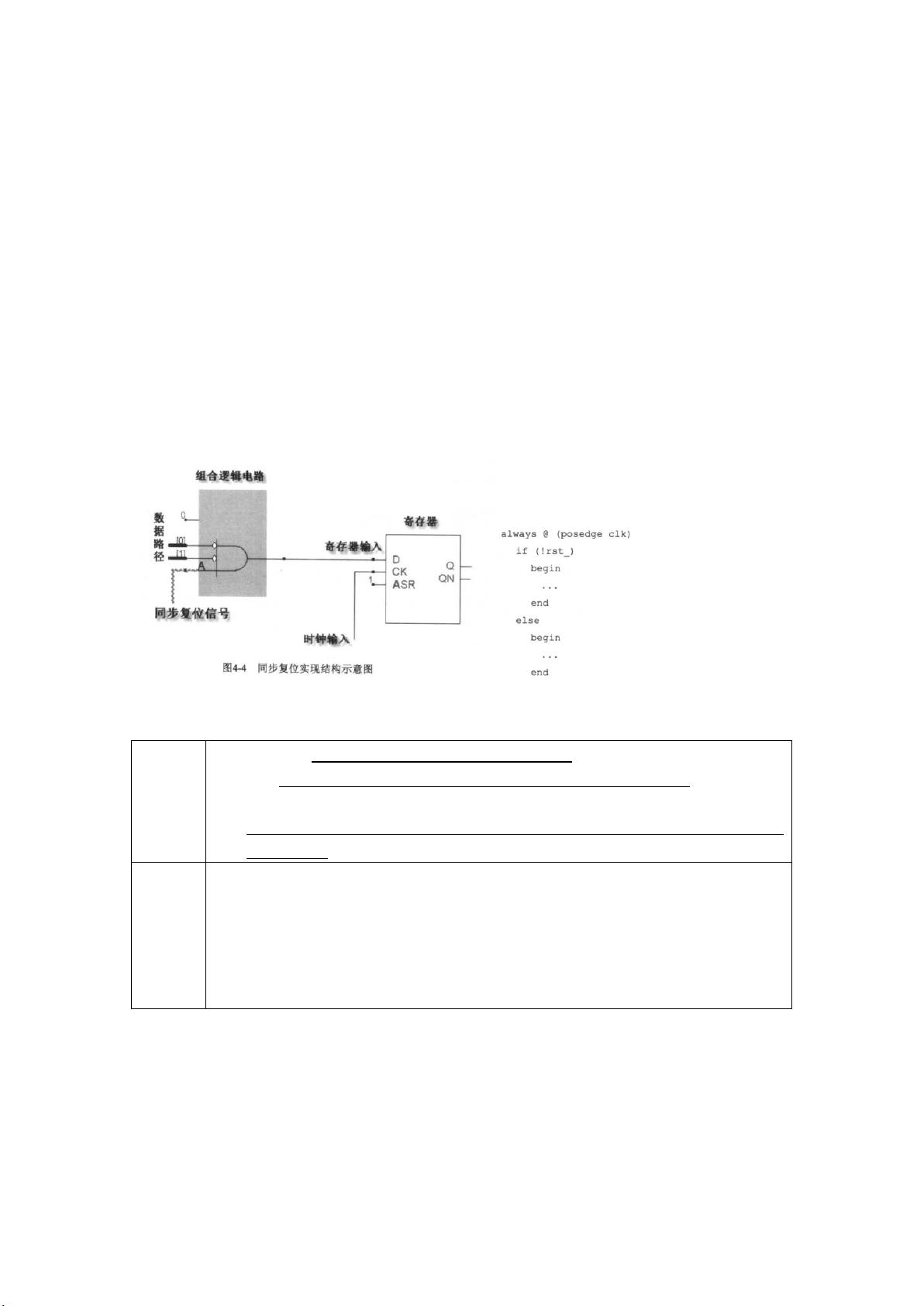

1.1 同步复位电路建模

所谓同步复位是指当复位信号发生变化时,并不立即生效,只有当有效时钟沿采样到己

变化的复位信号后,才对所有寄存器复位。同步复位的应用要点如下:

很多目标器件(如 FPGA 和 CPLD) 和 ASIC 库的触发器本身并不包含同步复位端口,这时同步

复位会被实现为如上图所示的结构。

优点

➢ 同步复位利于基于周期机制的仿真器进行仿真;

➢ 使用同步复位可以设计 100%的同步时序电路,有利于时序分析,其综合结果

的频率往往较高;

➢ 同步复位仅在时钟的有效沿生效,可以有效地避免因复位电路毛刺造成的亚

稳态和错误。

缺点

➢ 很多目标器件(如 FPGA 和 CPLD)和 ASIC 库的触发器本身并不包含同步复位

端口,使用同步复位会增加更多逻辑资源;

➢ 同步复位的最大问题在于必须保证复位信号的有效时间足够长,这样才能保

证所有触发器都能有效地复位。只有同步复位大于时钟最大周期,加上同步

信号穿过的组合逻辑路径延时,再加上时钟偏斜时,才能保证同步复位可靠、

彻底。

JonnyWONG

- 粉丝: 1

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0