EDA 技术实验讲义

(GW48 系列实验开发系统详细使用说明)

目 录

GW48 EDA 系统使用说明

GW48 教学实验系统原理与使用介绍

实验电路结构图

GW48EK EDA 系统

GWCNF 型 FPGA 掉电保护配置器应用

GW48-PK 系统 LCD 液晶屏使用方法

第一章 GW48 SOC/EDA 系统使用说明

第一节 GW48 教学实验系统原理与使用介绍

一、GW48 系统使用注意事项

a:闲置不用 GW48 EDA/SOC 系统时,关闭电源,拔下电源插头!!!

b:EDA 软件安装方法可参见光盘中相应目录中的中文 README.TXT;详细使用方法可参阅本书或《EDA

技术实用教程》、或《VHDL 实用教程》中的相关章节。

c:在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

d:换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。其它

接口都可带电插拔(当适配板上的 10 芯座处于左上角时,为正确位置)。

e:对工作电源为 5V 的 CPLD(如 1032E/1048C、95108 或 7128S 等)下载时。最好将系统的电路“模

式”切换到“ b”,以便使工作电压尽可能接近 5V。

g: GW48 详细使用方法可参见《EDA 技术实用教程》配套教学软件*.ppt。

h:主板左侧 3 个开关默认向下,但靠右的开关必须打向上(DLOAD),才能下载。

i:跳线座“SPS” 默认向下短路(PIO48);右侧开关默认向下(TO MCU)。

j:左下角拨码开关除第 4 档“DS8 使能”向下拨(8 数码管显示使能)外,其余皆默认向上拨。

二、GW48 系统主板结构与使用方法

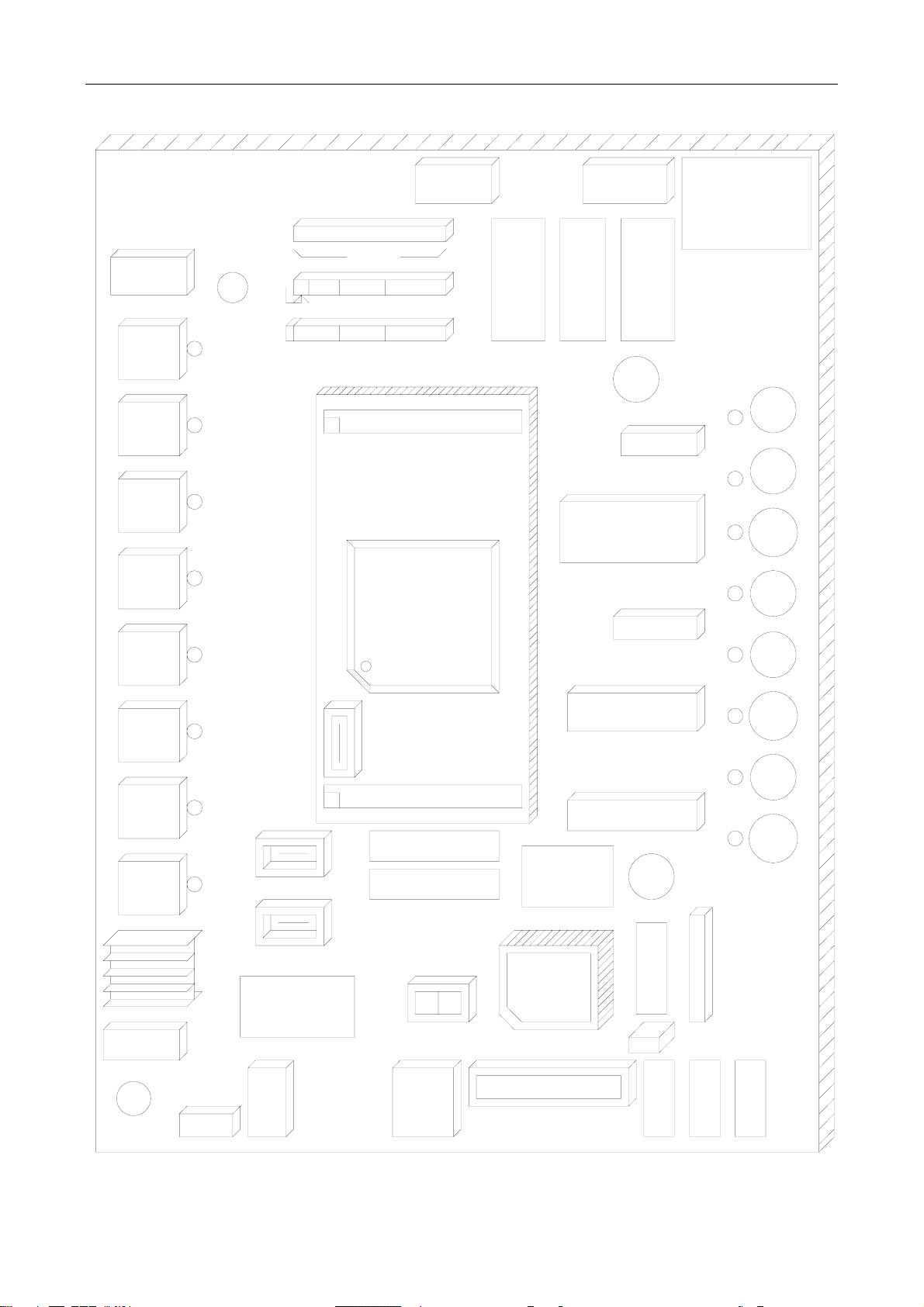

附图 1-1A 为 GW48-CK 型 EDA 实验

开发系统的主板结构图(GW48-GK/PK

型未画出,具体结构说明应该参考实物

主板),该系统的实验电路结构是可控

的。即可通过控制接口键 SW9,使之改

变连接方式以适应不同的实验需要。因

而,从物理结构上看,实验板的电路结

构是固定的,但其内部的信息流在主控

器的控制下,电路结构将发生变化。这

种“多任务重配置”设计方案的目的有

3 个:1.适应更多的实验与开发项目;

2. 适应更多的 PLD 公司的器件;3. 适

应更多的不同封装的 FPGA 和 CPLD 器

件。系统板面主要部件及其使用方法说

明如下(请参看相应的实验板板面和附

图 1-1A)。

以下是对 GW48 系统主板功能块的

注释,但请注意,有的功能块仅 GW48-GK 获 GW48-PK 系统存在:

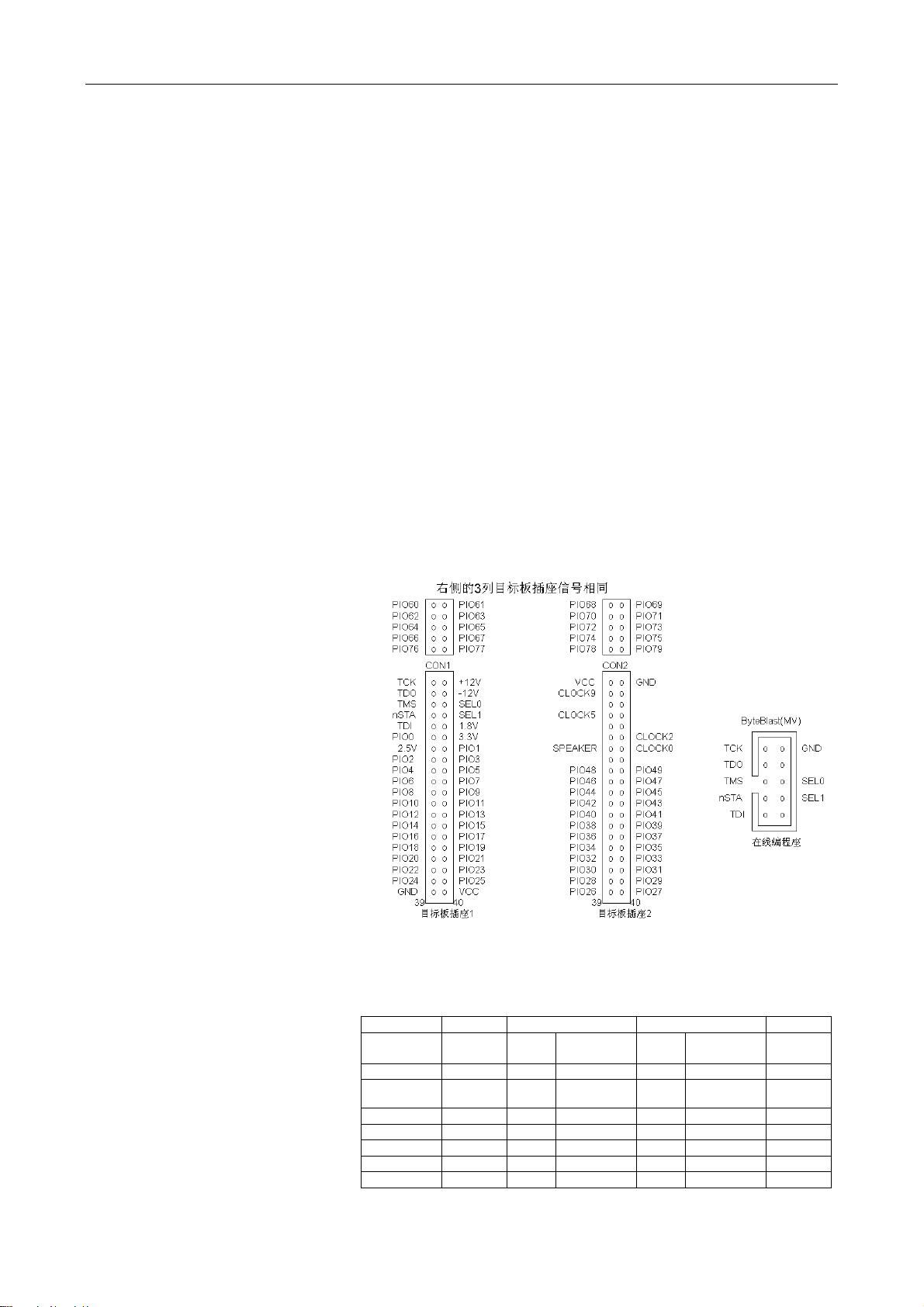

附图 1-1B、GW48-GK/PK 系统目标板插座引脚信号图

(1) SW9 :按动该键能使实

验板产生 12 种不同的实验电路结

构。这些结构如第二节的 13 张实

验电路结构图所示。例如选择了

“NO.3”图,须按动系统板上的

SW9 键,直至数码管 SWG9 显示“3”,

于是系统即进入了 NO.3 图所示的

实验电路结构。

附表 1-1 在线编程坐各引脚与不同 PLD 公司器件编程下载接口说明

PLD 公司 LATTICE ALTERA/ATMEL XILINX VANTIS

编程座

引脚

IspLSI CPLD FPGA CPLD FPGA CPLD

TCK (1) SCLK TCK DCLK TCK CCLK TCK

TDO (3) MODE

TDO

CONF_DONE TDO DONE TMS

TMS (5) ISPEN TMS nCONFIG TMS /PROGRAM ENABLE

nSTA (7) SDO nSTATUS TDO

TDI (9) SDI TDI DATA0 TDI DIN TDI

SEL0 GND VCC* VCC* GND GND VCC*

SEL1 GND VCC* VCC* VCC* VCC* GND

(2) B2 :这是一块插于主系统

板上的目标芯片适配座。对于不同

2

的目标芯片可配不同的适配座。可用的目标芯片包括目前

数模转换器件

模数转换器件

鼠标接口

PS/2接口

单片机接口器件

S1

在线下载接口

接口电路切换座

模块

配置/下载

在系统

电位器

VR1

显示控制器件2

显示控制器件1

检测电源

在线下载通讯接口

电路

接口

模拟接口

模式配置键

系统复位

键B

键A

5V ,+/-12V

3.3V, 2.5V

1.8V

电压源模块

SWG9

模式指示

CON1

B2

适配座

目标芯片

J3B

在线下载口

目标板插座1

目标板插座2 CON2

21

CPLD/FPGA

目标芯片

EDA实验开发

数码5 数码4 数码3 数码2

D5 D4 D3 D2

键8 键1

频率计

时钟频率选择

JP1A JP1B JP1C

中频组 高频组低频组

Clock0

UART接口

时钟发生电路

接口电路

视频接口电路

RS-232

B8

B4

B3

VGA

VGA

视频接口

RS-232

J8

C38

扬声器

50M晶振

ASIC

KONXIN

D/A信号输出

A/D信号输入

A/D信号输入

J2

AOUT

AIN1

AIN0

JP2

D9D10D11D12D16 D15 D14 D13

键2键3键4键7 键6 键5

ByteBlasterMV

ByteBlaster

散热器

数码8 数码7 数码6 数码1

FUSE

K1

电源开关

D8 D7 D6 D1

附图 1-1A

GW48-CK 实验开发系统的板面结构图

4

世界上最大的六家 FPGA/CPLD 厂商几乎所有 CPLD、FPGA 和所有 ispPAC 等模拟 EDA 器件 。第三节的

表中已列出多种芯片对系统板引脚的对应关系,以利在实验时经常查用。

(3) J3B/J3A:如果仅是作为教学实验之用,系统板上的目标芯片适配座无须拔下,但如果要进

行应用系统开发、产品开发、电子设计竞赛等开发实践活动,在系统板上完成初步仿真设计后,就有

必要将连有目标芯片的适配座拔下插在自己的应用系统上(如 GWDVP 板)进行调试测试。为了避免

由于需要更新设计程序和编程下载而反复插拔目标芯片适配座,GW48 系统设置了一对在线编程下载

接口座:J3A 和 J3B。此接口插座可适用于不同的 FPGA/CPLD(注意,1、此接口仅适用于 5V 工作

电源的 FPGA 和 CPLD;2、5V 工作电源必须由被下载系统提供)的配置和编程下载。 对于低压

FPGA/CPLD,(如 EP1K30/50/100、EPF10K30E 等,都是 2.5V 器件),下载接口座必须是另一座:

ByteBlasterMV。注意,对于 GW48-GK/PK,只有一个下载座:ByteBlasterMV,是通用的。

(4)混合工作电压使用:对于低压 FPGA/CPLD 目标器件,在 GW48 系统上的设计方法与使用方

法完全与 5V 器件一致,只是要对主板的跳线作一选择(对 GW48-GK/PK 系统不用跳线):

JVCC/VS2:跳线 JVCC(GW48—GK/PK 型标为“VS2”)对芯片 I/O 电压 3.3V(VCCIO)或 5V

(VCC)作选择,对 5V 器件,必须选“5.0V”。例如,若系统上插的目标器件是 EP1K30/50/100

或 EPF10K30E/50E 等,要求将主板上的跳线座“JVCC”短路帽插向“3.3V”一端;将跳线座“JV2”

短路帽插向“+2.5V”一端(如果是 5V 器件,跳线应插向“5.0V”)。

(5)并行下载口 :此接口通过下载线与微机的打印机口相连。来自 PC 机的下载控制信号和

CPLD/FPGA 的目标码将通过此口,完成对目标芯片的编程下载。编程电路模块能自动识别不同的

CPLD/FPGA 芯片,并作出相应的下载适配操作。

(6)键1~键8 :为实验信号控制键,此 8 个键受“多任务重配置”电路控制,它在每一张电路

图中的功能及其与主系统的连接方式随 SW9 的模式选择而变,使用中需参照第二节中的电路图。

(7)键 9~键 12 :实验信号控制键(仅 GW48—GK/PK 型含此键)此 4 个键不受“多任务重配置”

电路控制,使用方法参考“实验电路结构 NO.5”。

(8) 数码管 1~8/发光管 D1~D16 :也受“多任务重配置”电路控制,它们的连线形式也需参照

第二节的电路图。

(9) 数码管 9~14/发光管 D17~D22 :不受“多任务重配置”电路控制(仅 GW48—GK/PK 型含

此发光管),它们的连线形式和使用方法参考“实验电路结构 NO.5”。

(10)“时钟频率选择”P1A/JP1B/JP1C :为时钟频率选择模块。通过短路帽的不同接插方式,使

目标芯片获得不同的时钟频率信号。对于“CLOCK0”JP1C,同时只能插一个短路帽,以便选择输向

“CLOCK0”的一种频率:

信号频率范围: 1Hz – 50MHz(对 GW48-CK 系统)

信号频率范围: 0.5Hz – 50MHz(对 GW48-GK 系统)

信号频率范围: 0.5Hz – 100MHz(对 GW48-PK 系统),

由于 CLOCK0 可选的频率比较多,所以比较适合于目标芯片对信号频率或周期测量等设计项目的

信号输入端。JP1B 分三个频率源组,即如系统板所示的“高频组”、“中频组”和“低频组”。它们分

别对应三组时钟输入端。例如,将三个短路帽分别插于 JP1B 座的 2Hz、1024Hz 和 12MHz;而另三个短

路帽分别插于 JP1A 座的 CLOCK4、CLOCK7 和 CLOCK8,这时,输向目标芯片的三个引脚:CLOCK4、CLOCK7

和 CLOCK8 分别获得上述三个信号频率。需要特别注意的是,每一组频率源及其对应时钟输入端,分

别只能插一个短路帽。也就是说,通过 JP1A/B 的组合频率选择,最多只能提供三个时钟频率。

注意,对于 GW48-GK/PK 系统,时钟选择比较简单:每一频率组仅接一个频率输入口,如低频端

的 4 个频率通过短路帽,可选的时钟输入口仅为 CLOCK2,因此对于 GW48-GK/PK,总共只有 4 个时钟

可同时输入 FPGA:CLOCK0(Pin126)、CLOCK2(Pin54)、CLOCK5(Pin56)、CLOCK9(Pin126)。

(11)扬声器 S1:目标芯片的声讯输出,与目标芯片的“SPEAKER”端相接,即 PIO50。

通过此口

可以进行奏乐或了解信号的频率。

(12) PS/2 接口:通过此接口,可以将 PC 机的键盘和/或鼠标与 GW48 系统的目标芯片相连,从

而完成 PS/2 通信与控制方面的接口实验,GW48-GK/PK 含另一 PS/2 接口,参见实验电路结构 NO.5。

(13)VGA 视频接口:通过它可完成目标芯片对 VGA 显示器的控制。

(14) 单片机接口器件:它与目标板的连接方式也已标于主系统板上:连接方式可参见附图 2-13。

5

注意 1,对于 GW48-GK/PK 系统,实验板左侧有一开关,向上拨,将 RS232 通信口直接与 FPGA 的

PIO31 和 PIO30 相接;向下拨则与 89C51 单片机的 P30 和 P31 端口相接。于是通过此开关可以进行不

同的通信实验,详细连接方式可参见附图 2-13。平时此开关向下打,不要影响 FPGA 的工作。

注意 2,由附图 2-13 可知,单片机 89C51 的 P3 和 P1 口是与 FPGA 的 PIO66-PIO79 相接的,而这

些端口又与 6 数码管扫描显示电路连在一起的,所以当要进行 6 数码管扫描显示实验时,必须拔去右

侧的单片机,并安实验电路结构 NO.5,将拨码开关 3,拨为使能,这时 LCD 停止工作。

(15) RS-232 串行通讯接口:此接口电路是为单片机与 PC 机通讯准备的,由此可以使 PC 机、单

片机、FPGA/CPLD 三者实现双向通信。当目标板上 FPGA/CPLD 器件需要直接与 PC 机进行串行通讯时,

可参见附图 2-13,和实验电路结构图 NO.5,将实验板右侧的开关向上打“TO FPGA”,从而使目标芯

片的 PIO31 和 PIO30 与 RS232 口相接,即使 RS232 的通信接口直接与目标器件 FPGA 的 PIO30/PIO31

相接。而当需要使 PC 机的 RS232 串行接口与单片机的 P3.0 和 P3.1 口相接时,则应将开关向下打“TO

MCU”既可(平时不用时也应保持在个位置)。

(16) “AOUT” D/A 转换 :利用此电路模块(实验板左下侧),可以完成 FPGA/CPLD 目标芯片

与 D/A 转换器的接口实验或相应的开发。它们之间的连接方式可参阅“实验电路结构 NO.5” :D/A

的模拟信号的输出接口是“AOUT”,示波器可挂接左下角的两个连接端。当使能拨码开关 8:“滤波 1”

时,D/A 的模拟输出将获得不同程度的滤波效果 。

注意,进行 D/A 接口实验时,需打开左侧第 2 个开关,获得+/-12 伏电源,实验结束后关上此电源。

(17) “AIN0”/“AIN1”:外界模拟信号可以分别通过系统板左下侧的两个输入端“AIN0”和“AIN1”

进入 A/D 转换器 ADC0809 的输入通道 IN0 和 IN1,ADC0809 与目标芯片直接相连。通过适当设计,目

标芯片可以完成对 ADC0809 的工作方式确定、输入端口选择、数据采集与处理等所有控制工作,并可

通过系统板提供的译码显示电路,将测得的结果显示出来。此项实验首先需参阅第二节的“实验电路

结构 NO.5”有关 0809 与目标芯片的接口方式,同时了解系统板上的接插方法以及有关 0809 工作时序

和引脚信号功能方面的资料。

注意:不用 0809 时,需将左下角的拨码开关的“A/D 使能”和“转换结束”打为禁止:向上拨,

以避免与其他电路冲突。

ADC0809 A/D 转换实验接插方法(如实验电路结构 NO.5 图所示):

1. 左下角拨码开关的“A/D 使能”和“转换结束”打为使能:向下拨,即将 ENABLE(9)与 PIO35

相接;若向上拨则禁止,即则使 ENABLE(9)Å0,表示禁止 0809 工作,使它的所有输出端为高阻态。

2.左下角拨码开关的“转换结束”使能,则使 EOC(7)ÅPIO36,由此可使目标芯片对 ADC0809 的

转换状态进行测控。

(18) VR1/“AIN1”:VR1 电位器,通过它可以产生 0V~+5V 幅度可调的电压。其输入口是 0809

的 IN1(与外接口

AIN1 相连,但当 AIN1 插入外输入插头时,VR1 将与 IN1 自动断开)。若利用 VR1 产

生被测电压,则需使 0809 的第 25 脚置高电平,即选择 IN1 通道,参考“实验电路结构 NO.5”。

(19) AIN0 的特殊用法 :系统板上设置了一个比较器电路,主要以 LM311 组成。若与 D/A 电路

相结合,可以将目标器件设计成逐次比较型 A/D 变换器的控制器件参考“实验电路结构 NO.5”。

(20) 系统复位键:此键是系统板上负责监控的微处理器的复位控制键,同时也与接口单片机的

复位端相连。因此兼作单片机的复位键。

(21) 下载控制开关 :在系统板的左侧第 3 个开关。当需要对实验板上的目标芯片下载时必须将

开关向上打(即“DLOAD”);而当向下打(LOCK)时,将关闭下载口,这时可以将下载并行线拔下而

作它用(这时已经下载进 FPGA 的文件不会由于下载口线的电平变动而丢失);例如拔下的 25 芯下载

线可以与 GWAK30+适配板上的并行接口相接,以完成类似逻辑分析仪方面的实验。

(22)跳线座 SPS :短接“T_F”可以使用在系统频率计。频率输入端在主板右侧标有“频率计”

处。模式选择为“A”。短接“PIO48”时,信号 PIO48 可用,如实验电路结构图 NO.1 中的 PIO48。平

时应该短路“PIO48”

(23) 目标芯片万能适配座 CON1/2 :在目标板的下方有两条 80 个插针插座(GW48-CK 系统),

其连接信号如附图 1-1B 所示,此图为用户对此实验开发系统作二次开发提供了条件。此二座的位置

设置方式和各端口的信号定义方式与综合电子设计竞赛开发板 GWDVP-B 完全兼容!!!

对于 GW48-GK/PK 系统,此适配座在原来的基础上增加了 20 个插针,功能大为增强。增加的 20

6

- 1

- 2

- 3

前往页