一、课题要求:

(1)技术要求:1、掌握多功能数字钟的工作原理.

2、应用 EDA 技术,VHDL 语言编写程序。

3、层次化设计,设计原理框图.

4,、硬件设计及排版。

(2)功能要求:1、基本功能:能进行正常的时、分、秒计时功能,分别由 6

个数码管显示 24 小时、60分钟、60 秒的计数器显示。

2、 扩展功能:(1)能够利用按键实现“校时”“校分"

“清零”功能。

(2)能利用扬声器做整点报时,整点前

五秒短声,整点长声.

(3)本人工作:负责软件部分,,编写各部分模块的 VHDL 程序,并且锁定引脚,

将程序下载到芯片中。

二、设计方案:

原理框图:

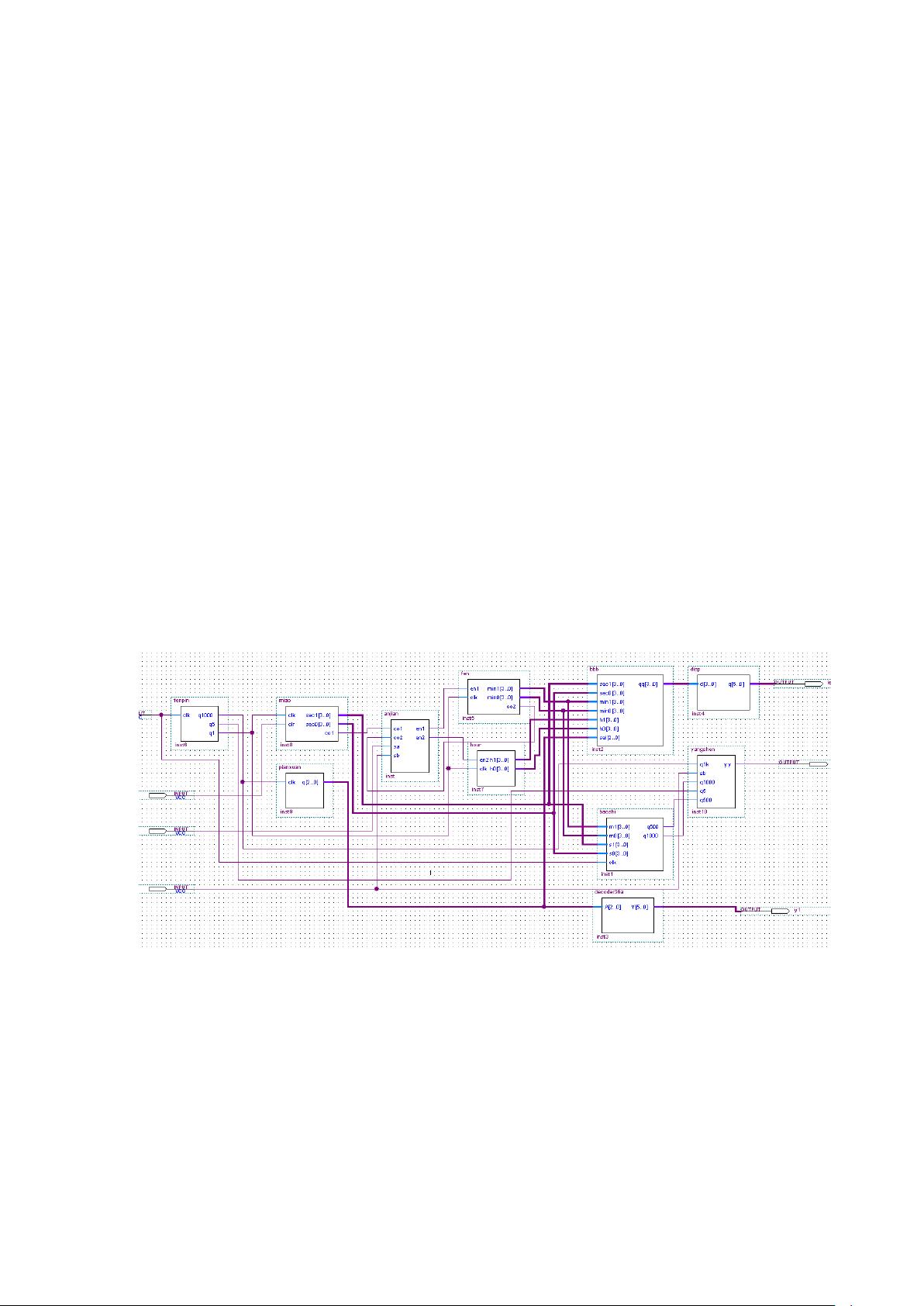

数字钟原理框图

一共有 11 个小模块:分频,片选,按键,小时,分,秒,显示模块,七段显示译码器,报

时,扬声,36译码器。

左边第一个是时钟信号输入端,50Mhz 到分频模块。第二个为清零按键,第三个为校分按

键,第四个为校时按键。

右边第一个为七段显示译码器输出端,第二个为扬声器输出端,第三个为 6 个数码管输出

端。

中间模块为数字钟的核心,有计时,报时,校时功能。