ECP5 PCI Express Board

Evaluation Board User Guide

FPGA-EB-02037-1.1

June 2021

ECP5 PCI Express Board

Evaluation Board User Guide

© 2014-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2 FPGA-EB-02037-1.1

Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its

products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely

with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been

subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the

same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice’s

product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this

document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any

products at any time without notice.

ECP5 PCI Express Board

Evaluation Board User Guide

© 2014-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02037-1.1 3

Contents

Acronyms in This Document ................................................................................................................................................. 5

1. Introduction .................................................................................................................................................................. 6

2. Features ........................................................................................................................................................................ 7

3. ECP5 Device .................................................................................................................................................................. 8

4. Applying Power to the Board ........................................................................................................................................ 8

5. Programming/FPGA Configuration ............................................................................................................................... 9

5.1. Diamond Programmer Requirements ................................................................................................................. 9

5.2. Board Programming ............................................................................................................................................ 9

5.3. PROGRAMN and GSRN ...................................................................................................................................... 10

5.4. Programming Serial SPI Flash Memory ............................................................................................................. 10

5.5. On-Board Clock Capabilities .............................................................................................................................. 12

5.6. SerDes ............................................................................................................................................................... 12

6. FPGA Test Pins ............................................................................................................................................................ 13

6.1. General Purpose DIP Switches .......................................................................................................................... 13

6.2. General Purpose LEDs ....................................................................................................................................... 14

6.3. General Purpose LEDs ....................................................................................................................................... 14

6.4. Ethernet Interfaces ........................................................................................................................................... 15

6.5. Power Measurements ....................................................................................................................................... 16

6.6. PMOD ................................................................................................................................................................ 16

6.7. Expansion Headers/Connectors ........................................................................................................................ 17

7. Ordering Information ................................................................................................................................................. 19

Technical Support Assistance .............................................................................................................................................. 20

Appendix A. Bill of Materials .............................................................................................................................................. 21

Appendix B. Schematic Diagrams ....................................................................................................................................... 32

Revision History ................................................................................................................................................................... 54

ECP5 PCI Express Board

Evaluation Board User Guide

© 2014-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4 FPGA-EB-02037-1.1

Figures

Figure 1.1. ECP5 PCI Express Board, Top Side ....................................................................................................................... 6

Figure 4.1. Power Distribution Scheme ................................................................................................................................ 8

Figure 5.1. PCI Express Board Configuration/Programming Mux Selection ......................................................................... 9

Figure 5.2. ECP5 Configuration Pin (CFG Pins) .................................................................................................................... 10

Figure 5.3. ECP5 Status LEDs and Push-button Controls .................................................................................................... 10

Figure 5.4. Device Information Dialog Screen .................................................................................................................... 11

Figure 5.5. Select Device Dialog Box ................................................................................................................................... 11

Figure 6.1. ECP5 PCI Express Bard and LEDs and Switches ................................................................................................. 13

Figure 6.2. PMOD Connector and Switches ........................................................................................................................ 16

Figure B.1. Board Block Diagram ........................................................................................................................................ 32

Figure B.2. ECP5 Banks ........................................................................................................................................................ 33

Figure B.3. Mechanical ........................................................................................................................................................ 34

Figure B.4. Power Supplies ................................................................................................................................................. 35

Figure B.5. ECP Power ......................................................................................................................................................... 36

Figure B.6. ECP5 GNDs, XRES, Mountings and Logos .......................................................................................................... 37

Figure B.7. USB to FTDI ....................................................................................................................................................... 38

Figure B.8. MachXO2 Configuration Mux ........................................................................................................................... 39

Figure B.9. ECP5 Config ....................................................................................................................................................... 40

Figure B.10. LEDs and Switches .......................................................................................................................................... 41

Figure B.11. Clock Generation ............................................................................................................................................ 42

Figure B.12. Card 1 .............................................................................................................................................................. 43

Figure B.13. Card 2 .............................................................................................................................................................. 44

Figure B.14. ECP5 Quad C to D ............................................................................................................................................ 45

Figure B.15. PCIe 4-Lane Connector ................................................................................................................................... 46

Figure B.16. RJ45 ................................................................................................................................................................. 47

Figure B.17. LPDDR3 ........................................................................................................................................................... 48

Figure B.18. ECP5 Bank 0, Bank 1, and Bank 4 .................................................................................................................... 49

Figure B.19. ECP5 Bank 2 to Bank 3 .................................................................................................................................... 50

Figure B.20. ECP5 Bank 2 to Bank 3 #1 Termination ........................................................................................................... 51

Figure B.21. ECP5 Bank 2 to Bank 3 #2 Termination ........................................................................................................... 52

Figure B.22. ECP5 Bank 6 to Bank 7 .................................................................................................................................... 53

Tables

Table 4.1. Board Power Supply Fuses

*

.................................................................................................................................. 8

Table 5.1. JTAG Chain Select ................................................................................................................................................. 9

Table 5.2. Clock Sources ..................................................................................................................................................... 12

Table 6.1. FPGA Ball to DIP Switch Position ........................................................................................................................ 13

Table 6.2. LED Definitions ................................................................................................................................................... 14

Table 6.3. DDR3 Memory Controller Interconnections ...................................................................................................... 14

Table 6.4. PHY Status Indicators ......................................................................................................................................... 15

Table 6.5. FPGA GPIO to RGMII Interfaces ......................................................................................................................... 15

Table 6.6. ECP5 Power Measurements ............................................................................................................................... 16

Table 6.7. Expansion Connections ...................................................................................................................................... 17

Table 7.1. Ordering Information ......................................................................................................................................... 19

ECP5 PCI Express Board

Evaluation Board User Guide

© 2014-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02037-1.1 5

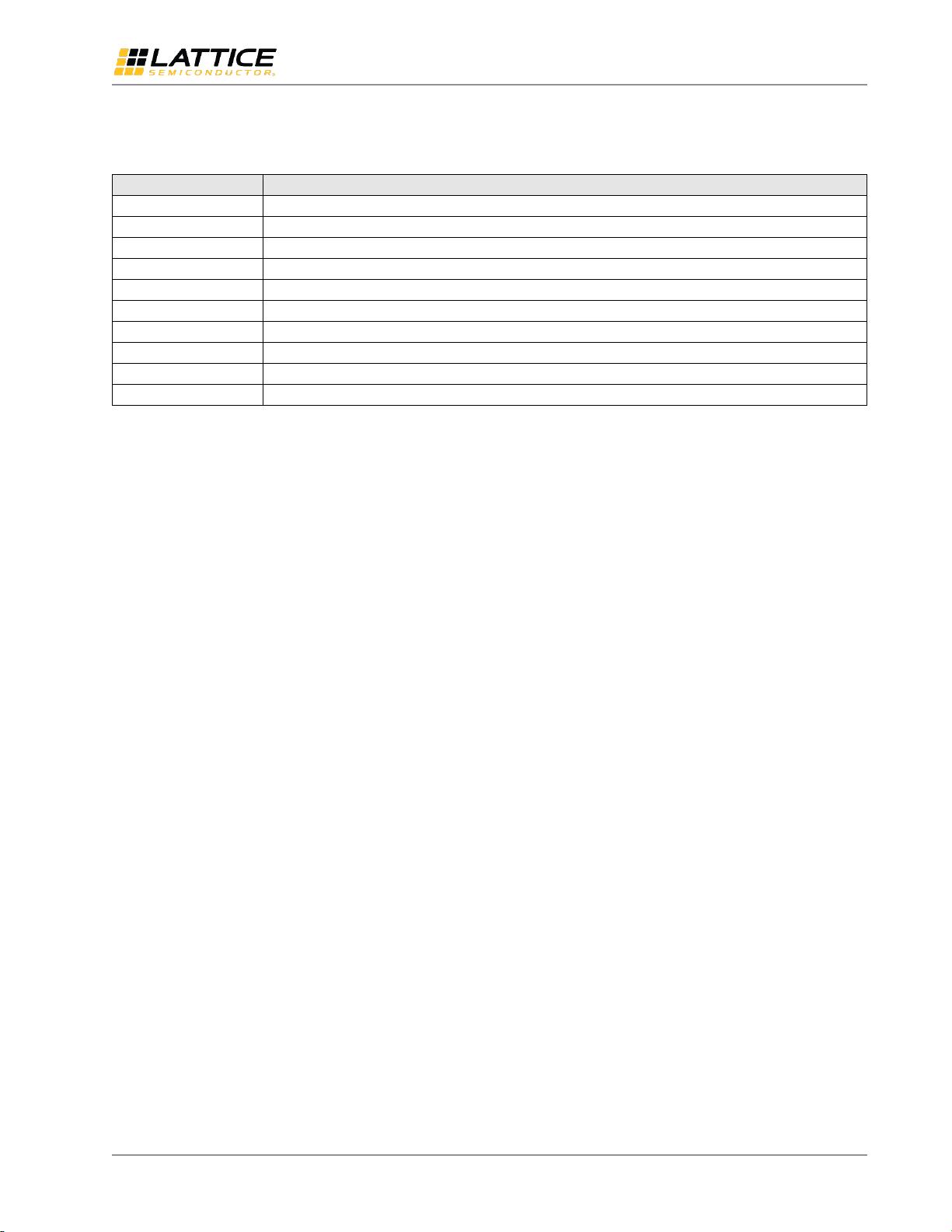

Acronyms in This Document

A list of acronyms used in this document.

Acronym

Definition

DIP

Dual In-line Package

FIFO

First-In, First-Out

FPGA

Field-Programmable Gate Array

LED

Light Emitting Diode

PCB

Printed Circuit Board

PCIe

Peripheral Component Interconnect Express; PCI Express

RoHS

Restriction of Hazardous Substances Directive

SerDes

Serializer/Deserializer

SPI

Serial Peripheral Interface

USB

Universal Serial Bus