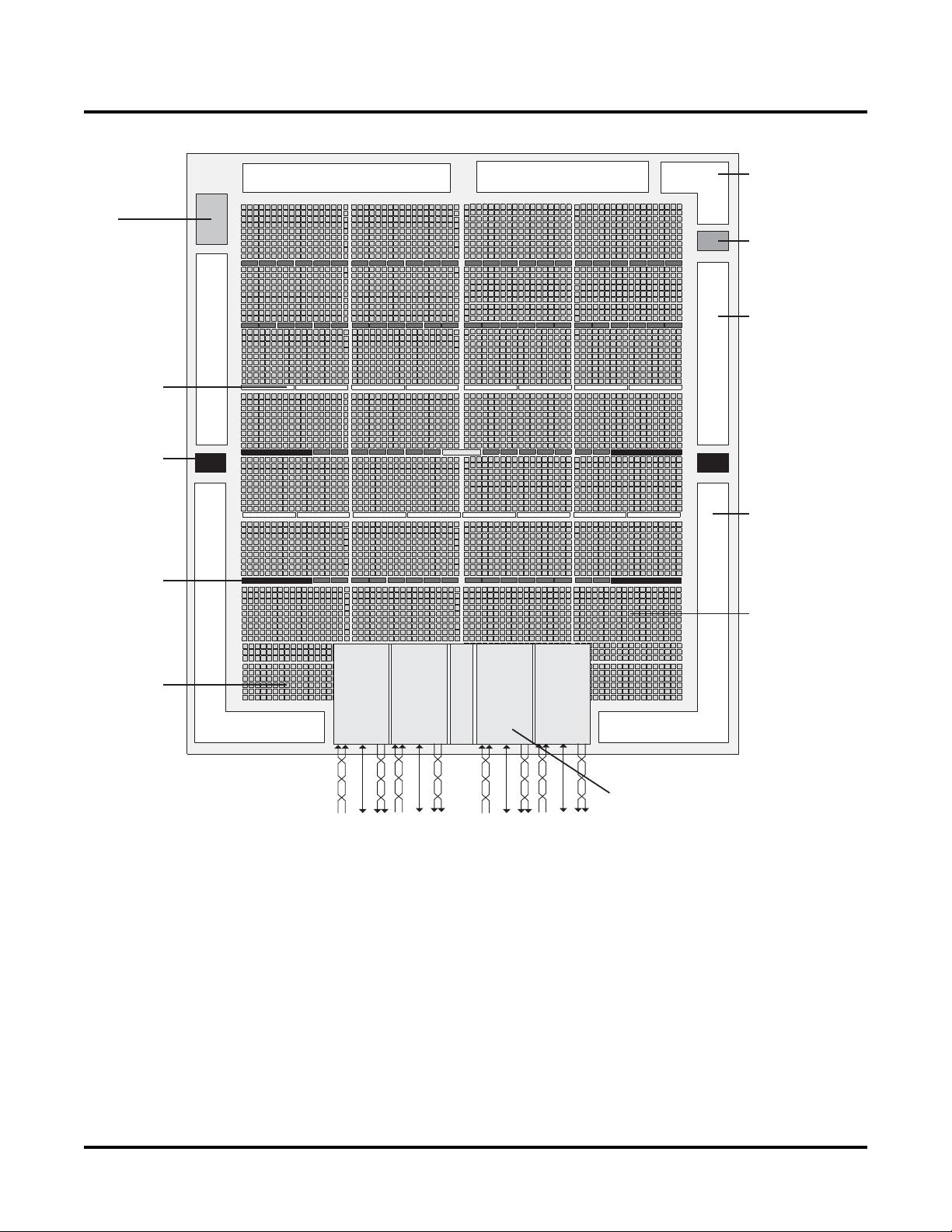

莱迪斯ECP3器件系列数据手册涵盖了关于该系列FPGA芯片的详细技术规格和性能参数。根据手册提供的信息,我们可以了解到莱迪斯ECP3系列FPGA具备的一些关键技术特点和功能。 莱迪斯ECP3系列FPGA具有较高的逻辑密度,提供了17K到149K的查找表(LUTs)数量,这使得该系列FPGA能够满足对系统集成度要求越来越高的应用需求。此外,ECP3系列提供了116到586个可配置的I/O引脚数量,为设计人员提供了灵活的接口配置选项。 ECP3系列FPGA的一个突出特点是集成了串行器/解串器(SERDES),支持高达3.2Gbps的速率,适用于多种数据传输协议,包括PCI Express、SONET/SDH、以太网(1GbE、SGMII、XAUI)、CPRI、SMPTE3G和Serial RapidIO等。每个设备最多支持16个通道,这为高速数据传输提供了强大的支持。 在数字信号处理方面,ECP3系列使用了sysDSP™技术,通过全可级联的切片架构实现高性能的乘加运算。每一片切片支持半36x36、两个18x18或四个9x9乘法器,还包括更高级的18x36乘法器和18x18乘累加器(MAC)操作。这些特点为需要进行复杂算法运算的应用提供了高效的数据处理能力。 在存储资源方面,ECP3系列FPGA集成了高达6.85Mbit的sysMEM™嵌入式块RAM(EBR)和36K到303K位的分布式RAM,能够满足不同应用对存储需求的多样性。 时钟管理方面,ECP3系列FPGA内建了sysCLOCK技术,包括两个延迟锁环(DLLs)和最多十个相位锁定环(PLLs)。这些硬件时钟管理单元能够提供灵活的时钟方案,支持高速时钟域之间的转换。 为了支持源同步I/O,ECP3系列FPGA提供了专用的读写均衡功能、专用的齿轮逻辑,并支持多种源同步标准,如ADC/DAC、7:1LVDS、XGMII等。同时,该系列FPGA还支持高速ADC/DAC设备,以及支持DDR/DDR2/DDR3内存的专用读写均衡功能和可选的符号间干扰(ISI)修正。 在I/O支持方面,ECP3系列FPGA提供了可编程的sysI/O™缓冲器,支持广泛的接口标准,包括LVTTL、LVCMOS、SSTL、HSTL、PCI、LVDS、Bus-LVDS等。这些I/O缓冲器还支持片上终端和可选的输入均衡滤波器,为不同的接口标准提供了优化的支持。 莱迪斯ECP3系列FPGA提供了多种封装选项,包括328csBGA(10x10mm)、256ftBGA(17x17mm)、484fpBGA(23x23mm)、672fpBGA(27x27mm)和1156fpBGA(35x35mm)。这些封装提供了不同数量的SERDES通道和I/O组合,以适应不同应用的特定需求。 莱迪斯ECP3系列FPGA提供了丰富的功能和特性,使其成为设计高性能、低功耗系统时的理想选择。这些FPGA特别适用于通信、计算和工业自动化等领域的应用。

剩余140页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功