运算器实验_计算机组成原理_实验报告.docx

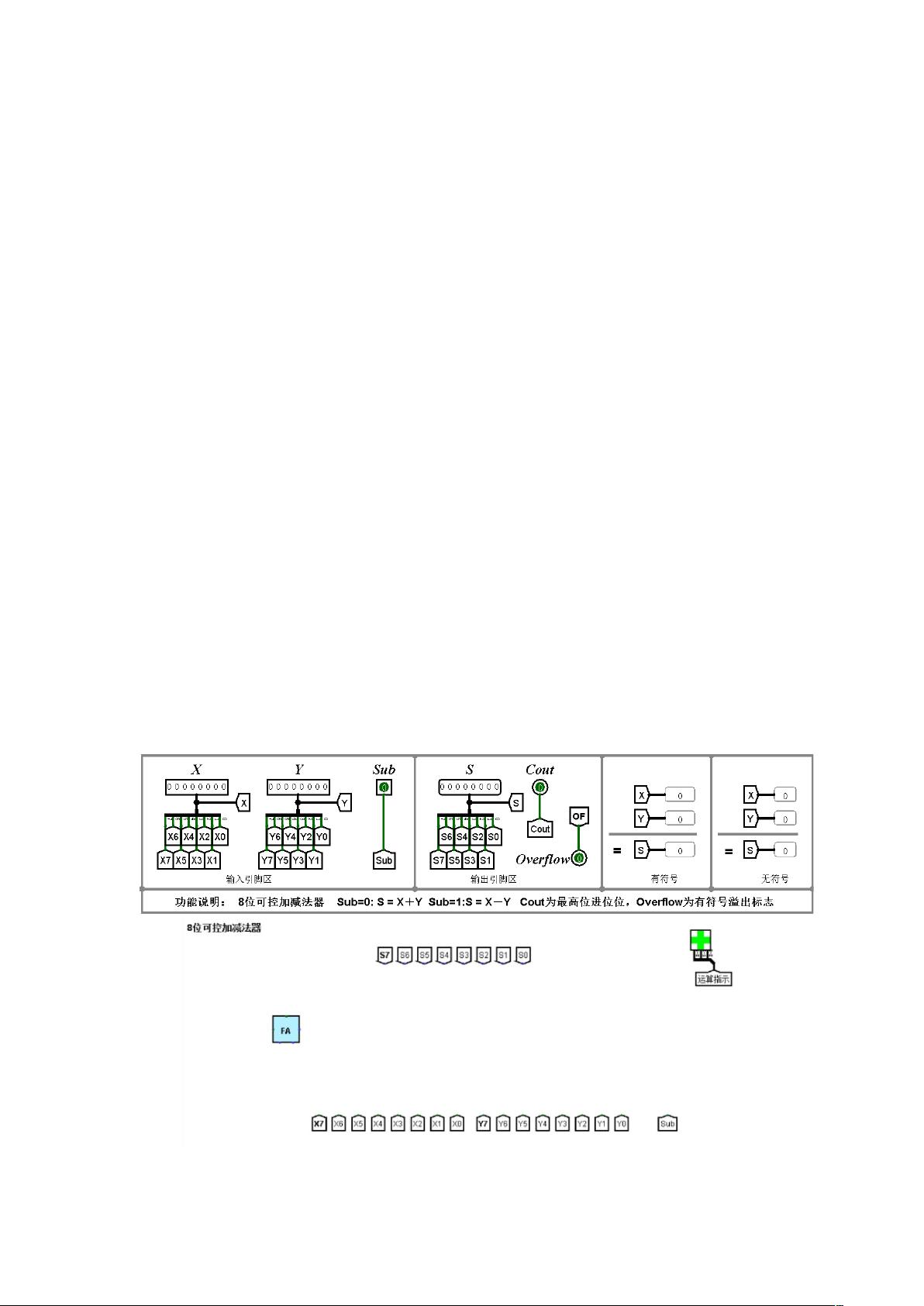

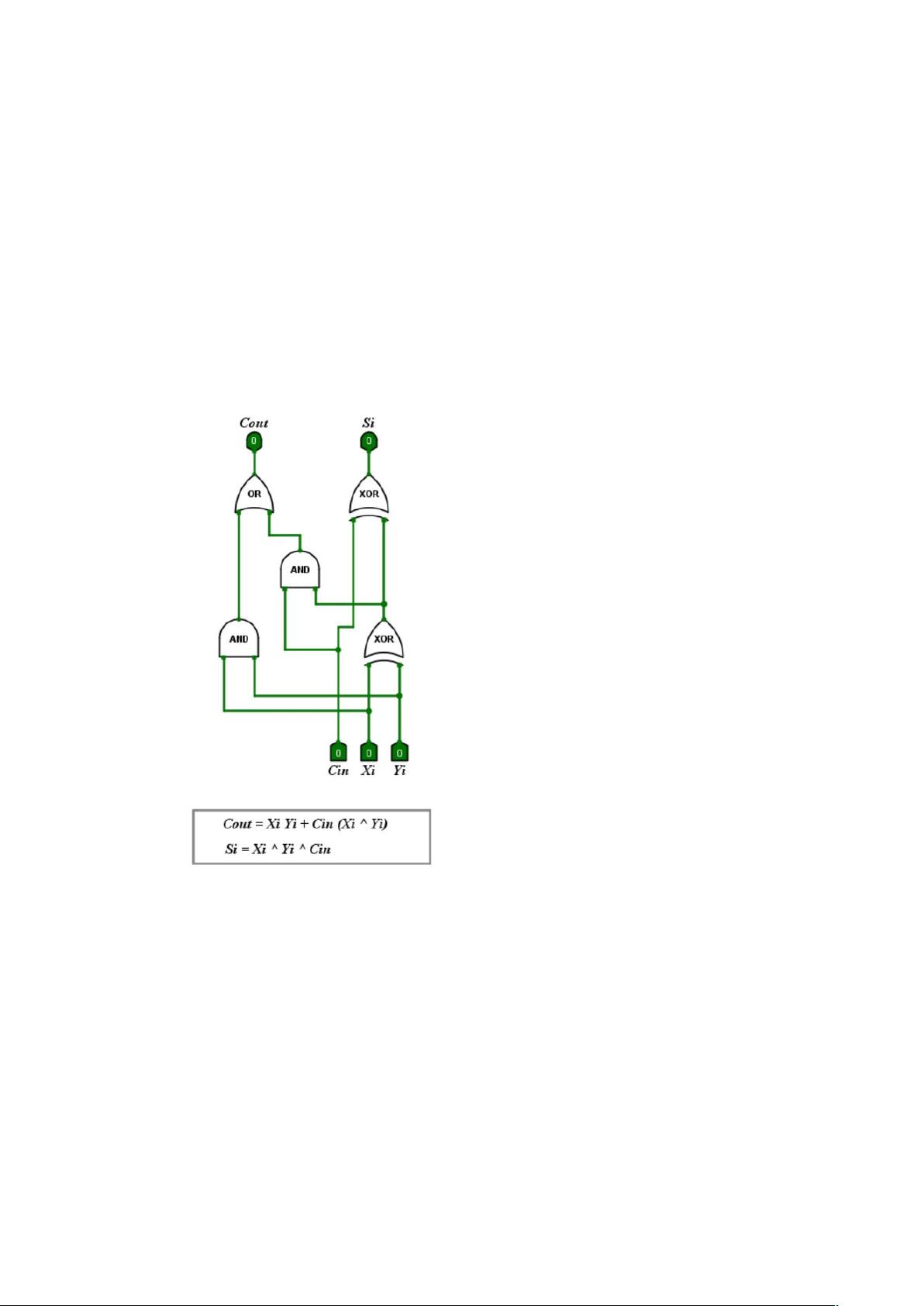

在现代计算机科学领域中,运算器作为计算机硬件系统的核心部件,主要负责执行各种算术和逻辑操作。在计算机组成原理的教学过程中,了解并掌握运算器的设计与实现原理对于学生深入理解计算机内部工作机制至关重要。本实验报告通过对8位可控加减法器、4位快速加法器以及16位快速加法器的设计与实现进行详细探讨,旨在加深学生对相关概念的理解,并在实践中提升动手能力。 ### 8位可控加减法器 8位可控加减法器的核心功能是根据外部控制信号的不同,执行加法或减法运算。该加减法器通过8个全加器串联构成,每个全加器处理二进制数的一位,并计算相应的进位。全加器的构成基于两个二进制数位以及一个进位输入,输出为和以及进位信号。 当控制信号Sub为0时,加减法器执行加法操作,将输入的X和Y进行相加,输出和S和进位Cout。当Sub为1时,执行减法操作,实际上是将X与Y的二进制补码相加(即X加上Y的反码后加1),同样得到和S和进位Cout。此外,为了检测有符号运算的溢出情况,设计中还包含了溢出位OF,用于指示运算结果是否超出了可表示的范围。 ### 4位快速加法器 4位快速加法器的核心在于其采用了先行进位技术,显著提升了加法运算的速度。该加法器主要由一个4位先行进位电路和四个全加器构成,其中CLAA74182芯片负责并行计算进位值。CLAA74182芯片提供的G(进位生成)和P(进位传递)函数结合进位输入Cin,能快速生成和数S以及进位输出Cout。 通过预先计算和数的进位值,4位快速加法器有效减少了在进行连续加法运算时的进位延迟,使得加法运算的执行速度得到大幅提升。这一设计在提高运算效率的同时,还降低了电路的复杂性,是计算机硬件设计中优化算术运算速度的有效手段。 ### 16位快速加法器 16位快速加法器是4位快速加法器的扩展版本,它通过并行处理四个4位快速加法器来实现16位数据的快速加法。在设计上,它将每4位数据作为一个单元,分别进行加法运算,然后通过CLAA74182芯片计算全局进位,以实现16位数据的完整加法运算。 这种设计的关键在于合理地组织和组合各个4位加法单元的局部进位,以减少整体计算时间。通过这种方式,16位快速加法器能够在保证运算速度的同时,处理更大的数据量,满足更多实际应用的需求。 ### 实验过程与总结 在实验过程中,学生首先通过理论学习理解了各种加法器的工作原理,随后进入设计和搭建电路阶段。在这一阶段中,学生需要精心设计电路的连接方式,并在实际操作中进行调试,以确保电路能够正确地执行预期的运算。在电路搭建和调试完成后,学生还需进行一系列的测试,以验证加法器的正确性和效率。 通过这一系列的实验操作,学生不仅加深了对计算机组成原理中算术运算硬件实现的理解,还锻炼了他们的动手实践能力和问题解决能力。这些实验为学生未来在计算机系统设计及硬件优化方面的学习和工作奠定了坚实的基础。 ### 结语 本报告详细介绍了8位可控加减法器、4位快速加法器与16位快速加法器的设计与实现过程。通过这三个实验项目,学生能够全面掌握计算机组成原理中关于二进制运算、进位机制以及电路设计的知识点。这些知识与技能对于计算机科学与工程领域的学生来说是极为重要的,因为它们是理解计算机工作原理和设计高效计算机系统不可或缺的部分。通过实践操作和实验验证,学生对计算机硬件系统本质的理解将更加深入,为他们成为未来计算机科学的探索者打下了坚实的基础。

剩余10页未读,继续阅读

- 粉丝: 3w+

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功