共

140

页文档名称 大规模逻辑设计指导书

机密

1.0

密级产品版本文档编号

研究管理部文档中心

大规模逻辑设计指导书

第一篇 方法论

(仅供内部使用)

yyyy/mm/dd

日期批

准

人

2000/03/18

日期审

核

人

2000/03/17

日期文

档

作

者

版权所有

不得复制

修订记录

初稿完成1.002000/03/17

作者描述修订版本日期

绝密

请输入文档编号

2001-8-28 版权所有 侵权必究 第2页 共142页

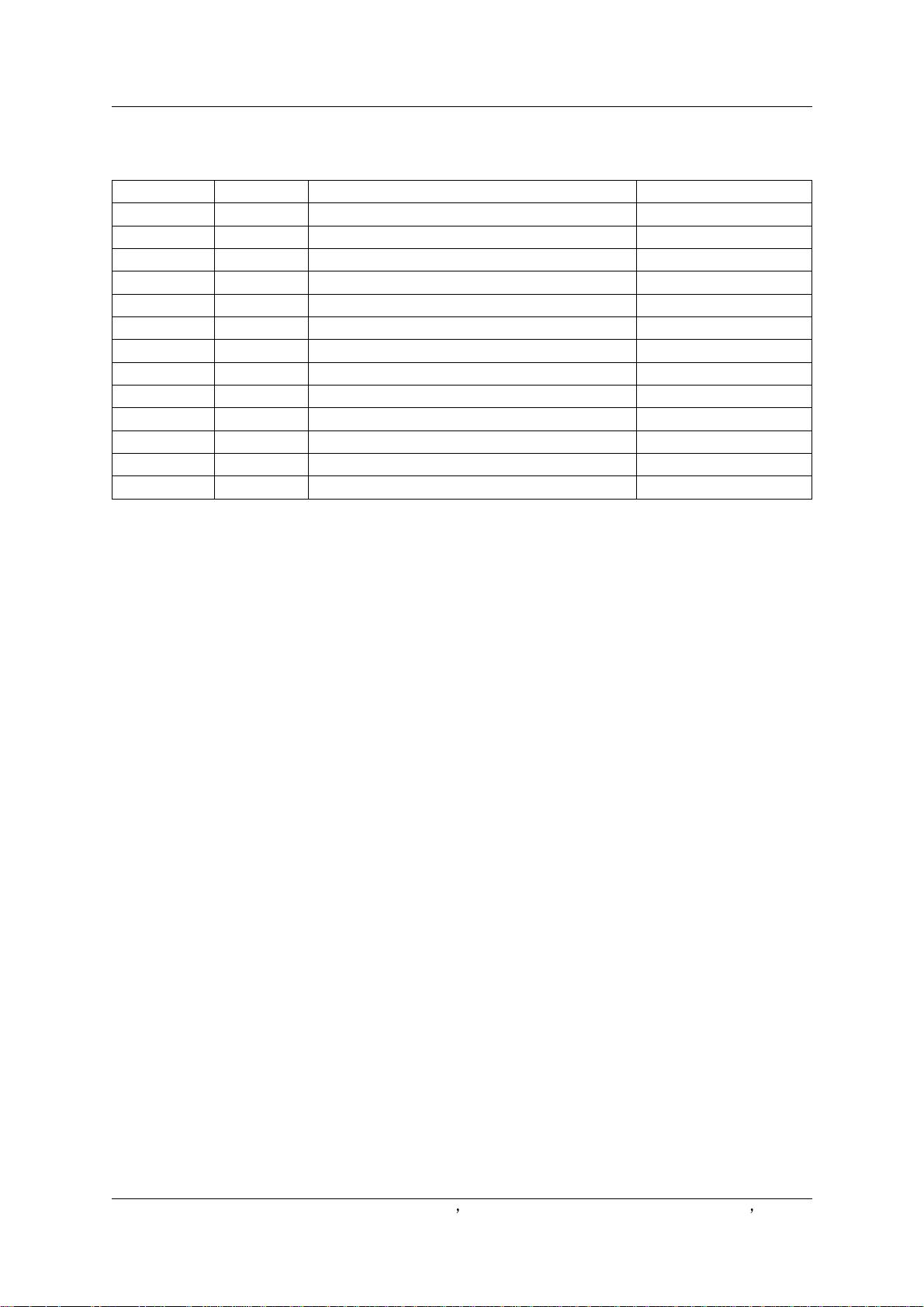

目 录

375.2代码编写中容易出现的问题 .............................................

365.1.12FSM ...........................................................

365.1.11Comments .......................................................

365.1.10Macros ..........................................................

355.1.9Combinatorial Vs Sequential Logic ......................................

345.1.8Assignment .......................................................

335.1.7Writing functions ...................................................

335.1.6case 语句 .........................................................

325.1.5IF 语句 ..........................................................

315.1.4Expressions .......................................................

315.1.3Net and Register ....................................................

295.1.2Modules .........................................................

28

5.1.1选择有意义的信号和变量名

对设计是十分重要的 命名包含信号或变

量诸如出处

有效状态等基本含义 下面给出一些命名的规则 ..................

285.1Verilog 编码风格 ......................................................

28

5规范内容

..............................................................

28

4引用标准和参考资料

.....................................................

28

3定义

..................................................................

28

2范围

..................................................................

28

1目的

..................................................................

28

第二章

VERILOG语言编写规范

...............................................

268.5 参数化元件实例 ......................................................

258.4 程序包书写实例 ......................................................

248.3 函数书写实例 .......................................................

228.2 VHDL 编写范例 ......................................................

228.1 VHDL保留字 ........................................................

22

8附录

..................................................................

217.5 多赋值语句案例

三态总线 .............................................

207.4 避免使用Latch .......................................................

207.3 考虑综合的执行时间 ..................................................

207.2组合逻辑描述的多种方式 ...............................................

197.1 资源共享问题 .......................................................

19

7 代码编写中容易出现的问题

................................................

18

6代码模块划分

...........................................................

185.1.13 TAB键间隔 ......................................................

185.1.12Comments .......................................................

185.1.11 FSM

有限状态机 ...............................................

185.1.10package .........................................................

175.1.9 类属( generics) ....................................................

175.1.8 procedure ........................................................

165.1.7 function .........................................................

165.1.6 运算符(operator) ...................................................

125.1.5 语句 ............................................................

105.1.4实体 ............................................................

95.1.3 信号和变量 .......................................................

95.1.2数据对象和类型 ....................................................

85.1.1标识符 Identifiers)命名习惯 ...........................................

75.1 VHDL编码风格 .......................................................

7

5规范内容

...............................................................

7

4引用标准和参考资料

......................................................

7

3定义

...................................................................

72范围 ...................................................................

7

1目的

...................................................................

7

第一章 VHDL语言编写规范

..................................................

绝密

请输入文档编号

2001-8-28 版权所有 侵权必究 第3页 共142页

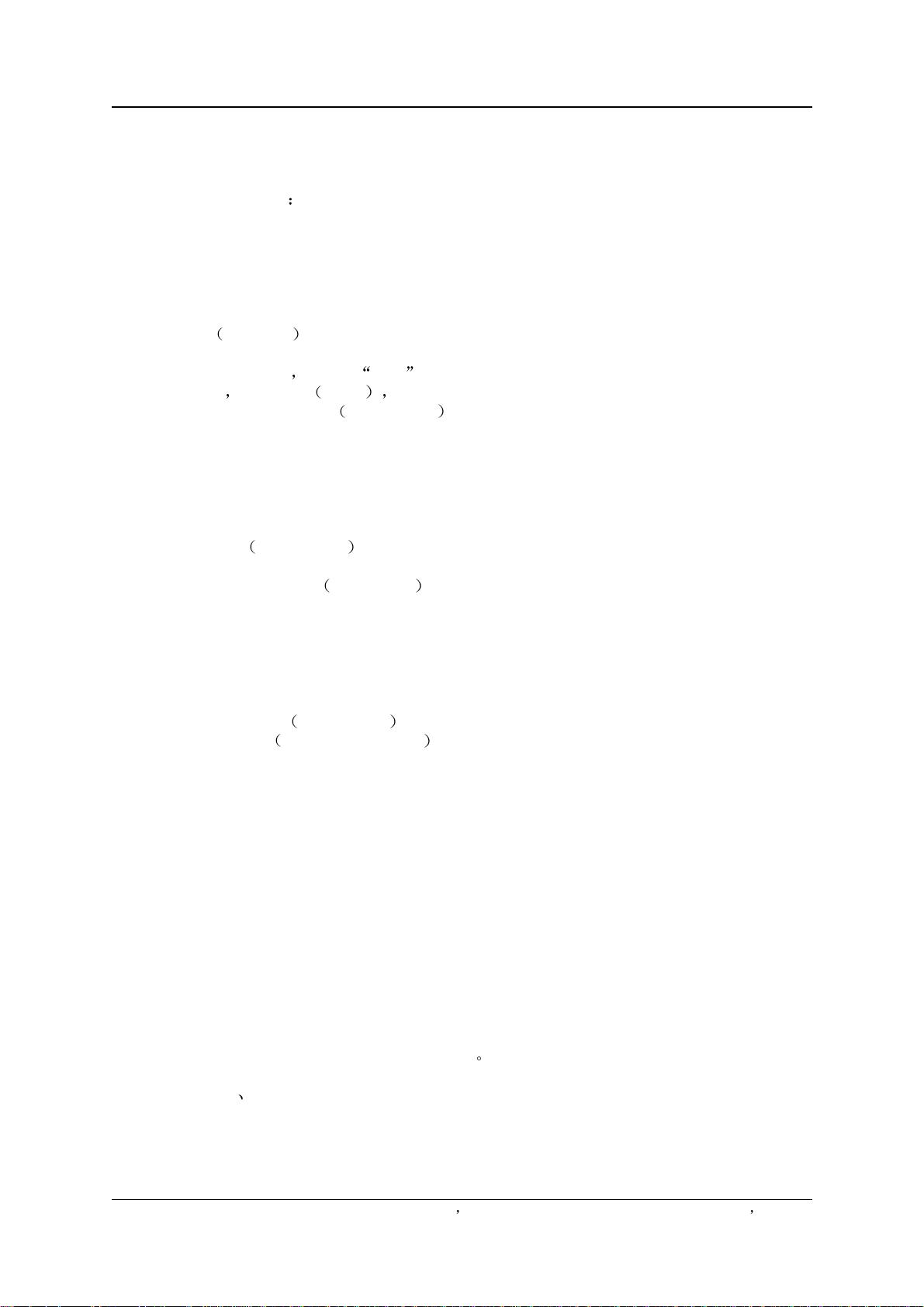

894.1合理选择加法电路 ....................................................

89

4设计技巧

..............................................................

883.10时钟电路设计 .......................................................

873.9异步复位电路设计 ....................................................

863.8三态电路设计 ........................................................

853.7合理使用内部RAM ....................................................

823.6错误地使用变量或信号 .................................................

823.5同一个信号在两个或两个以上的process中赋值 ...............................

813.4产生不必要的Latch ....................................................

803.3错误使用inout ........................................................

803.2采用std_logic以外的信号类型 ............................................

803.1.2采用时间相关语句

仿真语句 .......................................

803.1.1信号或变量赋初值 ..................................................

803.1不可综合的代码 ......................................................

79

3常见问题

..............................................................

782.2代码模块划分 ........................................................

782.1代码编写风格 ........................................................

78

2VHDL代码风格

.........................................................

78

1前言

..................................................................

78

第五章

VHDL数字电路设计指导

..............................................

77

8ALTERA参考设计准则

....................................................

76

7 时序设计的可靠性保障措施

................................................

72

6 全局信号的处理方法

.....................................................

71

5 时延电路处理

..........................................................

70

4SET和RESET信号处理

...................................................

693.4 不建议使用电路 ......................................................

593.3 异步设计中常见问题及其解决方法 ........................................

593.2 同步电路的设计规则 ..................................................

583.1同步电路的优越性 ....................................................

58

3同步电路设计

...........................................................

57

2 时序分析基础

..........................................................

57

1 设计可靠性

...........................................................

57

第四章同步电路设计技术及规则

...............................................

544.2ASIC设计如何考虑可靠性 ...............................................

524.1ASIC可靠性设计 ......................................................

52

4附录

..................................................................

523.4设计的规范性 ........................................................

523.3设计的可靠性 ........................................................

513.2.5设计验证

仿真测试方案 ...........................................

503.2.4具体电路设计

详细设计文档 .......................................

493.2.3确定关键电路时序和模块间接口时序

总体方案 .........................

493.2.2功能模块划分 .....................................................

493.2.1设计目标分析 .....................................................

493.2基本设计流程 ........................................................

483.1设计工程师基本素质要求 ...............................................

48

3可编程ASIC设计

........................................................

472.3根据市场需求和产品发展策略确定芯片开发策略 ..............................

472.2芯片设计发展趋势 ....................................................

462.1芯片设计类型 ........................................................

46

2芯片设计发展趋势

.......................................................

46

1引言

..................................................................

45

第三章

可编程ASIC设计方法简介

.............................................

446.2testbench编写示例 .....................................................

436.1Module 编写示例 ......................................................

43

6附录

..................................................................

绝密

请输入文档编号

2001-8-28 版权所有 侵权必究 第4页 共142页

1365.2不要直接使用数字 ...................................................

1365.1只使用IEEE的标准类 .................................................

136

5可移植性的编码准则

....................................................

1354.14 使用有意义的标号 ..................................................

1354.13 使用循环 LOOP和数组 .............................................

1354.12 使用函数 .........................................................

1354.11 VHDL Entity_Architecture和Configuration段

..............................

1354.10 端口映射和Generic映射 ..............................................

1344.9端口顺序 ..........................................................

1344.8不要使用HDL的保留字 ................................................

1344.7缩进 ..............................................................

1344.6行长度 ............................................................

1344.5独立成行 ..........................................................

1344.4使用注释 ..........................................................

1334.3源文件中要有文件头 ..................................................

1334.2VHDL中Architecture的命名约定 .........................................

1324.1命名定义 ..........................................................

132

4原则描述

.............................................................

132

3基本原则

.............................................................

132

2范围

.................................................................

132

1目的

.................................................................

132

第六章

代码可重用性设计

...................................................

1315.4.9元件的引用

CoreGen/LogiBLOX ...................................

1315.4.8实现边界扫描

JTAG 1149.1 .......................................

1305.4.7专用I/O译码器 ....................................................

1295.4.6存储器的实现 ....................................................

1285.4.5用三态Buffer实现多路选择器 .........................................

1265.4.4专用全局Set/Reset资源 ..............................................

1245.4.3全局时钟Buffer ...................................................

1215.4.2充分利用IOB资源 .................................................

1175.4.1组合逻辑合理划分

四输入特点 ....................................

1175.4高效利用CLB或IOB资源 ...............................................

1145.3桶形移位器

Barrel Shifter 的两种实现方式 ...............................

1095.2.4三种编码方式的VHDL实例 ..........................................

1095.2.3状态机的容错性 ..................................................

1085.2.2设计技巧 ........................................................

1075.2.1状态机编码 ......................................................

1075.2状态机编码及设计技巧 ................................................

1075.1Xilinx器件结构特点 ..................................................

107

5与工艺结构相关的设计技巧

以Xilinx为例

..................................

1054.9复制电路

减少扇出 fanout 提高设计速度 .............................

1044.8利用电路的等价性

巧妙地 分配 延时 ..................................

1014.7组合逻辑和时序逻辑分离 ..............................................

1004.6流水线

Pipelining .................................................

994.5.4综合工具与资源共享 ................................................

994.5.3子表达式共享 .....................................................

984.5.2loop语句 .........................................................

974.5.1if语句 ...........................................................

974.5资源共享 ...........................................................

954.4减少关键路径的逻辑级数 ...............................................

924.3IF语句和Case语句

速度与面积的关系 .....................................

924.2巧妙处理比较器 ......................................................

914.1.3改变操作数的位宽 ..................................................

914.1.2使用圆括号处理多个加法器 ...........................................

894.1.1串行进位与超前进位

................................................

绝密

请输入文档编号

2001-8-28 版权所有 侵权必究 第5页 共142页