2010 Microchip Technology Inc. 初稿 DS41302C_CN

PIC12F609/615/617

PIC12HV609/615

数据手册

8 引脚 8 位

CMOS 闪存单片机

*8 位 8 引脚器件受 Microchip 的低引脚数专利 (美国专利号 5,847,450)保护。其他美国及外国的专利和应用可能已发

布或正在等待批准。

DS41302C_CN 第 2 页 初稿 2010 Microchip Technology Inc.

提供本文档的中文版本仅为了便于理解。请勿忽视文档中包含

的英文部分,因为其中提供了有关 Microchip 产品性能和使用

情况的有用信息。Microchip Technology Inc. 及其分公司和相

关公司、各级主管与员工及事务代理机构对译文中可能存在的

任何差错不承担任何责任。建议参考 Microchip Technology

Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。如果将 Microchip 器件用于生命

维持和 / 或生命安全应用,一切风险由买方自负。买方同意在

由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障

Microchip 免于承担法律责任,并加以赔偿。在 Microchip 知识

产权保护下,不得暗中或以其他方式转让任何许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 dsPIC、

K

EELOQ、 KEELOQ 徽标、 MPLAB、 PIC、 PICmicro、

PICSTART、 PIC

32

徽标、 rfPIC 和 UNI/O 均为 Microchip

Technology Inc. 在美国和其他国家或地区的注册商标。

FilterLab、 Hampshire、 HI-TECH C、 Linear Active

Thermistor、MXDEV、MXLAB、SEEVAL 和 The Embedded

Control Solutions Company 均为 Microchip Technology Inc.

在美国的注册商标。

Analog-for-the-Digital Age、 Application Maestro、

CodeGuard、 dsPICDEM、 dsPICDEM.net、 dsPICworks、

dsSPEAK、 ECAN、 ECONOMONITOR、 FanSense、

HI-TIDE、 In-Circuit Serial Programming、 ICSP、 Mindi、

MiWi、MPASM、MPLAB Certified 徽标、MPLIB、MPLINK、

mTouch、 Octopus、 Omniscient Code Generation、 PICC、

PICC-18、PICDEM、PICDEM.net、PICkit、PICtail、REAL

ICE、 rfLAB、 Select Mode、 Total Endurance、 TSHARC、

UniWinDriver、 WiperLock 和 ZENA 均为 M

icrochip

Technology Inc. 在美国和其他国家或地区的商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2010, Microchip Technology Inc. 版权所有。

ISBN: 978-1-60932-090-4

请注意以下有关 Microchip 器件代码保护功能的要点:

•Microchip的产品均达到 Microchip 数据手册中所述的技术指标。

•Microchip确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的

操作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

•Microchip愿与那些注重代码完整性的客户合作。

•Microchip或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了 《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的

软件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

Microchip

位于美国亚利桑那州

Chandler

和

Tempe

与位于俄勒冈州

Gresham

的全球总部、设计和晶圆生产厂及位于美国加利福尼亚州和

印度的设计中心均通过了

ISO/TS-16949:2002

认证。公司在

PIC

®

MCU

与

dsPIC

®

DSC

、

KEELOQ

®

跳码器件、串行

EEPROM

、单片机外

设、非易失性存储器和模拟产品方面的质量体系流程均符合

ISO/TS-

16949:2002

。此外,

Microchip

在开发系统的设计和生产方面的质量体

系也已通过了

ISO 9001:2000

认证。

2010 Microchip Technology Inc. 初稿 DS41302C_CN 第 3 页

PIC12F609/615/617/12HV609/615

高性能 RISC CPU:

• 仅需学习 35 条指令:

- 除了跳转指令以外,所有指令都是单周期的

• 工作速度:

-DC- 20 MHz 振荡器 / 时钟输入

-DC- 200 ns 指令周期

• 中断能力

• 8 级深硬件堆栈

• 直接、间接和相对寻址模式

单片机特性:

• 精确的内部振荡器:

- 出厂时精度已校准到 ±1%,典型值

- 可软件选择频率范围:4MHz或 8 MHz

• 节能休眠模式

• 电压范围:

- PIC12F609/615/617:2.0V 至 5.5V

- PIC12HV609/615:2.0V 到用户定义的最大

值 (见 “注”)

• 工业级和扩展级温度范围

• 上电复位 (Power-on Reset, POR)

• 上电延时定时器(Power-up Timer,PWRT)和振

荡器起振定时器(Oscillator Start-up Timer,OST)

• 欠压复位 (Brown-out Reset, BOR)

• 带独立振荡器的看门狗定时器(Watchdog Timer,

WDT)有利于可靠地工作

• 带上拉的主复位引脚,与输入功能复用

• 可编程代码保护

• 高耐用性闪存:

- 闪存耐写次数达 100,000 次

- 闪存数据保存时间:> 40 年

• 自读 / 写程序存储器 (仅限 PIC12F617)

低功耗特性:

• 待机电流:

-2.0V时典型值为 50 nA

• 工作电流:

-32kHz、 2.0V 时典型值为 11 μA

-4MHz、 2.0V 时典型值为 260 μA

• 看门狗定时器电流:

-2.0V时典型值为 1 μA

注: 并联稳压器两端的电压不应超过 5V。

外设特性:

• 并联稳压器 (仅限 PIC12HV609/615):

-5V稳压

-4mA到 50 mA 并联电流范围

• 5 个 I/O 引脚和 1 个只用作输入的引脚

• 高灌 / 拉电流能力,可直接驱动 LED

- 引脚电平变化中断或

- 引脚可单独编程的弱上拉

• 模拟比较器模块,具有:

-1个模拟比较器

- 片上可编程参考电压(CV

REF)模块(VDD的%)

- 可从外部访问比较器输入和输出

- 内置滞后 (软件可选择)

• Timer0:带有 8 位可编程预分频器的 8 位定时器 /

计数器

• 增强型 Timer1:

- 带有预分频器的 16 位定时器 / 计数器

- 外部 Timer1 门控 (计数使能)

- 如果选用 INTOSC 模式,可选择连接在 OSC1

和 OSC2 之间的振荡器 (工作在 LP 模式下)

作为 Timer1 的振荡器

- 可选择系统时钟作为 Timer1 的振荡器

• 通过两个引脚进行在线串行编程 (In-Circuit Serial

Programming

TM

, ICSP

TM

)

仅限 PIC12F615/617/HV615:

• 增强型捕捉 / 比较 /PWM 模块:

-16位捕捉,最大分辨率 12.5 ns

- 比较,最大分辨率 200 ns

-10位 PWM,带有 1 或 2 路输出通道,1 路输

出通道可编程“死区”,最高频率 20 kHz,自

动关闭

• A/D 转换器:

-10位分辨率和 4 路通道,采样内部参考电压

• Timer2:带有 8 位周期寄存器、预分频器和后分频

器的 8 位定时器 / 计数器

8 引脚 8 位 CMOS 闪存单片机

PIC12F609/615/617/12HV609/615

DS41302C_CN 第 4 页 初稿 2010 Microchip Technology Inc.

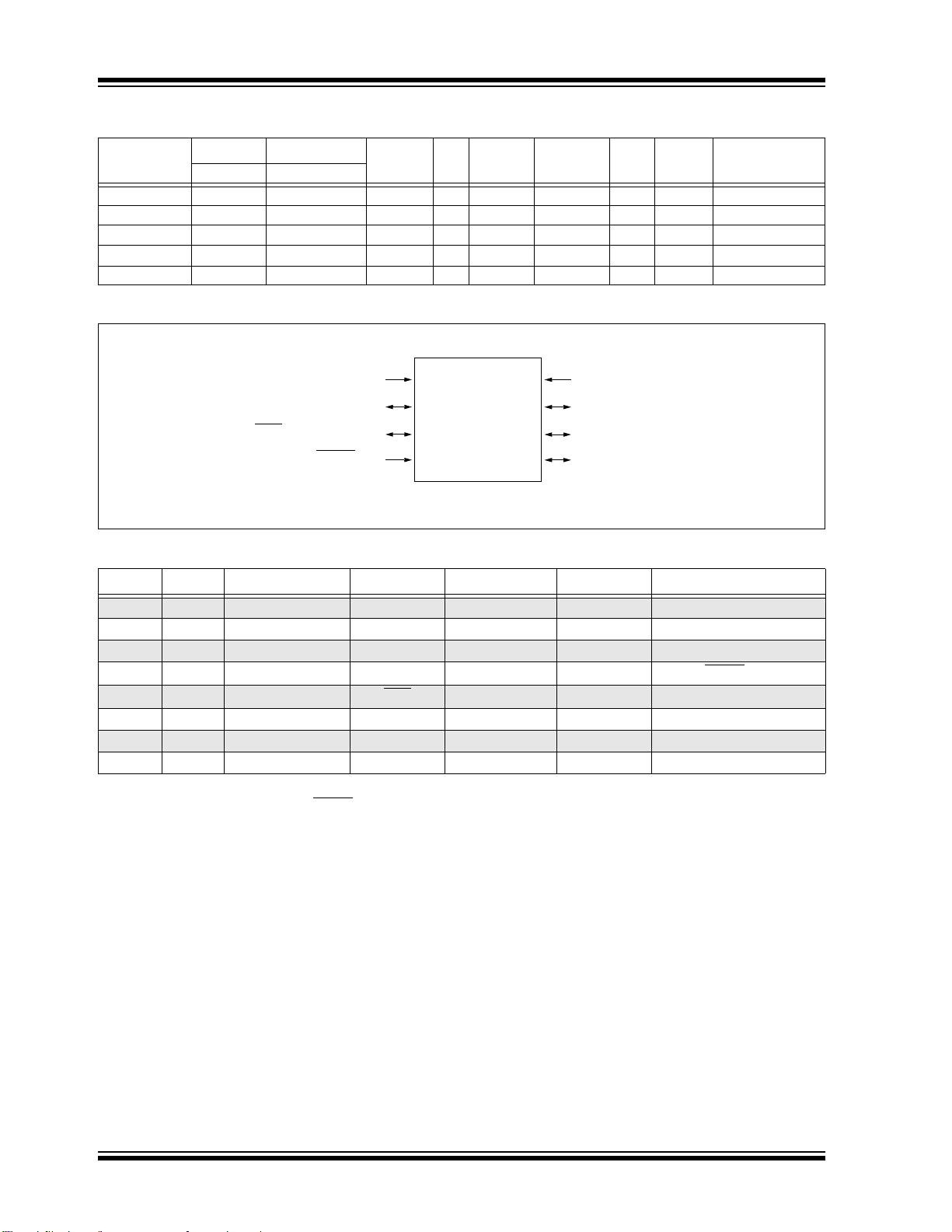

8 引脚图, PIC12F609/HV609 (PDIP、 SOIC、 MSOP 和 DFN)

表 1: PIC12F609/HV609 引脚汇总 (PDIP、 SOIC、 MSOP 和 DFN)

器件

程序存储器 数据存储器

自读 / 自写

I/O

10 位 A/D

(通道)

比较器

ECCP

8/16 位

定时器

电压范围

闪存 (字) SRAM (字节)

PIC12F609 1024 64

—

50 1

—

1/1 2.0V-5.5V

PIC12HV609 1024 64

—

50 1

—

1/1

2.0V- 用户定义

PIC12F615 1024 64

—

54 1

有

2/1 2.0V-5.5V

PIC12HV615 1024 64

—

54 1

有

2/1

2.0V- 用户定义

PIC12F617 2048 128

有

54 1

有

2/1 2.0V-5.5V

I/O

引脚 比较器 定时器 中断 上拉 基本功能

GP0 7 CIN+ — IOC

有

ICSPDAT

GP1 6 CIN0- — IOC

有

ICSPCLK

GP2 5 COUT T0CKI INT/IOC

有

—

GP3

(1)

4—

—

IOC

有

(2)

MCLR/VPP

GP4 3 CIN1- T1G IOC

有

OSC2/CLKOUT

GP5 2 — T1CKI IOC

有

OSC1/CLKIN

— 1 — — — — VDD

—8— ——— VSS

注 1: 仅用作输入。

2: 仅当引脚被配置为外部 MCLR

时。

1

2

3

4

5

6

7

8

PIC12F609/

HV609

V

SS

GP0/CIN+/ICSPDAT

GP1/CIN0-/ICSPCLK

GP2/T0CKI/INT/COUT

VDD

GP5/T1CKI/OSC1/CLKIN

GP4/CIN1-/T1G

/OSC2/CLKOUT

GP3/MCLR

/VPP

2010 Microchip Technology Inc. 初稿 DS41302C_CN 第 5 页

PIC12F609/615/617/12HV609/615

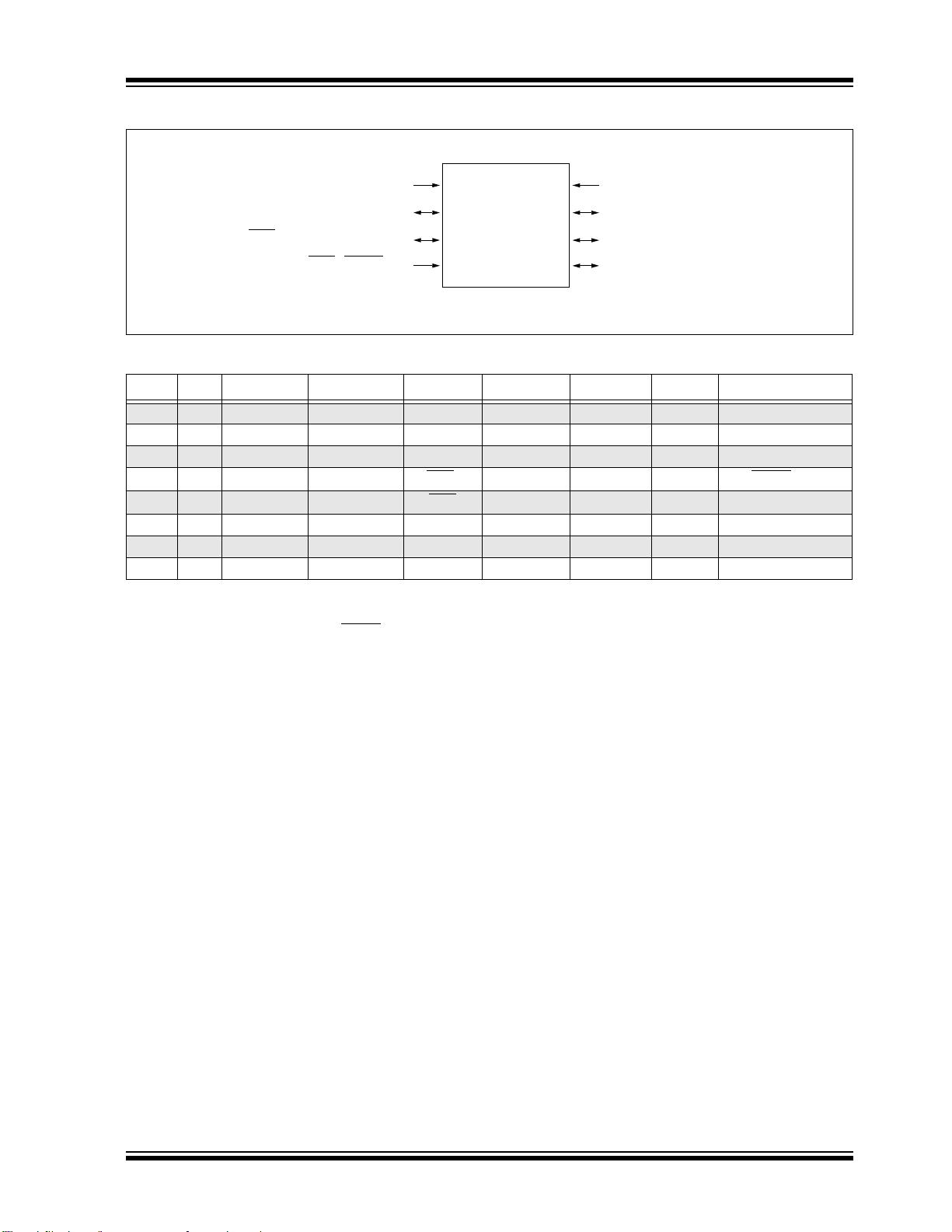

8 引脚图, PIC12F615/617/HV615 (PDIP、 SOIC、 MSOP 和 DFN)

表 2: PIC12F615/617/HV615 引脚汇总 (PDIP、 SOIC、 MSOP 和 DFN)

I/O

引脚 模拟 比较器 定时器

CCP

中断 上拉 基本功能

GP0 7 AN0 CIN+ — P1B IOC

有

ICSPDAT

GP1 6 AN1 CIN0- — — IOC

有

ICSPCLK/V

REF

GP2 5 AN2 COUT T0CKI CCP1/P1A INT/IOC

有

—

GP3

(1)

4— — T1G*— IOC

有

(2)

MCLR/VPP

GP4 3 AN3 CIN1- T1G P1B* IOC

有

OSC2/CLKOUT

GP5 2 — — T1CKI P1A* IOC

有

OSC1/CLKIN

— 1 — — — — — — VDD

—8 — — — — — — VSS

* 备用引脚功能。

注 1: 仅用作输入。

2: 仅当引脚被配置为外部 MCLR

时。

1

2

3

4

5

6

7

8

PIC12F615/

617/HV615

V

SS

GP0/AN0/CIN+/P1B/ICSPDAT

GP1/AN1/CIN0-/V

REF/ICSPCLK

GP2/AN2/T0CKI/INT/COUT/CCP1/P1A

VDD

GP5/T1CKI/P1A*/OSC1/CLKIN

GP4/AN3/CIN1-/T1G

/P1B*/OSC2/CLKOUT

GP3/T1G

*/MCLR/VPP

* 备用引脚功能。